# Hadron Universal Logic module User Guide

2023.08.19

Ryotaro Honda

Open-It HUL project

| able of contents                               |    |

|------------------------------------------------|----|

|                                                |    |

| 1. Introduction                                |    |

| 1.1 Update history                             |    |

| 1.2 Module overview                            |    |

| 2. Hardware                                    |    |

| 2.1 HUL controller module                      |    |

| 2.2 HUL Mezzanine cards                        |    |

| 3. SiTCP                                       | 1  |

| 3.1 MAC and IP address setting                 | 1  |

| 4. Firmware                                    | 1  |

| 4.1 Version.1 and Version. 3 series            |    |

| 4.2 Basic structure of HUL firmware            |    |

| 4.3 Commons to all HUL firmware                | 1  |

| 4.4 HUL Skeleton                               |    |

| 4.5 HUL RM                                     | 2  |

| 4.6 HUL Scaler                                 | 3  |

| 4.7 HUL MH-TDC                                 | 3  |

| 4.8 Mezzanine HR-TDC and HUL HR-TDC BASE       | 4  |

| 4.9 Three-dimensional matrix trigger           | 6  |

| 4.10 Mass trigger (TOF based trigger)          | 6  |

| 4.11 Streaming TDC                             | 7  |

| 5. For developers                              | 8  |

| 5.1 Vivado project to be used                  | 8  |

| 5.2 Structure of HUL firmware                  | 8  |

| 5. Software                                    | ç  |

| 6.1 Source files                               | ç  |

| 6.2 Programs for each FW                       | Ç  |

| 7. Practical Usage                             | ç  |

| 7.1 Generation and download of MCS with Vivado | Ç  |

| 7.2 MCS download via SiCPT by FMP              | (  |

| 7.3 A few How-to's in usage                    | ç  |

| 7.4 Miscellaneous                              | 1( |

# 1. Introduction

# 1.1 Update history

### 2017.12.19

- In Chapter 2, added a section about Mezzanine DTL.

- In Chapter 2, added a section about Mezzanine HR-TDC.

- Consistent behavior of the reset sequence in the existing firmware (described in Chapter 4).

- Explicitly stated that 100 Mbps ethernet communication is not supported in the exisiting firmware.

- Added a bit in the data header of the existing firmware showing that HRM exists (described in Chapter 4).

- $\bullet$  Stability improvement of HUL MH-TDC in high rates. Increased the event word size to 12 bits. Confirmed no event slips up to  $10^9$  events.

- Added HR-TDC section in Chapter 4.

- Added a few practical use in Chapter 7.

- Description about the board with SPI flash chip changed to MT25QL512.

- Description of simple tests.

- Description of how to use multiple HUL in a VME crate.

- Usage of HR-TDC.

- Modification to sitcp\_controller.cc in controlling C++ software package. Sleep configulation in Reset\_SiTCP.

- Removed gzfilter.hh from the controlling C++ software package, because it is strongly dependent to the gcc version. Removed data compression option.

### 2018.2.2

- Resolved an issue of returning a wrong event ID by +1 when event-tag is received from JO bus by HRM, Scaler, MH-TDC and HRTDC\_BASE, relative to the module with HRM installed.

- Resolved an issue of data returning out of the search window range from Mezzanine HR-TDC and MH-TDC.

- Resolved an issue of Local bus hang in case of BCT::Reset in HR-TDC\_BASE.

- Described in Chapter 7 the issue that no triger could be received in the JO slave modules after a module reset in case of Level2 trigger in JO on a VME crate (not resolved).

- In Chapter 7, described the case where an event slip has occured.

### 2018.8.22

- In Chapter 7, described a board which has SPI flash upgraded to S25FL256SAGNFI001.

- In Chapter 7, described the handling necessary in the original SPI flash memory, N25Q128A

### 2021.11.10

- Firmware is major updated to version 3.

- Major updates of the descriptions in the User Guide

| 2022.0 | 1.13                                                                                          |

|--------|-----------------------------------------------------------------------------------------------|

| •      | Release the English version user guide.                                                       |

| 022.0  | 3.18                                                                                          |

| •      | Correct the description of the mezzanine HR-TDC sub-header structure.                         |

| 023.0  | 1.17                                                                                          |

| •      | Released Mezzanine HR-TDC v5.0 and HUL HRTDC BASE v4.0. Updated description of what changed.  |

| •      | Removed MifFunc.cc from software. Introduced BctBusBridge.cc instead.                         |

| •      | Fixed a bug that the self-busy length of HUL HRTDC BASE is short and there is a valley in the |

|        | busy signal.                                                                                  |

| 2023.0 | 2.24                                                                                          |

• Released HUL HRTDC BASE v4.1. The bug-fixed version of v4.0, which does not work correctly.

### 2023.08.19

$\bullet$  Fixed incorrect description of Mezzanine HR-TDC clock frequency.

# 1.2 Module overview

Hadron Universal Logic (HUL) module has been developed as an upgrade from Tohoku Universal Logic (TUL) which was used in Hadron Hall experiments, J-PARC. The controlling field programmable gate array (FPGA) is upgraded to Xilinx Kintex 7, enabling more complicated logic conditions run in a higher speed. HUL has two fixed input connectors and two mezzanine slots the latter of which enable extensions to various experimental needs by installing mezzanine cards. These two connectors and slots are connected to FPGA by 64 (32x2) fixed input lines and 64 (32x2) pair differential lines, respectively, enabling handling of 128 channel maximum inputs. The 64 pair differential lines are directly connected to the mezzanine base connectors, so that input/output is programmable to the mezzanine cards. HUL is equipped with the data communication ethernet interface (GbE) and the trigger input/output busline (KEK-VME JO) which TUL did not have. Communication to the data-taking PC employs UDP and TCP protocols supplied by the SiTCP technology, which is a FPGA-based hardware implimentation of TCP/IP, supporting 1Gbps TCP communication via an ethernet cable (Cat.5 and above). UDP communication is extended by remote-bus control protocol (RBCP) of SiTCP, which supports the addressed access to the memory region of HUL in slow-controls. KEK-VME JO bus is 8 pairs of triggering bus in M-LVDS signal levels. It consists of 7 pairs of transmission lines and one pair of output (BUSY). HUL may act as the bus controller or the slave receiver of the JO bus. HUL is developped in an Open-It project "Hadron Universal Logic Module", employing the technological developments achieved in the Open-It consourtium. The interectual property and its usage is subject to the terms of the Open-It consourtium. Open-It

# 2. Hardware

# 2.1 HUL controller module

Hadron Universal Logic (HUL) controller module is VME 6U size printed circuit board, and is called simply as HUL hereafter. The catalog number in GND Ltd. is: **GND catalog number (ジーエヌディー管理番 号) GN-1573-1**

# 2.1.1 Detailed Specifications

```

• Input ports

```

- 64 pairs of differential inputs (KEL 8831E connector)

- Supports LVDS, ECL, PECL, LVPECL etc.

- 4 ports of NIM inputs

- Output ports

- 4 ports of NIM outputs

- Mezzanine slots

- 2 slots

- $\circ$  Directly connected to FPGA via duplex LVDS 32 pairs

- $\circ$  Power suppy to Mezzanine board: +3.3 V from HUL

- Communication interface

- RJ45: GbE (1000BASE-T)

- VME J1 is not supported

- FPGA

- Xilinx Kintex7 (XC7K160T-1FBG676C)

- Configuration memory chips

- SPI flash in 3.3V (one of the followings depending on the manufacture date)

- N25Q128A13EF840E

- MT25QL512ABB1EW9-OSIT

- S25FL256SAGNF1001

- $\,\circ\,$  SPI (synchronous serial interface) in serial configuration mode

- Clock source

- 50 MHz LVCMOS (~50 ppm)

- Peak-To-Peak jitter 30ps

- Trigger bus

- KEK-VME JO

- HUL may be configured as a bus driver or a receiver

- Power supply

- $\circ$  DC +5V

- supplied from a AC/DC adapter, or the VME-J1 connector

- Power consumption

- static: 0.5~0.7 W @3.3 V (mainly at ethernet PHY) and 0.5~0.7 W @1.0 V (mainly at FPGA)

- $\circ$  dynamic: strongly depends on the FPGA firmware

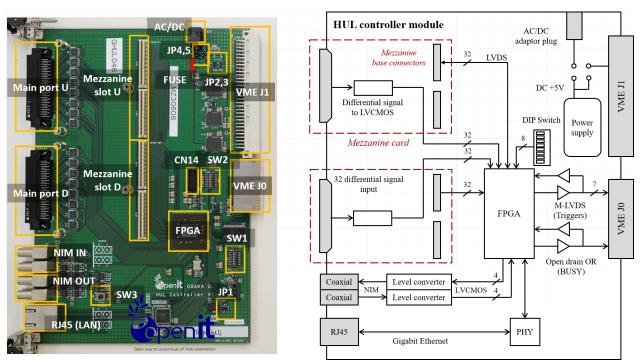

A picture of HUL and block diagram are shown below

Figure 1: Photo and block diagram of HUL controller.

### Main port U (D)

Fixed input ports in the front. The connector is the half-pitch 68 poles (KEL 8831E-068-170L-F). A cable with the compatible connector is supposed to be manufactured. Channel assignment is 0-31 for U and 32-63 for D, with lower number in the marker side. The signal grounds are A1A2 and B1B2 pairs, right below the marker. The inputs support differential signals in LVDS, ECL, PECL and LVPECL levels with the common mode voltage in the -4 V  $\sim$  +5 V range. When feeding an emitter-follower type signal levels, such as ECL, the signal current must be controlled in the driver side. There is no register for the current control in the HUL side.

The fixed input ports converts the differential signals to LVCMOS before feeding to FPGA. This limits the maximum repetation speed to 560 Mbps. If the signal rate is higher than that, consider using a mezzanine card. For an application to wire chambers, where Amp Shaper Discriminator (ASD) outputs are fed into HUL, the repetition rate limit is not a problem.

### NIM IN

4 intputs of NIM level. Channel assignments are written on the board. Channel number starts with 1

### NIM OUT

4 outputs in NIM level. Channel assignments are written on the board. Channel number starts with 1

### Ethernet connection (LAN)

RJ45 type ethernet connector. Gigabit Ethernet PHY chip is connected. Used for PC-FPGA communication via SiTCP.

### Mezzanine slot U(D)

Slots to install mezannine cards. HUL has two of 64 pole connectors MOLEX-071439-0464 for one card. The upper connector has the signals and the lower has the power supply and the ground. Mezzanine cards may employ a few models of connectors with different heights, but if MOLEX-071436-1464 is employed, the card will be supported by three of 9 mm stand + 0.5 mm washer sets.

The signals are 32 pairs of differential lines to FPGA. There is no component to determine the signal direction between mezzanine connectors to FPGA, so that duplex LVDS may be adopted for the signal levels. The design of the mezzanine card and the FPGA firmware determine the actual signal levels and directions. If inputs are assigned to Slot U and D, the channel numbers will be 64-95 and 96-127 respectively, with the offset (0-31 and 32-63) from the main ports of the board. Some of the polarities p/n are reversed between the mezzanine connectors to FPGA owing to the simplicity of

the pattern layout. The VHDL source MZN\_NetAssign.vhd takes care of the polarities of the differential signals by inserting logical inverters (NOTs) to the signals.

Mezzanine slots supply +3.3 V to the card. The current allowance will be 4-5 Amps (13-16 W) to the card, with the 6 Amps supplied from the power and 1-2 Amps consumed by HUL itself.

### CN14

Connector for JTAG protocol. PC may download the FPGA firmware via USB-JTAG downloader by Xilinx. How to download bitstream or MCS are described more in detail in Chapter 7.

### SW1

The switch which defines whether HUL is a VME JO bus driver or a receiver. SW1-8 must be all OFF to be a receiver (default). SW1-8 must be all ON to be a driver. Do not define more than one driver in a VME crate, as such situation will short circuit the bus line and causes a damage.

### SW2

User defined dip switch. The role is defined in FPGA firmware.

### SW3

User defined push switch. It generates a pulse to send to FPGA. In the exisitng firmware, it causes the highest reset action. The pulse logic is negative, changing from 1 to 0 if pressed.

### JP1

Reserved. Keep it open.

### JP2, 3

Close to take power from VME J1. DC +5V as the supply.

### JP4, 5

Close to take power from a AC/DC adapter.

### AC/DC

Standard socket for a DC power input (OD 5.5 mm, ID 2.1 mm, center plus).

### FUSE

5 Amps fuse. Compatible to a standard fuse, such as PICO® fuse by Littelfuse.

### VME J1

Connector to a VME crate. Only the power supply (+5V) is connected.

### VME J0

Connector to KEK-VME JO bus. There is no connection to the power supply on JO bus. **Equipped as a default, but is an optional.** Order the board without CN9 to remove this connector.

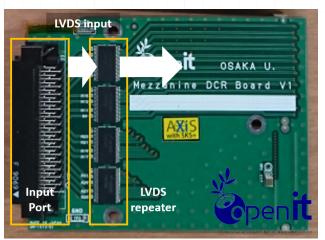

# 2.2 HUL Mezzanine cards 2.2.1 HUL Mezzanine Drift Chamber Receiver (DCR) Ver.1

Drift Chamber Receiver (DCR) Ver.1 is the input repeater circuit board for the Amp Shaper Discriminator (ASD) card designed for drift chambers (GND catalog number: GNA200). It repeats 32 channels of signal from GNA200 into LVDS levels, so that HUL can read. Ver.1 keeps the differential characteristics to FPGA with a higher timing resolution, it is superior to the Ver.2 or the HUL main input ports. However, these advantages are subtle, and Ver.2 is upper conpatible with more kinds of supported signal levels. GND catalog number (ジーエヌディー管理番号): GN-1573-S1

Figure 2: mezzanine DCR v1

### Input Port

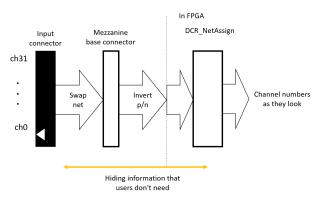

LVDS input ports. The connector is a half-pitch 68 pole (KEL 8831E-068-170L-F). A compatible connector must be used with cables. The marker side is lower in the channel number, as in the HUL on-board inputs. The grounds are A1A2 and B1B2 pair, directory below the marker. Due to the simplicity of the board pattern, DCR ver.1 and ver.2 both have a swapping of the channel numbers and polarity p/n. The VHDL source DCR\_NetAssign.vhd takes care of the channel / polarity order to be correct, as shown in the figure below.

Figure 3: DCR has net swaps and corrections

### LVDS repeater

Receives LVDS signals and repeats to FPGA. These ICs protect FPGA from unintentinal signal disturbances, such as discharges.

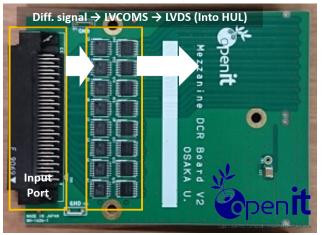

# 2.2.2 HUL Mezzanine Drift Chamber Receiver (DCR) Ver.2

Drift Chamber Receiver (DCR) Ver.2 has the same role with ver.1, but employs the same differential receiver ICs with those used in HUL on-board main input ports. This enables acceptance of various levels of differential signals (LVDS, ECL, PECL, LVPECL etc) as for the HUL on-board inputs. For the purpose of input ports extention, ver.2 is recommended. GND catalog number (ジーエヌディー管理番号): GN-1626-1

Figure 4: mezzanine DCR v2

### Input Port

Mechanically the same with DCR Ver.1. Supports differential signals with the common mode voltages ranging from -4 V to +5 V. The differential signal is converted to LVCMOS (as in the on-board input ports) and subsequently converted to LVDS to feed to FPGA. The VHDL code DCR\_NetAssign.vhd takes care of the channel and polarity p/n swaps as in ver. 1.

### 2.2.3 HUL Receiver Module (HRM)

HUL Receiver Module (HRM) receives the trigger signals and event numbers distributed from Master Triger Module (MTM: GNN-570) employed in J-PARC Hadron Hall experiments, and returns BUSY signals back to MTM. HRM de-serializes the trigger signals and event numbers transmitted through the Category 5e twist-pair cables, and converts to a bus signal format to FPGA. In return, HRM serializes the BUSY and RSV2 signals from FPGA to be transmitted to MTM. The trigger signals to and BUSY signals from HRM are all processed in the FPGA on HUL, enabling the HUL to function as a J0 bus controller of KEK-VME crates. **GND catalog number** ( $\Im - I \Im = 1$ , GN-1627-1

Page 9

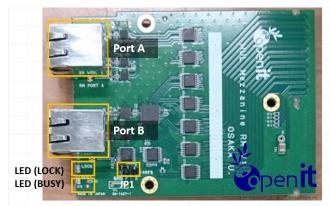

Figure 5: HUL receiver module (HRM)

### Port A

Trigger inpurt port A. Should be connected with a twist pair cable to MTM port A or repeater port A.

### Port B

Trigger input port B. Should be connected with a twist pair cable to MTM port B or repeater port B.

### LED (LOCK)

Lights green if the event tag bit from Port B is correctly decoded, and the PLL lock of the clock is high.

### LED (BUSY)

Lights red if the BUSY to MTM is high. However, HRM reflects only the BUSY status from FPGA, which should be independently checked if it correctly reflect the the create bus BUSY signals.

### JP1

Controls RRFB, meaning whether the de-serialized event tag outputs synchlonize to RCLK clock rising edge (R) or falling edge (F). Default is R. This is a 3-pins pin header. Short the R side.

| Signal           | Direct | on Description                                                                                     |

|------------------|--------|----------------------------------------------------------------------------------------------------|

| RCLK             | IN     | Clock decoded from the event tag from port B                                                       |

| LEVEL1           | IN     | Levell trigger signal                                                                              |

| LEVEL2           | IN     | Level2 trigger signal                                                                              |

| Clear            | IN     | Fast clear signal                                                                                  |

| RSV1             | IN     | Reserve 1 signal from MTM                                                                          |

| LOCK             | IN     | Lock bit of PLL, showing that the clock is correctly decoded.                                      |

| SNINC            | IN     | Spill Number Increment. FPGA may count the spill numbers.                                          |

| Event<br>counter | IN     | 12 bit event number from MTM                                                                       |

| Spill<br>counter | IN     | 8 bit spill number from MTM                                                                        |

| RRFB             | OUT    | Timing for decoded tag information. High for rising edge (R) and Low for falling edge (F) of RCLK. |

| BUSY             | OUT    | BUSY signal to MTM                                                                                 |

| RSV2             | OUT    | Reserve 2 signal to MTM                                                                            |

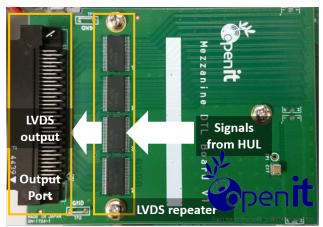

# 2.2.4 HUL Mezzanine differential signal transmitter LVDS (DTL)

Mezzanine DTL is a LVDS output buffer from HUL-FPGA to other devices. The circuit is the same with DCRv1, except the input/output directions of the LVDS repeaters. The channel assignment is the same with DCRv1. HUL-FPGA must output LVDS signal to drive this card. **GND catalog number (ジーエヌディー管** 理番号): **GN-1724-1**

Figure 6: Mezzanine DTL

### Output Port

LVDS output ports. The mechanical specification, signal and ground assignments are the same with DCR v1. This mezzanine card requires to use the VHDL source DCR\_NetAssign.vhd, but the input/output direction is opposite from the case in DCRv1.

Page 11

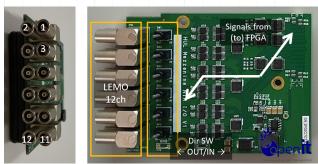

# 2.2.5 HUL Mezzanine NIM extension (NIM-Ex)

Mezzanine NIM-Ex extends the NIM inputs/outputs of HUL. It has 12 LEMO connectors grouped in 6 pairs which are independently selected for inputs or outputs by switch settings. The same IC is employed as used in HUL NIM IO ports, and the speed is the same.

NIM-Ex card consumes 5.5W, being rather large. The card generates -3.3 V on-board and may become hot. Air cooling fan is strongly recommended. Otherwise, the mezzanine card may break by the self-heating. There are numerous mistakes on the circuit diagrams. An example design is included in the skeleton project of mezzanine board, because the errorous circuit net prevents a guess of correct XDC and HDL code.

Figure 7: Mezzanine NIM-Ex

### LEMO

12 channel LEMO connectors. Example sckeleton design includes NimEx\_NetAssign.vhd, which has the net number associated to the physical channels as <u>figure above</u>.

### Dir SW

Signal direction in groups of 2 channels. Defined for OUTPUTs if the switch is toward the LEMO connector; defined INPUTS if otherwise.

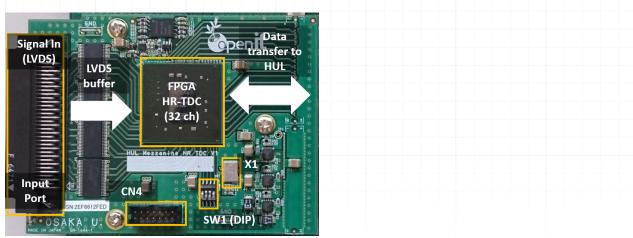

# 2.2.6 HUL Mezzanine High-resolution TDC

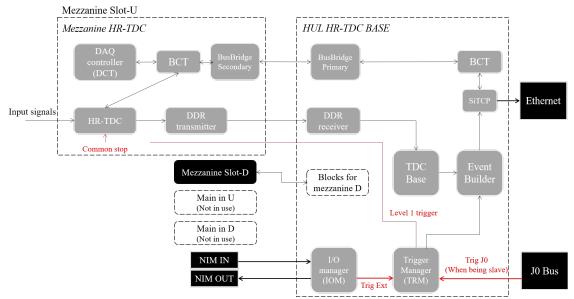

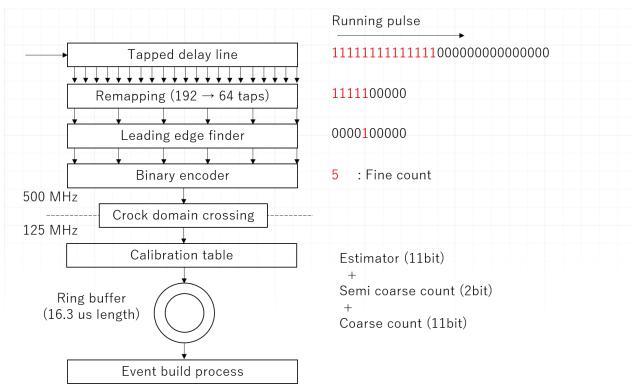

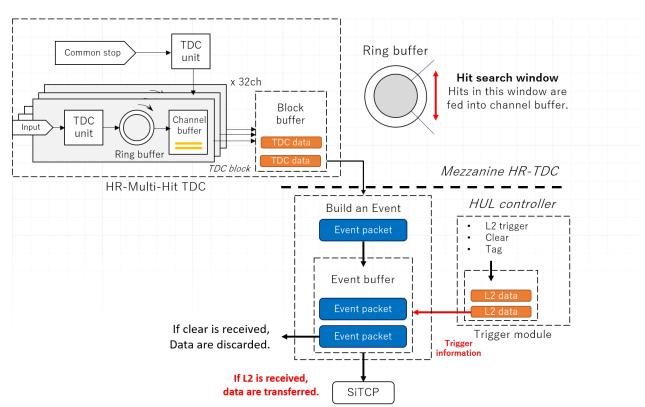

Mezzanine HR-TDC is capable of measuring time difference in ~30 ps resolution in common stop and multihit mode. It has a dedicated FPGA for the time measurement on the mezzanine card, and requires controls and data transfer operations from HUL. The function of the mezzanine is to measure time, to form data in a pre-fixed format and transfer the data to FPGA on HUL by the trigger input. Depending on the firmware of FPGA on HUL, this mezzanine is able to act as a simple TDC or play a more complicated role such as Time of Flight (TOF) trigger. Detailed action and control is described in Chapter 4.

The FPGA on this mezzanine card is Kintex-7 160T-1, the same chip as used on HUL. One mezzanine takes 32 channels of timing signals, capable to measure both the leading and trailing edges. The sinal input level is exclusively LVDS, not supporting ECL. The clock for FPGA is selectable either from the quartz on the mezzanine or from HUL. The power is +3.3 V taken from HUL, and other voltages are generated on the mezzanine card via low drop-out (LDO) regulators. The power consumption is 5 W / card, which is rather high. If the +3.3 V power supply chip on HUL is LMZ30604RKGT (max. 4 Amps), it is insufficient to drive two mezzanine cards. In such cases, make sure the chip on HUL is LMZ30606RKGT (max. 6 Amps). The power consuption of the entire board will become almost 20 W when two HR-TDC mezzanine boards are installed. Make sure that the board is well cooled by a fan. If the cooling of the FPGAs is

not sufficient, they became unstable with progressively increased leak currents. It is strongly recommended that a VME crate with a fan is used. (Also, stable ground is necessary to reach to the high timing resolution.) **GND catalog number (ジーエヌディー管理番号): GN-1644-1**

Figure 8: Mezzanine HR-TDC

### Input Port

Signal inputs which supports only LVDS levels. Connector is a half-pitch 68 pole (KEL 8831E-068-170L-F). The ground is assigned on A1A2 and B1B2, right below the marker. Channel assignment is 0-31 from the marker. There is no swap of the channels.

### CN4

JTAG connector for firmware download. FPGA and SPI flash memory may be accessed. The SPI flash memory chp is N25Q128A11EF840E or MT25QU256ABA1EW9-OSIT with 1.8V power inputs. Please configure / identify the chip correctly when downloading MCS onto the SPI chip.

### SW1

Dip switch to control the FPGA of the mezzanine card. The current firmware selects the clock source from the quartz on the mezzanine card or from the HUL.

### X1

100 MHz quartz oscillator. The frequency must be the same if HUL clock is used.

### SPI flash memory chip version

Mezzanine HR-TDC has two versions for the flash memory chip, depending on the date of the manufacture. To correctly identify the flash memory chip, Vivado (the FPGA tool on PC) is required. It is safer to mark the SPI flash memory chip version with a note on the board.

- N25Q128A11EF840E (pre 2020 manufacture)

- MT25QU256ABA1EW9-0SIT (since 2020)

# 3. SiTCP

SiTCP is a hardware implementation of TCP/IP network communication protocol, developed by Tomohisa Uchida at KEK. It enables the communication without an involvement of a CPU. Please refer to Uchida's and BBT's web sites for detailed usage and the most recent IP core (the component to be linked when developing a firmware). \* <u>Uchida's web site</u> \* <u>BBT's web site</u>

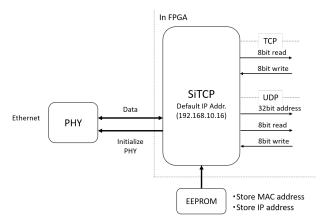

SiTCP block diagram is shown in a figure below. SiTCP initializes the ethernet communication PHY and loads MAC and IP addresses from EEPROM. In the forced default mode, the MAC and IP addresses are set to the default (192.168.10.16). The forced default mode does not allow other SiTCP hardware in the same forced default mode to exist in the same network, usually used in the 1 to 1 connection to the PC for testing. SiTCP provides TCP and UDP communication protocols to FPGA. SiTCP supports both the 100 Mbps and 1Gbps modes automatically switched by the signal from PHY; however, the existing firmware for HUL only supports the lGbps mode. TCP generally transmits or receives data in the 8 bit units synchlonized with the system clock; however, the TCP receive action (data from PC to hardware in TCP) is not recommended in SiTCP. The registers on the hardware are accessed via UDP. A unique packet called RBCP is used in the UDP for control command transmission, address setting and data transmission and receiving. RBCP returns UDP acknowledge for handshaking between the PC and SiTCP. UDP transmits 32 bit address and transmits/receives data in 8 bits synchlonized with the system clock. SiTCP internal registers and the EEPROM are also addressed and may be accessed via UDP, however do not touch them unless really necessary. The IP and MAC address are stored in EEPROM and loaded to SiTCP registers, which may be accessed by the BBT software (SiTCP tools) or specifying the UDP address in a user program.

SiTCP does not "keep alive" the connection by default. This causes a session closure in case of very low trigger rate (~1 trigger / 30 min). To avoide such situation, regularly send a keep alive packet.

Figure 1: SiTCP block diagram

# 3.1 MAC and IP address setting

MAC and IP addresses are stored in EEPROM and designed to be set via SiTCP. A firmware which has at least SiTCP must be loaded to FPGA to access the address. To set the address, a user program with RBCP communications may be written, however, SiTCP tools developed by BBT is also available from its web site after user registration. To write the MAC address, use SiTCPMpcWriter in the BBT's tools. Select the file in the DVD purchased from GND Ltd (recommended) after starting the tool. MAC address has to be unique to each hardware; having the same MAC address in the same network causes a communication trouble. For more about SiTCPMpcWriter, refer to <u>BBT's web page</u>.

To write IP address, use SiTCP Utility (MS Window software) also available in multi platforms (betarelease). This procedure must be performed after installing the MAC address. Check on "access to EEPROM" which is marked in the red square in the figure below. Specify the current IP address and press "show(表示)" button. If the "eye" in the upper right corner blinks and the information is shown, the access was successful. If the current IP address is unknown, start the hardware in the foced default mode (192.168.10.16). Fill in the new IP address to set and press "rewrite(書き替え)". This loads the new IP address only to EEPROM, and the current IP address stays the same. To confirm the IP address in EEPROM, again press the "show(表示)". This address is effective after turning on the harware power next time

| l御対象       |             |    | 書換情報       |               |      |

|------------|-------------|----|------------|---------------|------|

| Address 19 | 2.168.10.16 |    | IP Address | 192.168.10.16 |      |

| CP Port 24 |             | 表示 | TCP Port   | 24            | 書き換え |

| DP Port 46 | 60          |    | UDP Port   | 4660          |      |

|            |             |    |            |               |      |

|            |             |    |            |               |      |

|            |             |    |            |               |      |

|            |             |    |            |               |      |

Figure 2: SiTCP Utility

# 4. Firmware

# 4.1 Version.1 and Version. 3 series

Major update of the firmware was done in August 2021 from version 1 to version 3. There is no software compatibility between them, because of the change of the local bus controller (BCT) structure. Version. 2 is an internal development and not released. Version.1 uses some of the RECP address as the data bus, but version.3 uses the full RECP address (32bit) and the full RECP data (8 bit) as they are. The modification above seamlessly enables FPGAModule class as a wrapper to RECP class. In the DAQ / slowcontrol software for version 3 firmware, RECP address specifies the local modules, making ModuleID and LocalAddress in version 1 obsolete. ModuleID and LocalAddress reflects the Bus Controller (BCT) structure of version 1, which information is irrelevant to the (non developper) users.

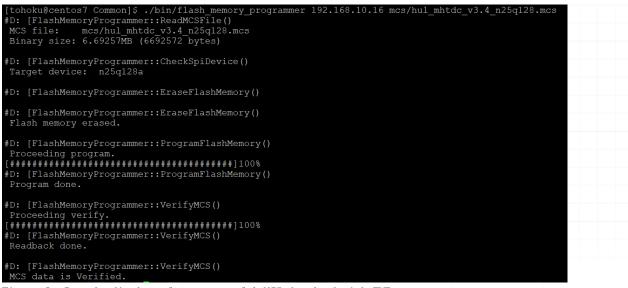

Version.3 is newly equipped with two local modules common to all: Flash Memory Programmer (FMP) and Self Diagnosis System (SDS). FMP writes SPI flash memory via SiTCP. It has enabled a remote downloading of the firmware (MCS file) to EEPROM via ethernet, eliminating the offline download procedure using a USB-JTAG cable. SDS diagnoses the status of FPGA and the board. It audits the number of soft error corrections caused by radiations, or detects an un-recoverable error. Surveillance of FPGA temperatures and critical voltages (VCCINT, VCCAUX and VCCBRAM) are also implemented.

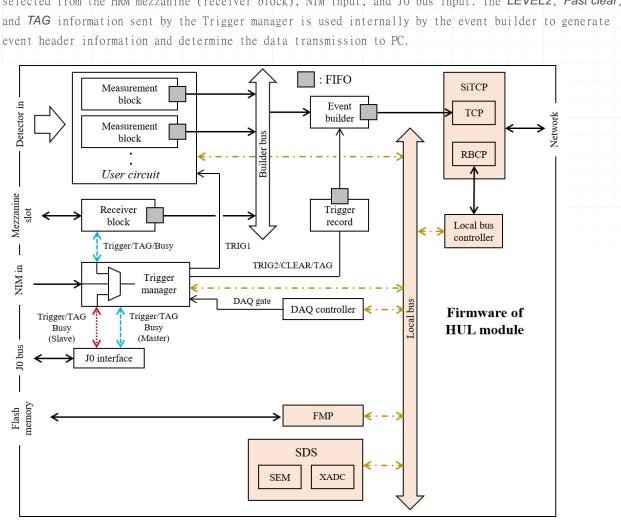

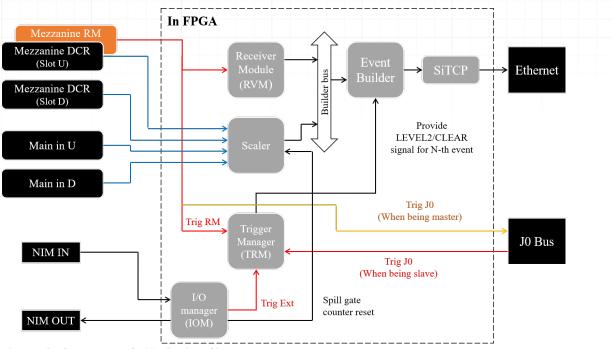

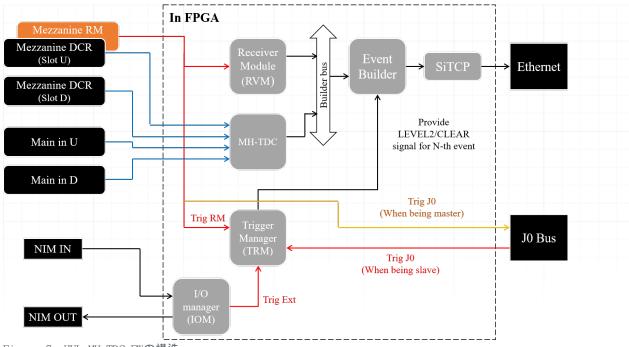

# 4.2 Basic structure of HUL firmware

There are two types of HUL firmware: with or without data acquisition by the PC. An example for the former is TDC, and the latter is a trigger logic. The latter has the individual block structure depending on the function, but the former (data-acquisition) has a common block structure. The following is the common block diagram. The components shown in orange in the figure are the functions implemented in all firmware. The local bus that controls each local module is controlled by the local bus controller (BCT), which is connected to SiTCP's RBCP (UDP). FMP and SDS are local modules implemented in all version.3 firmware, and their functions are as described above.

The white squares in the figure represent the parts related to data acquisition. They are called a measurement block, such as TDC and scaler. These features are mainly implemented in the block labeled as *User circuit*. The data from these *user circuits* is collected in the event builder block via the builder bus, attached with event headers, and then transferred to the PC via SiTCP. The Receiver block, trigger manager, and J0 interface are the blocks involved in trigger I / 0. HUL is designed to receive trigger and event tag information sent by Master Triger Module (MTM: GNN-570). The receiver block is activated when the HRM mezzanine card is installed, and gains the role of receiving the trigger from the upstream circuit. This block is also connected to the builder bus to transfer the received trigger information to the PC when the trigger is received. When using the receiver block, HUL is most likely the J0 bus master in the VME crate. The J0 interface sends the trigger and tag information received by the receiver block to the J0 bus if the HUL is the J0 bus master. In the case of HUL being a J0 slave, the trigger information coming from the J0 bus is passed to the trigger manager. To make HUL a general-purpose module, it supports trigger input from the NIM port in the absence of MTM. The trigger manager is responsible for trigger distribution inside the firmware, and the trigger input source may be

selected from the HRM mezzanine (receiver block), NIM input, and JO bus input. The LEVEL2, Fast clear,

Figure 1: Block diagram of data-acquisition-type firmware

# 4.3 Commons to all HUL firmware

hul software package manages the addresses of BCT, FMP, and SDS, the common parts of the firmware, in the file common/src/RegisterMapCommon.hh .

### 4.3.1 Reset sequence

From the update of December 19, 2017, the reset sequence of all firmware has been standardized. In the previous firmware, there was no way of resetting other than turning off the power, when the BCT hangs. In MH-TDC, some FIFOs were not reset even if BCT reset was applied, and the DAQ hang state was not cleared. Therefore, a few reset levels have been introduced to deal with the problem.

#### Reset procedures (from milder to harder)

- BCT reset: Writing BCT Reset command in the designated address with RBCP. User modules under BCT control are reset in the firmware signal. Normally used.

- SiTCP reset: Calling Reset\_SiTCP defined in sitcp\_controller.cc. Will be reset even if the BCT is hung or deadlocked.

- Hard reset: Pressing SW3 on the board. All circuits including SiTCP are reset. Most enforceable reset procedure of all.

Use BCT reset normally, and if BCT deadlocks by a mis-operation, use SiTCP reset. If SiTCP hangs as well, use Hard reset.

### 4.3.2 Network speed supported

The currently released firmware, SiTCP only works in the 1 GbE mode. SiTCP supports both 100 Mbps and 1 GbE modes and can be configured to automatically switch. However, the existing firmware disables the automatic switching function for the convenience of the PHY chip being used. 100 Mbps mode will never be implemented, because there would be no needs for it anymore. Do not connect to a 100Mbps-only network switch. SiTCP will not communicate.

# 4.3.3 Bus controller (BCT)

Bus controller (BCT) has the functions of issuing a BCT reset, acquiring a version numer, and reconfiguring the FPGA, in addition to the usual functions to access the local modules. The special functions are available by executing the following operations to the listed RBCP address.

| Register | address     | operation | bit width | memo                                                                                                                               |

|----------|-------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------|

| Reset    | 0xE000'0000 | W         | -         | Asserting module reset signal to all modules except SiTCP.                                                                         |

| Version  | 0xE010'0000 | R         | 32        | Returns Firmware ID and version number. Needs to read 4 bytes.                                                                     |

| Reconfig | 0xE020'0000 | W         | -         | Sends Low to PROG_B_ON to re-configure FPGA. SiTCP connection will be immediately closed, and may be reconnected in a few seconds. |

### RBCP address for special functions of BCT (Module ID: 0xE)

# 4.3.4 Flash Memory Programmer (FMP)

FMP sends SPI commands from the PC and execute supported functions by the memory chip, such as read / write page data. Such SPI commands include erase, write and read memory. The same operations which Vivado does to the memory (erase, write, and verify) has now become available over the network by FMP. There is a known bug in FMP: the next page write request is accepted before the precious command finishes. Currently, the software simply waits a sufficient amount of time before sending the next page write command, but this is not a very good solution. Eventually, the FMP module may be corrected. Because of this wait time, it takes longer time to write than the network speed anticipates. If write-failures occur frequently, please contact the author of this document. The RBCP address is listed

below; it is not recommended to control FMP from anything other than FlashMemoryProgrammer.cc included in the *hul\_software* package. If the write-lock bit is accidentally set, that memory block may never be writitten again.

| Register       | address      | operation | bit width      | memo                                                             |

|----------------|--------------|-----------|----------------|------------------------------------------------------------------|

|                |              |           |                | Obtain the status bit of FMP module.                             |

| Status         | 0xD000'0000  | R         | 8              | Currently, the lowest bit is assigned to SPI command cycle busy. |

|                |              |           |                | Mode change of SPI sequence.                                     |

|                |              |           |                | bit 1-2: SPI sequence mode                                       |

|                |              |           |                | • 0x0: Read mode                                                 |

|                |              |           |                | • Ox1: Write mode                                                |

| Status         | 0xD000'0000  | R/W       | 8              | • 0x2: Instruction mode                                          |

|                |              |           |                | bit 3: Dummy mode                                                |

|                |              |           |                | Sets chip select to be OFF, making the flash memory              |

|                |              |           |                | immune to the SPI sequence.                                      |

| Register       | 0xD020'0000  | R/W       | 64 SPI command |                                                                  |

| InstLength     | 0xD030'0000  | R/W       | 3              | SPI command length                                               |

| ReadLength     | 0xD040'0000  | R/W       | 10             | page read length                                                 |

| WriteLength    | 0xD050'0000  | R/W       | 10             | page write length                                                |

| ReadCountFIFO  | 0xD060'0000  | R         | 10             | read count for FIFO where the page-read data are stored.         |

| ReadFIFO       | 0xD070'0000  | R         | 8              | 8-bit (byte) wide readout from the read FIFO.                    |

| WriteCountFIFC | 00xD080'0000 | R         | 10             | write count for FIFO where the page-write data are stored.       |

| WriteFIFO      | 0xD090'0000  | W         | 8              | 8-bit (byte) wide writein to the write FIFO.                     |

| Execute        | 0xD100'0000  | W         | _              | execute the SPI sequence.                                        |

# 4.3.5 Self Diagnosis System (SDS)

SDS is a self-diagnosis program. Soft Error Mitigation (SEM) and XADC, IP cores of Xilinx FPGA, are implemented and monitored. SEM is an IP core that detects, corrects, and classifies single event upsets (SEUs). SDS detects the number of errors corrected and the occurrence of un-correctable errors. If the system falls into an uncorrectable state, reconfiguring the FPGA from the flash memory or performing a power cycle is necessary. Also, it is possible to intentionally inject SEU, but it will be an advanced use of SDS; please check how to use SEM in the Xilinx User Guide.

XADC is the collections of built-in ADCs in Xilinx FPGA HUL obtains FPGA temperature, VCCINT, VCCAUX, VCCBRAM voltages via XADC.

SEM has an unresolved issue. The incorrectable error staus may become 1 after the power is turned on in some FPGAs. The cause is not clear, but in such cases, reset the SEM once by executing reset\_sem in the *hul\_software* package after turning on the power.

| Register       | address       | operation | bit width | memo                                           |

|----------------|---------------|-----------|-----------|------------------------------------------------|

| SdsStatus      | 0xC000'0000   | R         | 8         | Obtain the status bit of SDS module.           |

|                |               |           |           | Select DRP mode of XADC.                       |

| XadcDrpMode    | 0xC010'0000   | R/W       | 1         | • OxO: Read mode                               |

| Audebi pmode   | 0.0000        | 10/ 11    | 1         | • Ox1: Write mode                              |

| XadcDrpAddr    | 0xC020'0000   | R/W       | 7         | Supply DRP address of XADC.                    |

| XadcDrpDin     | 0xC030'0000   | R/W       | 16        | Supply DRP data for input to XADC.             |

| XadcDrpDout    | 0xC040'0000   | R         | 16        | Obtain DRP data from XADC.                     |

| XadcExecute    | 0xC0F0'0000   | W         | -         | Execute DRP access to XADC.                    |

| SemCorCount    | 0xC100'0000   | R         | 16        | Number of corrections to SEU by SEM.           |

| SemRstCorCount | t 0xC200'0000 | W         |           | Reset SemCorCount.                             |

| SemErroAddr    | 0xC300'0000   | W         | 40        | Supply address to `inject_address` port of SEM |

| SemErroStrobe  | 0xC400'0000   | W         | -         | Send a pulse to `inject_strobe` port of SEM.   |

### RBCP address of SDS (Module ID: 0xC)

### **Contents of SdsStatus**

| bit number | Status                 | memo                                                                                                                                                     |

|------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Over temp              | Indicates that the FPGA temperature has exceeded 125 °C. Turn off the power of HUL immediately to cool down, because there is a serious lack of cooling. |

| 2          | Temp alarm             | Indicates that the FPGA temperature has exceeded 85 °C. The cooling capacity is most likely insufficient.                                                |

| 3          | VCCINT alarm           | It indicates that the voltage of VCCINT has exceeded the normal range (0.97–1.03V). Some trouble is occurring on the board.                              |

| 4          | Reserved               |                                                                                                                                                          |

| 5          | Watchdog alarm         | Indicates that the SEM heartbeat signal is absent. Some trouble is occurring in the SEM.                                                                 |

| 6          | Uncorrectable<br>error | Indicates that the SEM has detected an uncorrectable radiation error.<br>FPGA needs to be reconfigured.                                                  |

| 7          | Reserved               |                                                                                                                                                          |

| 8          | Reserved               |                                                                                                                                                          |

# 4.4 HUL Skeleton

This project is the minimum configuration of firmware that implements SiTCP but does almost nothing. Please use it as a sample when making firmware for HUL. There are only two functions, one is to take OR of the input signals and output it to NIM, and the other is to illuminate the LED with SiTCP or DIP. For the input signals, the fixed inputs (main input ports) and mezzanine inputs (assuming DCR v1 or v2) are grouped in 32 channels of one connector and their OR signal appears in the four NIM OUTs. Skeleton is misspelled in the VHDL source, but left as it is, because a correction influences in a wide range of codes. An example for using the NIM-Ex mezzanine card is included under <u>sources\_1 / example\_design /</u>. Please refer to the toplevel.vhd enclosed.

### Firmware ID and the current version

When Version is read from BCT, a 32-bit register is returned. Of these, the upper 16 bits are the Firmware ID, and the lower 16 bits are the version numbers (major version 8bit + minor version 8bit). The current HUL Skeleton ID and versions are as follows:

| Firmware ID 0x0000     |              |             |             |       |  |  |

|------------------------|--------------|-------------|-------------|-------|--|--|

| Major version 0x03     |              |             |             |       |  |  |

| Minor version 0x02     |              |             |             |       |  |  |

|                        |              |             |             |       |  |  |

| In the following, vers | ions are wri | tten in a f | format like | v3.2. |  |  |

### Version history

| Version | Release date | Modifications                   |

|---------|--------------|---------------------------------|

| -       | -            | There is no versions up to v2.x |

| v3.2    | 2021.08.01   | Updated to Version.3            |

### 4.4.1 Register map

### RBCP address of LED (Module ID: 0x0)

### LED assignment

LED1-3 reflects LED register or bit 2-4 of SW2. LED4 is connected to "Over temp" flag of SDS.

# 4.5 HUL RM

By mounting the Mezzanine HRM, the HUL RM can be a JO bus master and can operate as a DAQ module that reads the data received by the HRM. It is the basis of the MH-TDC and scaler firmware, and should be used as a starting point when developing a new DAQ type firmware.

Since the response to the trigger input is based on this firmware, here we will explain in detail the trigger system and the response of the event builder to it.

### Firmware ID and the current version

| Firmwa | are | ID   | 0x0415 |

|--------|-----|------|--------|

| Major  | vei | sior | n 0x03 |

| Minor  | vei | sior | n 0x02 |

| Version | Release date | Modifications                                                                                                                                                                                            |

|---------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v1.0    | 2016.12.23   | Initial release                                                                                                                                                                                          |

| v1.1    | 2017.01.15   | RVM data header changed from 0x9C to 0xF9.                                                                                                                                                               |

|         |              | Vivado update 2016.2 => 2016.4 TRM middle buffer changed from disperse RAM to BRAM. The depth changed from 128 to 256. Prog Full threshold introduced.                                                   |

| v1.2    | 2017.01.27   | The reason for the depth of 256 is to be below SCR block depth. RVM middle<br>buffer depth is also changed to 256. Functionality seen from the outside of<br>the module stays the same.                  |

| v1.3    | 2017.03.22   | Solved the problem that the initial register of IOM was not set correctly.<br>Solved the problem that the number of words written in header 2 became 0 in<br>the first event after turning on the power. |

| v1.4    | 2017.05.09   | Solved the problem of not responding to Clear (BUSY stays standing).                                                                                                                                     |

| v1.5    |              | Solved the problem that HRM hangs when Clear is entered. (Replaced by v1.6 without release.)                                                                                                             |

| v1.6    | 2017.08.22   | Fixed an issue where DAQ would hang if a hard reset was entered within ~2 u after the trigger. A new register for each block to select its response to the hard reset. Added new local address.          |

| v1.7    | 2017.12.19   | Standardlized reset sequence. Bit 24 of Header3 is now indicating whether HRM exists (to be exact, whether DIP2 is ON).                                                                                  |

| v1.8    | 2018.02.02   | Solved the bug that the event tag coming from the JO bus was latched too early and the event number on the HRM side deviated by 1.                                                                       |

| v2.x    | -            | un released                                                                                                                                                                                              |

| v3.2    | 2021.08.01   | Added FMP and SDS. Installed Builder bus. Changed the structure of Local bus.                                                                                                                            |

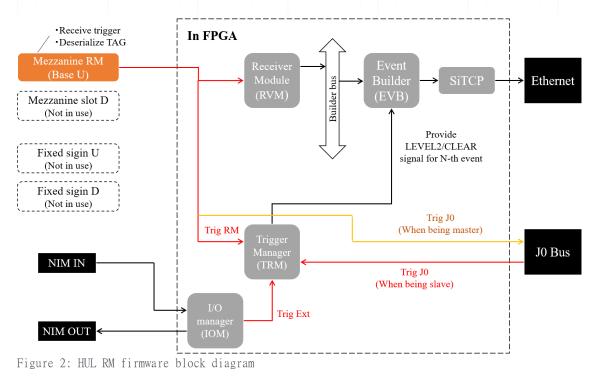

### Overview of module function

Varsian history

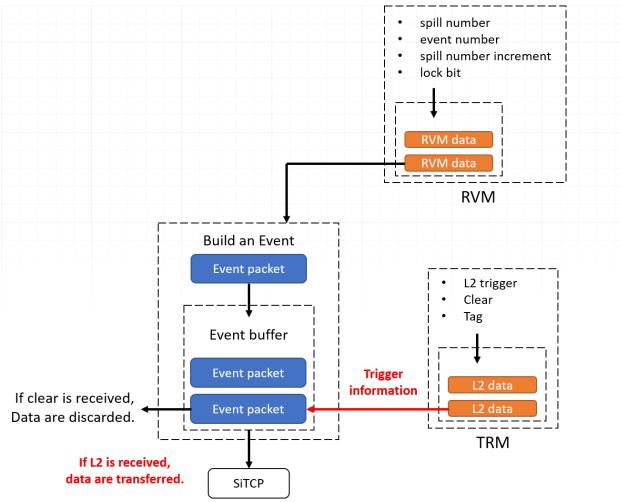

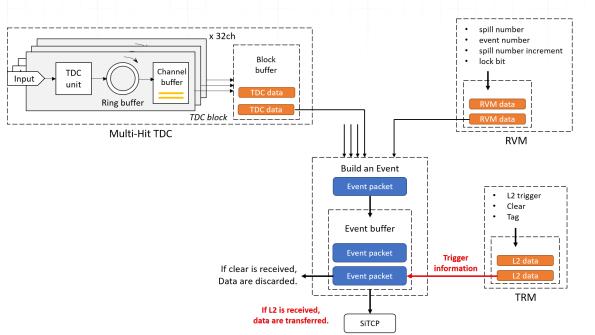

HUL RM data acquisition block diagram is shown below. The modules which do not relate to data acquisision are omitted. The function of HUL RM is the processing of information received and decoded by Mezzanine HRM. Therefore, the function is **implemented only in mezzanine slot U**. The information received by Mezzanine HRM is distributed in three routes. The first is the Receiver Module (RVM), which stores lock bit, spill number increment, spill number (full 8bit), and event number (full 12bit) information and passes them to the EVent Builder (EVB). Data is passed to the Event builder via the builder bus, so the RVM information is contained in the data body. That is, the RVM is part of the measurement block for the EVB. The second route is the distribution of trigger information to the J0 bus. At this stage, the event number is reduced to 3-bit and the spill number is reduced to 1-bit. The third is the input to TRigger Manager (TRM).

The HUL firmware has a module called trigger manager (TRM) that manages the internal trigger distribution. TRM receives trigger signals from three ports, trig Ext (NIM IN), JO bus (if slave), and HRM (if any), and the register sets which port to receive the trigger.

### 4.5 HUL RM

TRM distributes level1 trigger, level2 trigger, clear, and event number (3-bit) and spill number (1bit) information to each measurement block and EVB. For EVB, these are not DAQ data, so the tags from TRM are embedded within the event hearder. The event number and spill number distributed by TRM have been reduced to 3-bit and 1-bit, because this information must be independent to whether HUL is a master or a slave to the J0 bus. If Tag is not received, both event number and spill number will be 0.

I/O Manager (IOM) is a module that controls which FPGA internal signal is assigned to the NIM input / output ports.

There three types of busy signals. First is the module busy, whici is a logical sum of internal blocks in firmware. Second is the JO bus busy received from the JO bus; this is a logical sum of busy signals from HUL, which are slave to the JO bus. Last is the crate busy; this is a logical sum of the module busy, the JO bus busy, and the external busy received from NIM-IN. We use the JO busy and the crate busy, when HUL is a master to the JO bus.

# 4.5.1 Register map of HUL RM

The following is a map dedicated to HUL RM. Even if a module or register with the same name exists in other firmware, it does not necessarily have the same address. Be sure to set according to this map (or RegisterMap.hh and namespace of the distributed software).

| Register     | Address        | Operation | bit width     | description                                           |

|--------------|----------------|-----------|---------------|-------------------------------------------------------|

|              |                | Trigge    | r Manager:    | TRM (module ID = 0x00)                                |

| SelectTrigge | er 0x0000'0000 | R/W       | 12            | Selects trigger port in TRM                           |

|              |                | DAQ       | Controller: I | DCT (module ID = 0x01)                                |

| DaqGate      | 0x1000'0000    | R/W       | 1             | ON/OFF of DAQ gate. TRM disables trigger out if zero. |

|              |                |           |               | Write to this address asserts a soft reset to EVB,    |

| EvbReset     | 0x1010'0000    | W         | -             | and self event counter in Event builder becomes zero. |

|              |                |           |               | (Don't care about the register value.)                |

|              |                | 10 1      | /lanager: IO  | M (module ID = 0x02)                                  |

| NimOut1      | 0x2000'0000    | R/W       | 4             | Determines what to send to NIMOUT1.                   |

| NimOut2      | 0x2010'0000    | R/W       | 4             | Determines what to send to NIMOUT2.                   |

| NimOut3      | 0x2020'0000    | R/W       | 4             | Determines what to send to NIMOUT3.                   |

| NimOut4      | 0x2030'0000    | R/W       | 4             | Determines what to send to NIMOUT4.                   |

| ExtL1        | 0x2040'0000    | R/W       | 3             | Determines which NIMIN is connected to ExtL1.         |

| ExtL2        | 0x2050'0000    | R/W       | 3             | Determines which NIMIN is connected to ExtL2.         |

| ExtClr       | 0x2060'0000    | R/W       | 3             | Determines which NIMIN is connected to Ext clear.     |

| ExtBusy      | 0x2070'0000    | R/W       | 3             | Determines which NIMIN is connected to Ext busy.      |

| ExtRsv2      | 0x2080'0000    | R/W       | 3             | Determines which NIMIN is connected to Ext rsv2.      |

### Trigger Manager (TRM)

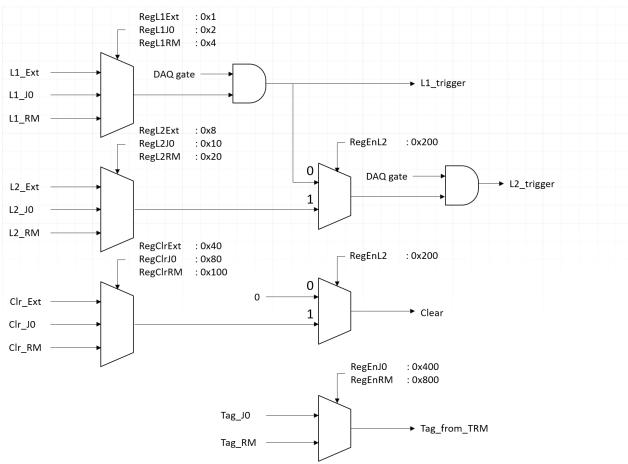

TRM decides which input port signal to be used as a trigger, and sends L1, L2, and Clear signals to the FPGA. Also, Tag signal is repeated, if received, for a redistribution in FPGA. Which port signal is selected is set by the 12-bit register SelectTrigger. The relationship between the trigger signal path and SelectTrigger is summarized in Figure. Which port receives the L1 trigger is determined by the 3 bits. Please note that if two or more bits are set, the trigger will come out in OR. Once the L1 route is determined, it will be ANDed with the DAQ gate (DAQ controller management) and distributed as the L1 trigger. The selection of L2 trigger and Clear is also performed with the 3 bits, but these are affected by EnL2 bit after routing. If EnL2 is 0, L2 contains a copy of L1 and Clear is always 0. In a simple system without MTM-RM, set EnL2 to 0. L2 is distributed as L2 trigger after ANDed with the DAQ gate. Tag information source is selected between J0 or HRM using EnJ0 and EnRM bits, respectively. If both are set to 1, Tag will not be issued.

Figure 3: Trigger route in TRM

A list of register values to be stored in TRM::SelectTrigger address. Since each bit is a switch for the appropriate selector, this register is a 12-bit wide bit string instead of an integer value. Exceptionally, only RegEnJO is used outside of TRM. Only when RegEnJO is high and DIP SW2 No. 2 (mezzanine HRM) is low, module busy is sent to JO bus. If you want to insert a module into the crate but do not want to affect the JO bus, set this register RegEnJO to O.

| Register label | Register value | description                                                   |  |  |  |

|----------------|----------------|---------------------------------------------------------------|--|--|--|

| RegL1Ext       | 0x001          | NIMIN provides L1 trigger.                                    |  |  |  |

| RegL1J0        | 0x002          | JO bus provides L1 trigger.                                   |  |  |  |

| RegL1RM        | 0x004          | Mezzanine HRM provides L1 trigger.                            |  |  |  |

| RegL2Ext       | 0x008          | NIMIN provides L2 trigger.                                    |  |  |  |

| RegL2J0        | 0x010          | JO bus provides L2 trigger.                                   |  |  |  |

| RegL2RM        | 0x020          | Mezzanine HRM provides L2 trigger.                            |  |  |  |

| RegCl rEx t    | 0x040          | NIMIN provides Clear.                                         |  |  |  |

| RegClrJO       | 0x080          | JO bus provides Clear.                                        |  |  |  |

| RegC1 rRM      | 0x100          | Mezzanine HRM provides Clear.                                 |  |  |  |

| RegEnL2        | 0x200          | 0: L2=L1 trigger、1: L2=L2 input                               |  |  |  |

| DeeEmIO        | 0              | Tag information from JO bus. If this bit is 1, module busy is |  |  |  |

| RegEnJO        | 0x400          | sent to JO bus.                                               |  |  |  |

| RegEnRM        | 0x800          | Tag information from HRM.                                     |  |  |  |

### I/O Manager (IOM)

IOM has the function of assigning the signal inside the FPGA to NIMIN or NIMOUT. For example, if Reg\_o\_ModuleBusy is set to AddrNnimout1, the BUSY signal will be output to NIM output 1 on the front panel. If Reg\_i\_Nimin1 is set for AddrExtL1, NIM input No. 1 is assigned to the L1Ext line of TRM. The register values that may be stored in the register address are summarized below. The syntax of assignments are opposite between NIMOUTs and NIMINs; NIMOUTs has the address where the signal register value is written in, whereas for inputs, signal has the address where NIMIN values is written in. The register values are interpreted as integers, meaning exclusive with each other.

| Register label   | Register value | description                                                                                                                                                                                    |  |  |  |

|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                  | Si             | ignals available for NIMOUT                                                                                                                                                                    |  |  |  |

| Reg_o_ModuleBusy | 0x0            | Module busy, meaning only the busy status of the module. JO<br>bus busy or ExtBusy are not included.                                                                                           |  |  |  |

| Reg_o_CrateBusy  | 0x1            | CrateBusy, including the module busy, JO bus busy and<br>ExtBusy. Usage of this signal assumes that HUL is the bus<br>master, and HRM returns the same busy to master trigger<br>module (MTM). |  |  |  |

| Reg_o_RML1       | 0x2            | HRM L1 trigger as HRM has received.                                                                                                                                                            |  |  |  |

| Reg_o_RML2       | 0x3            | L2 trigger as HRM has received.                                                                                                                                                                |  |  |  |

| Reg_o_RMC1 r     | 0x4            | Clear as HRM has received.                                                                                                                                                                     |  |  |  |

| Reg_o_RMRsv1     | 0x5            | Rserve 1 signal as HRM has received.                                                                                                                                                           |  |  |  |

| Reg_o_RMSnInc    | 0x6            | Spill Number Increment of HRM                                                                                                                                                                  |  |  |  |

| Reg_o_DaqGate    | 0x7            | DAQ gate in DCT                                                                                                                                                                                |  |  |  |

| Reg_o_DIP8       | 0x8            | ch 8 of DIP SW2                                                                                                                                                                                |  |  |  |

| Reg_o_clk1MHz    | 0x9            | 1 MHz clock                                                                                                                                                                                    |  |  |  |

| Reg_o_clk100kHz  | OxA            | 100 kHz clock                                                                                                                                                                                  |  |  |  |

| Reg_o_clk10kHz   | 0xB            | 10 kHz clock                                                                                                                                                                                   |  |  |  |

| Reg_o_clk1kHz    | 0xC            | 1 kHz clock                                                                                                                                                                                    |  |  |  |

|                  |                | NIMIN ports available                                                                                                                                                                          |  |  |  |

| Reg_i_nimin1     | 0x0            | NIMIN1                                                                                                                                                                                         |  |  |  |

| Reg_i_nimin2     | 0x1            | NIMIN2                                                                                                                                                                                         |  |  |  |

| Reg_i_nimin3     | 0x2            | NIMIN3                                                                                                                                                                                         |  |  |  |

| Reg_i_nimin4     | 0x3            | NIMIN4                                                                                                                                                                                         |  |  |  |

| Reg_i_default    | 0x7            | If this register value is set, the default assignment are<br>done for signal lines (see next table), including the<br>NIMOUTS.                                                                 |  |  |  |

| IOM | default | assignments | as | listed | below. |  |

|-----|---------|-------------|----|--------|--------|--|

|-----|---------|-------------|----|--------|--------|--|

| default |

|---------|

| IMIN1   |

|         |

|         |

| IMIN3   |

| IMIN4   |

| I       |

# 4.5.2 DIP SW and LED on HUL RM

### **DIP SW2 functions**

| Switch number function |                        | detail                                                                                                                      |  |  |  |  |

|------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                      | SiTCP force<br>default | ON for SiTCP forced default (192.168.10.16). Must be set before power on.                                                   |  |  |  |  |

| 2                      | Mezzanine HRM          | ON for Mezzanine HRM installed. The actual effect by this mode is described later. This bit status appears in data header3. |  |  |  |  |

| 3                      | Force BUSY             | Forced high for Crate Busy and Module Busy. Used for connection check.                                                      |  |  |  |  |

| 4                      | Bus BUSY               | ON to include JO bus busy to Crate Busy. OFF otherwise.                                                                     |  |  |  |  |

| 5                      | LED                    | ON to turn on LED4.                                                                                                         |  |  |  |  |

| 6                      | Not in Use             |                                                                                                                             |  |  |  |  |

| 7                      | Not in Use             |                                                                                                                             |  |  |  |  |

| 8                      | Level                  | Appears as IOM DIP8 signal.                                                                                                 |  |  |  |  |

### The effect of Mezzanine HRM (DIP SW2 #2)

If this bit is ON, a few functions change with regard to Mezzanine HRM.

### Event Builder includes RVM in the event packet.

If this bit is ON, the information in RVM is read by Event Builder and includes into the event packet.

### Mezzanine base (U) signal direction change

If this bit is ON, a few signal lines to be LVDS output as required by Mezzanine HRM. if this bit is OFF, all the slot lines will become LVDS inputs.

#### J0 bus master mode to be ON

If this bit is ON, L1, L2, Clear, Tag information are sent to the JO bus, and the BUSY signal is received from JO bus. To be a JO bus master, it is also necessary to turn all DIP SW1 ON.

| ) bus slave | ve mode to be OFF                                              |  |

|-------------|----------------------------------------------------------------|--|

| f this bit  | t is OFF, L1, L2, Clear, Tag will not be accepted from J0 bus. |  |

| elow is the | he relation between JO bus signals and the trigger signals.    |  |

| J0 bus      | Trigger signal                                                 |  |

| S1          | RM_Clear                                                       |  |

| S2          | RM_Level2                                                      |  |

| S3          | RM_SpillNumber(0)                                              |  |

| S4          | RM_Level1                                                      |  |

| S5          | RM_EventNumber(0)                                              |  |

| S6          | RM_EventNumber(1)                                              |  |

| S7          | RM EventNumber(2)                                              |  |

### LED indication

| _ |            |                                              |  |  |  |  |  |  |

|---|------------|----------------------------------------------|--|--|--|--|--|--|

|   | LED number | description                                  |  |  |  |  |  |  |

|   | LED1       | Light when TCP connection is open.           |  |  |  |  |  |  |

|   | LED2       | Light when module busy is high.              |  |  |  |  |  |  |

|   | LED3       | Light when DIP SW2 #2 (Mezzanine HRM) is ON. |  |  |  |  |  |  |

|   | LED4       | Light when DIP SW2 #5 (LED) is ON.           |  |  |  |  |  |  |

|   |            |                                              |  |  |  |  |  |  |

# 4.5.3 DAQ behavior of HUL RM

This section describes data flow and DAQ behavior. The DAQ function consists of each measurement module (hereinafter referred to as the measurement block) and the Event Builder module. The data flow is shown in Figure. When the trigger is received, each measurement block processes the data according to the determined operation and saves it in the block buffer. The measurement block has an internal block buffer that can temporarily store multi-events. Event Builder reads the data from each measurement block and continues to build events unless the event buffer is full. Therefore, the DAQ function operates synchronously with the trigger until the data is written to the block buffer; the subsequent processing does not depend on the external signals nor states and continues to build and transfer the data as long as the data link speed allows. For HUL RM, the measurement blocks are only RVM and TRM. Strictly speaking, TRM is not a measurement block because the TRM information is not included in the data body but in the header. The only event-built information is RVM data, and the TRM information is used to control data transfer. The TRM stores whether the L2 trigger or Clear was sent in the Nth event, and this information is used by the Event Builder to decide whether to send this event packet to SiTCP or just drop it. Therefore, HUL's DAQ function does not have a fast clear nor clear BUSY functions. All events raised by the L1 trigger are digitized and built once. However, the self-event number assigned by Event Builder is not incremented unless it is forwarded.

RVM latches the information shown in <u>Figure</u> at the timing of L2 trigger and saves it in the block buffer.

Figure 4: DAQ data flow of HUL RM firmware

### The timing when Module Busy is asserted

The definition of Module BUSY in HUL RM is the OR of the BUSY signals listed below. Block full and SiTCP full occurs only when network forwarding can not keep up, so usually BUSY is a fixed length of 160 ns. Currently, Self-busy, set to 160 ns, is rather long, and it may be shortened in the future.

| BUSY type  | BUSY length | memo                                                         |

|------------|-------------|--------------------------------------------------------------|

| Solf buoy  | 160 ns      | Asserted with a fixed length since the L1 trigger is         |

| Self busy  | 100 118     | detected.                                                    |

|            |             | BUSY is output when the block buffer is full. It is asserted |

|            |             | when the L1 trigger rate exceeds the data processing speed   |

| Block full | -           | of the subsequent circuit. In other words, it means that TCP |

|            |             | transfer cannot catch up, so it is practically equivalent to |

|            |             | SiTCP full.                                                  |

|            |             | Asserted when the TCP buffer of SiTCP is Full, meaning that  |

| SiTCP full | -           | the amount of data which the Event Builder is trying to send |

|            |             | is too large for the network bandwidth.                      |

| Data sti | ructure  |         |          |        |            |           |       |        |         |        |      |      |       |       |          |  |

|----------|----------|---------|----------|--------|------------|-----------|-------|--------|---------|--------|------|------|-------|-------|----------|--|

| In HUL,  | 32-bit   | is one  | word,    | and th | e three-wo | rd header | and   | varia  | able-le | ngth   | data | body | are   | one   | event    |  |

| block.   |          |         |          |        |            |           |       |        |         |        |      |      |       |       |          |  |

| Header   | word     |         |          |        |            |           |       |        |         |        |      |      |       |       |          |  |

|          | . (Magic | word)   |          |        |            |           |       |        |         |        |      |      |       |       |          |  |

| MSB      |          |         |          |        |            |           |       |        |         |        |      |      | LSB   |       |          |  |

|          |          |         |          |        | 0xFFF      | F0415     |       |        |         |        |      |      | I     |       |          |  |

| Header2  | (event   | size)   |          |        |            |           |       |        |         |        |      |      |       |       |          |  |

| 1        | 0xFF     | I       | 0x00     | I      | "00000"    | I         | N     | umber  | of word | (11-b  | oit) |      | Ι     |       |          |  |

| "Number  | of wor   | d" indi | cates t  | he num | ber of wor | ds contai | ned i | in the | e data  | body,  | not  | incl | uding | g the | e header |  |

| Header3  | (event   | number) |          |        |            |           |       |        |         |        |      |      |       |       |          |  |

|          | 0xFF     | HF      | RM exist | "000"  | Tag (4-b   | it)       | S     | elf co | unter ( | 16-bit | :)   |      |       |       |          |  |

If *HRM* exist is 1, ch2 of DIP SW2 is on, meaning HRM was installed. This means that data body has a RVM word. *Tag* " is the 4-bit Tag information from TRM. The lower 3 bits are the lower 3 bits of the RM Event Number, and the 4th bit is the least significant bit of the RM spill number. "Self counter" is a local event number that is incremented each time an event is forwarded. Starts with 0.

### Data body

| RVM word                                     |                    |  |

|----------------------------------------------|--------------------|--|

| 0xF9   "00"   Lock   SNI   Spill Num (8-bit) | Event Num (12-bit) |  |

*Lock* means the RM lock bit, must be 1. *SNI* means Spill Number Increment, which becomes 1 at the change of the Spill Number (not tested if it is true). *Spill Num* is the spill number, and *Event Num* is the event number, received by HRM, respectively.

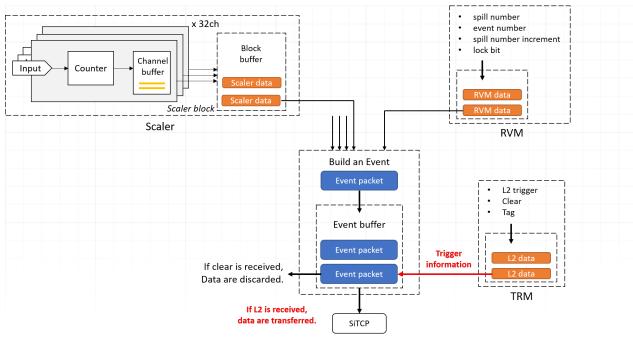

# 4.6 HUL Scaler

HUL Scaler is a firmware that adds a scaler function to HUL RM. The implemented scaler is a 28-bit synchronization counter that samples at 300 MHz. Since the HUL Scaler has many functions in common with the HUL RM, only the differences will be mentioned. **Firmware ID and current version**

| ID    |         | 0x4ca1 |

|-------|---------|--------|

| Major | version | 0x03   |

| Minor | version | 0x03   |

### Version history

Exactly same with HRM, except the current version is v3.3.

### **Overview of Module functions**

HUL Scaler is implemented for Mezzanine slot D and on-board input ports, in addition to Mezzanine slot U configured for HRM. DCR v1 (v2) is assumed to be installed in the Mezzanine slot(s), implementing

scalers up to 128 channels. It is also possible to mount HRM (instead of DCR) on Mezzanine slot U to become a JO bus master like HUL RM firmware. In this case, the Ch O-31 assigned to slot U is deleted from the data.

The Scaler consists of a 300 MHz, 28-bit long counter that latches the counter at the timing of the L1 trigger and writes it to the buffer. The HUL scaler has two new internal signals connected to the IOM: one is the *spill gate*, which enables the scalers only while this signal is high. The other is *counter reset*, which resets all counts to zero when it becomes high. Enable/Disable NIM input counter reset is set with *enable\_hdrst* (in v1.6 and later). Other features are common to HUL RM.

Figure 5: Structure of HUL Scaler firmware

# 4.6.1 Register map for HUL Scaler

The following is a map dedicated to HUL Scaler. The difference in the signal and address from HUL RM is marked as red . Signal names and the address are defined in RegisterMap.hh and namespace in the software package.

| Register      | Address       | Operation | bit width    | Description                                                                                                                                                                                            |  |

|---------------|---------------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               |               | Trigger   | Manager: T   | RM (module ID = 0x00)                                                                                                                                                                                  |  |

| SelectTrigger | · 0x0000'0000 | R/W       | 12           | Selects trigger port in TRM                                                                                                                                                                            |  |

|               |               | DAQC      | ontroller: D | CT (module ID = 0x01)                                                                                                                                                                                  |  |

| DaqGate       | 0x1000'0000   | R/W       | 1            | ON/OFF of DAQ gate. TRM disables trigger out if zero.                                                                                                                                                  |  |

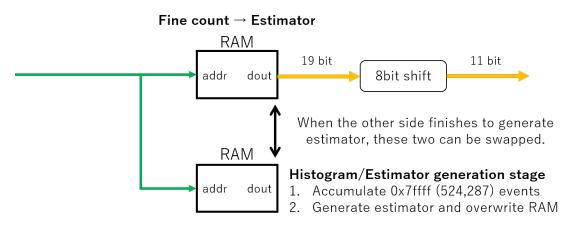

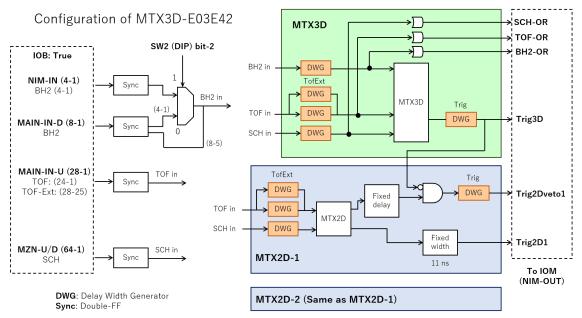

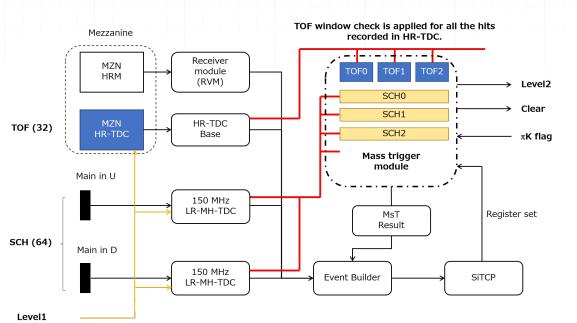

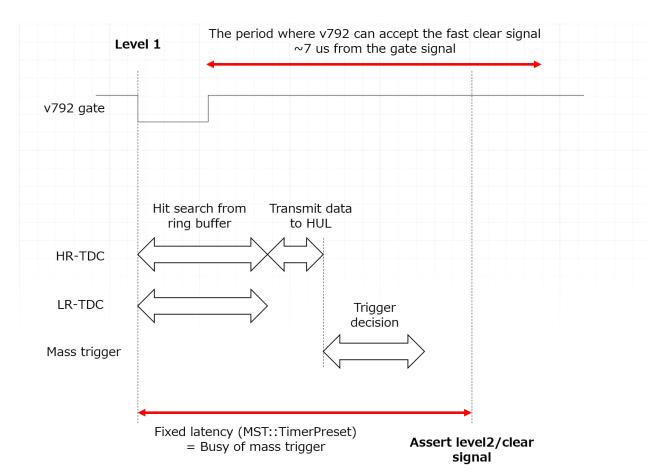

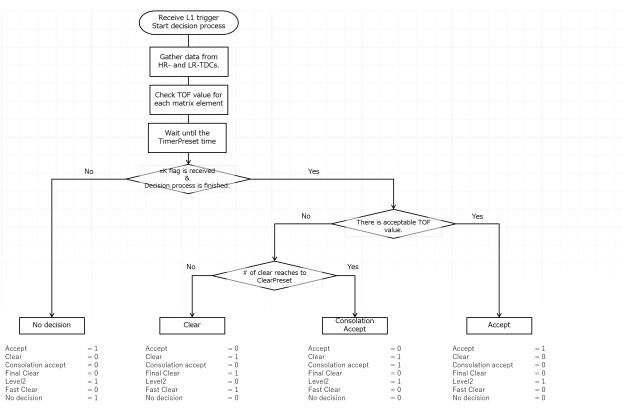

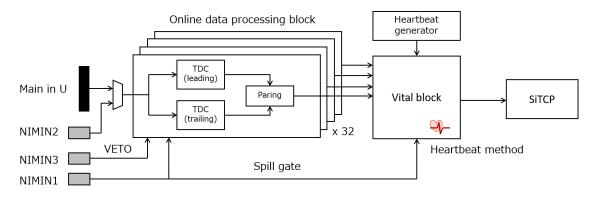

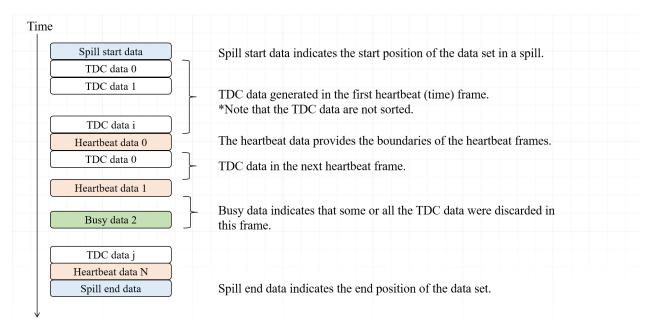

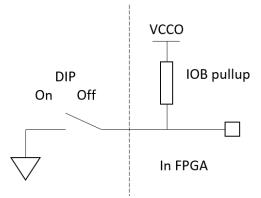

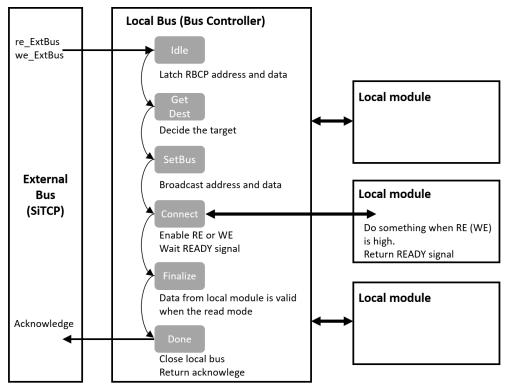

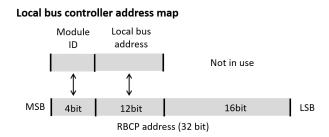

| EvbReset      | 0x1010'0000   | W         | -            | Write to this address asserts a soft reset to EVB,<br>and self event counter in Event builder becomes<br>zero. (Don't care about the register value.)                                                  |  |