# TGC Patch-Panel ASIC Design Report for Production Readiness Review

M. Miyahara, O. Sasaki, H. Asada, Y. Horii, M. Ikeno, H. Inaguma, S. Ito, M. Tomoto, T. Yamada, et al. (TGC Electronics Group) 16 Sep. 2019

## 1. Overview

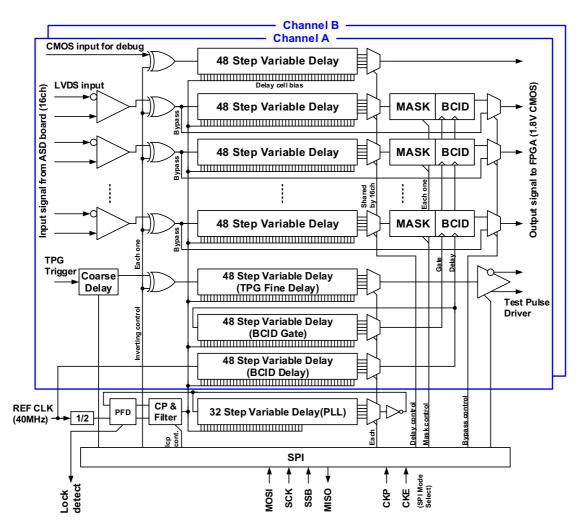

Figure 1 Block diagram of the Patch-Panel ASIC.

Patch-Panel ASIC is a full custom CMOS IC to be implemented on PS board in the PS pack of the TGC system. Figure 1 shows a block diagram. It receives discriminator output signals from two 16-channel ASD boards by LVDS receivers and performs bunch-crossing identification (BCID). The signals from the ASD board are transmitted with the LVDS level via twisted-pair cables. Prior to the BCID, variable delay is introduced to each signal from ASD boards in order to adjust the delay difference from time of flight and cable length and also to adjust the phase difference between LHC 40 MHz clock and signals from ASD boards. The BCID circuit contains

two blocks of variable delay. A block is used to adjust for the phase difference between the clock and hit signals, and the other is used to provide a gate width greater than 25 ns so that a hit can be assigned to either one or two bunch crossings. The BCID circuit can mask individual channels. The IC has test pulse generator in order to provide pulse to ASD boards. The test pulse generation is initiated by the test pulse trigger signal from a CMOS receiver. The delay is programmable in a range from 0 ns to 35 ns with sub-nanosecond resolution. Additional coarse delay is implemented to the test pulse generators.

The IC is subdivided into two parts: Channel A and Channel B. Each part corresponds to a single 16-channel ASD board. Setting of the delay is common to group of signals that come from the same ASD board. The amplitude and the delay of the test pulse trigger are programmable for each ASD board. The SPI protocol is adopted to the control of the IC.

#### 2. Process

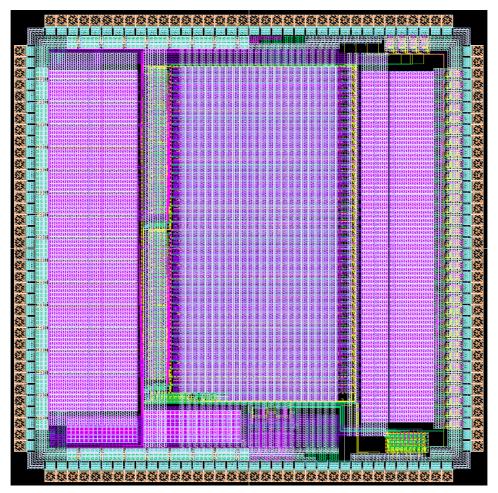

We have developed Patch-Panel ASIC prototype v0 using 0.18  $\mu$ m full custom CMOS technology of Silterra Malaysia. We used the library provided from ARM for standard logic circuits. We designed the circuits of an LVDS receiver, a PLL, a variable delay, and a test pulse generator. LVDS receivers and test pulse generators are based on power supply of 3.3 V and other I/O and internal circuits are based on 1.8 V. We have provided an entire layout by ourselves. The size of a chip is 2.47 mm x 2.47 mm including seal-ring as shown in Figure 2. The plots in the following sections show the results of the measurement of prototype v1 except where otherwise stated.

**Figure 2** Layout of the Patch-Panel ASIC. The size is 2.47 mm x 2.47 mm including seal-ring.

#### 3. LVDS Receiver

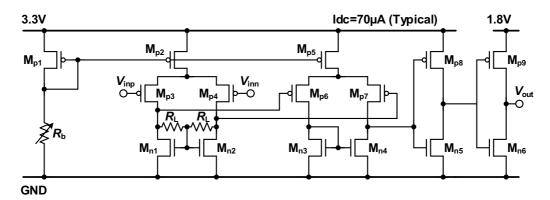

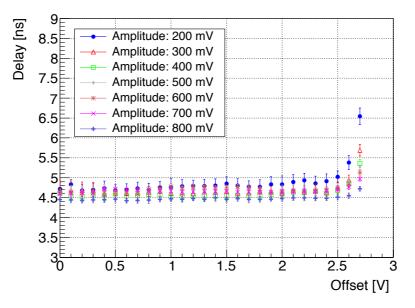

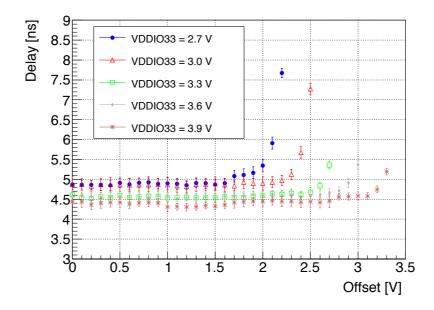

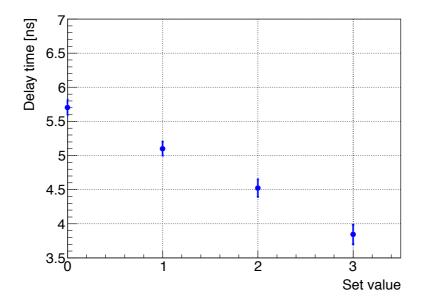

Figure 3 shows a schematic of the LVDS receiver, which consists of two differential amplifiers and two stages of inverter circuits. Bias current can be controlled via two-bit SPI register. We have measured the performance of the receiver of prototype v0 with bias current control code set to d'2. Figure 4 shows propagation delay for various amplitudes and offset voltages of the input differential signals. The offset voltage is defined to be the central voltage of "low" and "high" levels of input differential signals. The amplitude and the offset voltage of the differential signals from the ASD board are 400 mV and 1.2 V, respectively. Figure 5 shows the measured propagation delay depending on the offset voltages for supply voltages of 2.7-3.9 V. The propagation delay shown in Figures 4 and 5 is the sum of the delay of the receiver, the multiplexer, and the output buffer. The variation of the propagation delay due to the change of the operation conditions is less than 1 ns, which satisfies the system requirement. Figure 6 shows the measured propagation delay depending on bias current control codes. Propagation delay is reduced by increasing control code, while the power consumption of LVDS receiver is increased. A typical control code is d'2, which is implemented as the SPI's initial code.

Figure 3 Schematic of the LVDS receiver.

**Figure 4** Propagation delay depending on offset voltage for various amplitudes of the input signals.

Figure 5 Propagation delay depending on offset voltage for power supplies of 2.7-3.9 V.

**Figure 6** Propagation delay depending on the set value for bias current control. The offset voltage is set to 1.2 V, and the amplitude 400 mV.

#### 4. Variable Delay

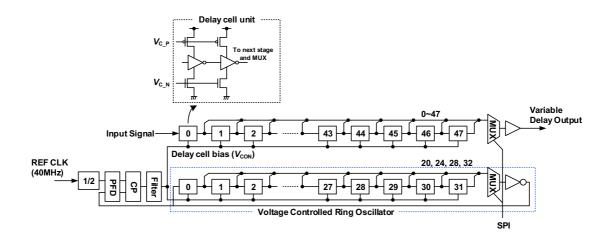

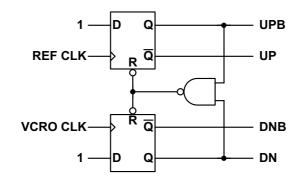

Variable delay circuit with a precision of sub-nanosecond is implemented with a PLL technique for stable delay against changes of operation conditions. Figure 7 shows a block diagram.

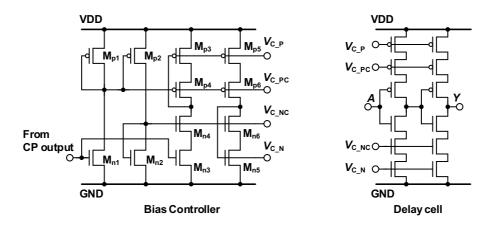

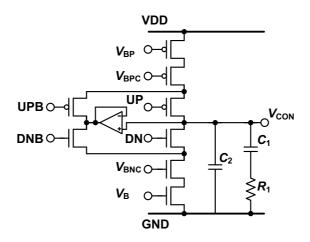

The PLL circuit consists of Voltage Controlled Ring Oscillator (VCRO), Phase Frequency Detector (PFD), Charge Pump (CP), and low-pass filter circuits. The VCRO is formed with 32 stages of delay units and a buffer gate. A selector is incorporated in the VCRO in order to change the number of the delay units in the ring (20, 24, 28, or 32). The selector can adapt fluctuation of the IC production process, and also can change the dynamic range of the variable delay. Each delay unit contains two inverter gates. The propagation delay of a delay unit is controlled by the control voltage ( $V_{cos}$ , which is separated to  $V_{c.s}$  and  $V_{c.p}$ ). Since the signal passing through the ring is inverted by an extra inverter gate after MUX (see Figure 7), the ring works as an oscillator. When a signal takes 25 ns for a round of the ring, the frequency of the VCRO is 20 MHz. The PFD compares the output from the VCRO with a reference clock. When the phase of the VCRO clock is going forward (backward) against the reference clock, the CP decreases (increases) the voltage of  $V_{cos}$ . This loop works as negative feedback and stabilizes the frequency of the VCRO. The negative feedback circuit stabilizes the propagation delay for a round of the ring at 25 ns when a reference clock of 40 MHz is used.

The schematics of the delay unit, PFD, CP, and the low-pass filter are shown in Figure 8. The capacitor of the low-pass filter is implemented outside the chip. In the operation, we will use a 150 pF capacitor. The same design is used for the delay units in PLL and variable delay. The control voltage  $V_{cos}$  is common for the delay units in PLL and variable delay. As far as the PLL circuit is in the locked state and all the delay units behave equally, the propagation delay of the variable delay is kept constant against any changes of the operation conditions (e.g. supply voltage, temperature). One can set the signal delay of the variable delay in accordance with 6-bit register controlled via SPI.

Figure 7 Block diagram of PLL and variable delay.

(a) Block diagram of bias controller (left) and delay unit (right).

(b) Block diagram of PFD.

(c) Block diagram of CP and low-pass filter.

Figure 8 Schematics of delay unit, phase detector, charge pump, and low-pass filter.

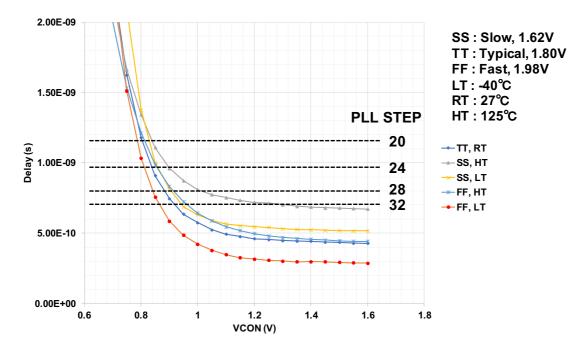

From a view point of Process-Voltage-Temperature (PVT) variation, the prototype v0 may not have enough margin in case of the number of the delay units in the VCRO ("PLL STEP") is 32. Therefore, the propagation delay is reduced by changing the gate length of transistors in the delay units for v1. The expected minimum propagation delay for prototype v1 is 0.45 ns in a typical condition. Figure 9 shows corner simulation of the propagation time of a delay unit for v1. The LPE simulation shows that all conditions cover the delay of PLL STEP = 20-32. PLL STEP of 24 or 28 is assumed for the actual operation. PLL STEPs 20 and 32 provide margin.

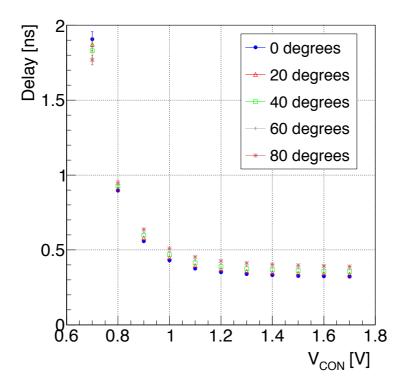

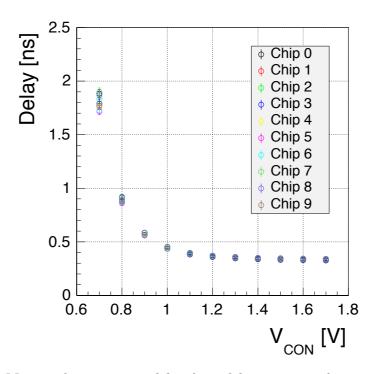

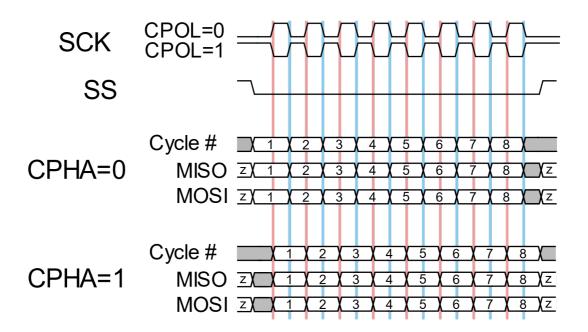

We measured the propagation delay of the signal that passes through a delay unit as a function of  $V_{cos}$ . Figure 10 shows the result of the measurement for chip surface temperatures of 0, 20, 40, 60, and 80 degrees. Sub-nanosecond delay is achieved in all temperature values. Figure 11 shows the propagation delay for ten chips. The variation among the chips is found to be small.

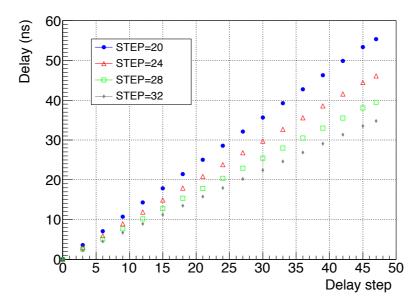

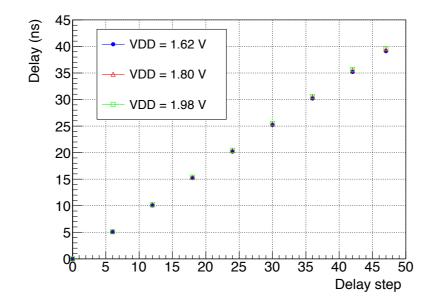

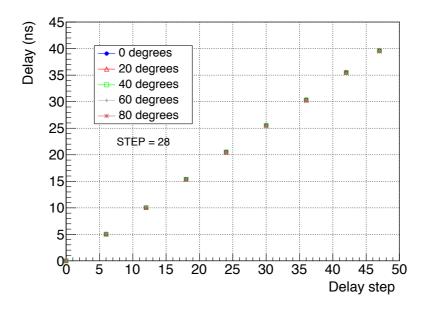

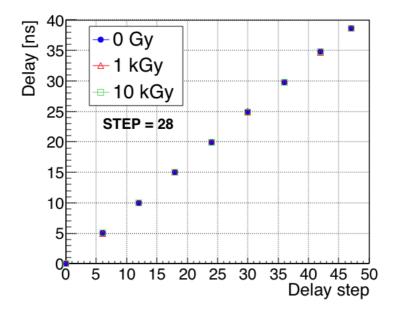

Figure 12 shows the measured delay of the variable delay depending on the number of delay units for a reference clock of 40 MHz. By changing PLL STEP, we can change the dynamic range and the resolution of the variable delay. The resolutions of the variable delay are 0.74 ns, 0.84 ns, 0.99 ns, and 1.19 ns for PLL STEPs 32, 28, 24, and 20, respectively. The dynamic range is derived by multiplying the resolution by 47 (the maximum of the six bit). The results indicate that the variable delay can have a dynamic range of 40 ns with a resolution of sub-nanosecond. Figure 13 shows the measured delay depending on the supply voltage. The delay dependence on the supply voltage is small (< 0.3 ns). The dependence on chip surface temperature is small (Figure 14).

**Figure 9** LPE simulation for the propagation delay of a delay unit. The dashed lines show the delay for PLL STEPs of 20, 24, 28, and 32 assuming reference clock of 40 MHz.

**Figure 10** Measured propagation delay of a delay unit as a function of  $V_{\text{CON}}$ . The delay for chip surface temperatures of 0, 20, 40, 60, and 80 degrees is shown. Sub-nanosecond delay is covered for all temperatures.

**Figure 11** Measured propagation delay for a delay unit as a function of  $V_{\text{CON}}$  for ten chips.

**Figure 12** Measured propagation delay of the variable delay depending on the number of delay units ("delay step"). The results are shown for PLL STEPs 20, 24, 28, and 32.

**Figure 13** The measured propagation delay of the variable delay depending on the number of delay units ("delay step"). The results are shown for supply voltages 1.62 V1.80 V, and 1.98 V. The PLL STEP is set to 28.

**Figure 14** Temperature dependence of the variable delay. The PLL STEP is set to 28.

## 5. BCID

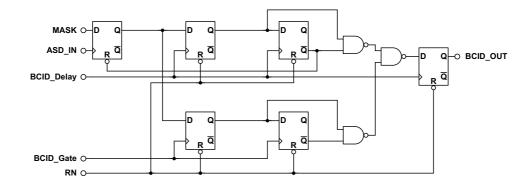

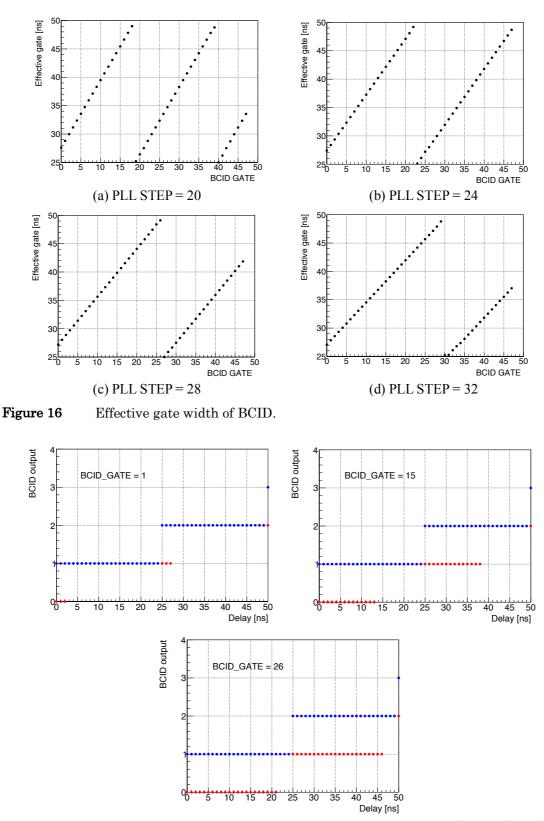

Figure 15 shows a block diagram of the BCID circuit. It contains two delayed clocks: BCID\_Delay and BCID\_Gate as shown in Figures 1 and 15. The BCID\_Delay is used to adjust for the phase difference between the 40 MHz clock on the PS board and the earliest arrival times of signals from the ASD boards. The BCID\_Gate is used to adjust the effective gate width. Set values for each delay are common to a group of 16-channel signals from an ASD board. The BCID circuit has a mask function, which can be set via SPI. Figure 16 shows the effective gate width of BCID circuit for a clock frequency of 40 MHz. The effective gate width was confirmed to cover a range from 25 ns to 49 ns. Figure 17 shows the BCID output for several set values of the BCID\_Delay. Each signal has either one or two BCID outputs depending on the effective gate width. This function makes it possible to assign a hit to either one or two bunch crossings depending on the timing of the hit.

Figure 15 Block diagram of the BCID circuit.

**Figure 17** The measured BCID output for BCID\_Gate values of 1 (top left), 15 (top right), and 26 (bottom). The horizontal axis shows the delay of input signal with respect to the 40 MHz clock, where the offset is subtracted. Each signal has either one or two BCID outputs depending on the effective gate width setting.

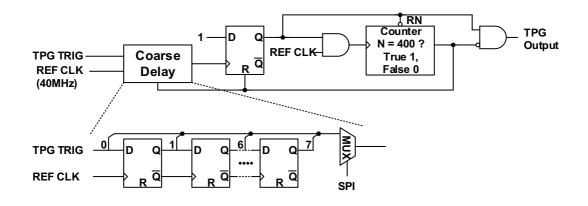

#### 6. Test Pulse Generator

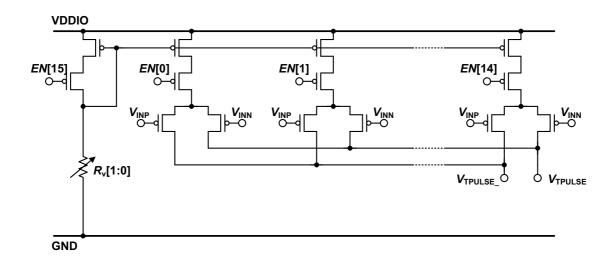

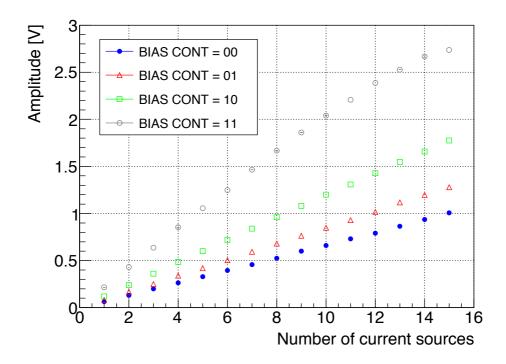

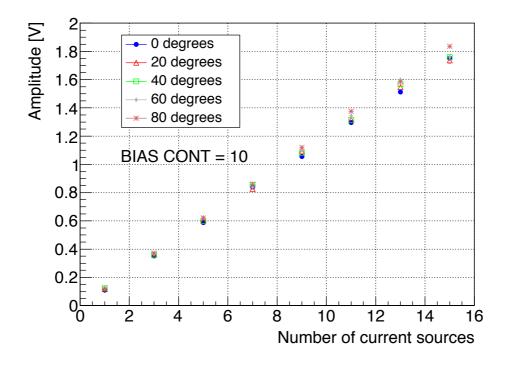

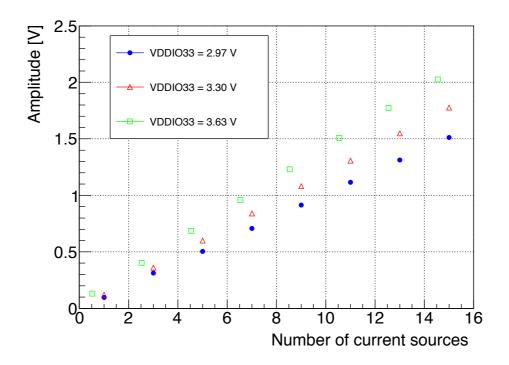

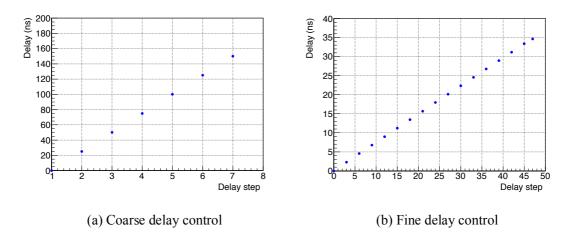

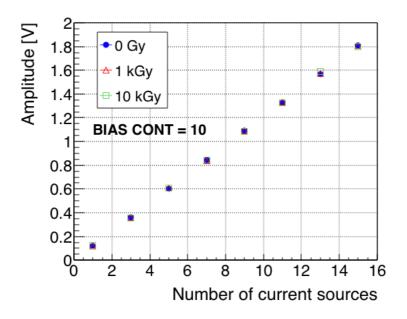

Figure 18 shows a schematic of the test pulse generator. When the ASIC receives a test pulse trigger signal, the test pulse generator outputs a differential square pulse with certain width, which is set via SPI in a range from 25 ns to 102.4  $\mu$ s (12-bit control code, default = 10  $\mu$ s). The amplitude setting is based on 4-bit register (0 to 15) controlled via SPI. The signal of POL defines the polarity of the test pulse. The test pulse trigger signal from outside of the ASIC can be taken with either a rising edge or a falling edge (programmable) of the 40 MHz clock in the ASIC. The delay of the test pulse after receiving a test pulse trigger signal can be programmed with a coarse delay (0 to 7 clocks) and a fine delay (0 ns to 40 ns in the case of PLL STEP = 28). Figure 19 shows a schematic of the output driver part. The amplitude versus the setting is shown in Figure 20, where the amplitude was measured with a load of 100 ohm and 8.0 pF for each output. The amplitude can be changed from 60 mV to 2.8 V. The amplitude used for daily calibration in Run 1 and Run 2 is ~300 mV. A similar value is assumed for Run 4 and the beyond. Figures 21 and 22 show the amplitude dependence on the ambient temperature and the supply voltage. The data indicate that the amplitude depends on supply voltage, while the dependence is safely small for the daily calibration. The coarse and fine delay control is shown in Figure 23.

Figure 18 Schematic of the test pulse generator.

Figure 19 Schematic of the test pulse generator unit.

**Figure 20** Amplitude of the differential output of the test pulse generator with 100 ohm load for each output pin. The values are shown for four bias control values.

**Figure 21** Amplitude of the test pulse generator depending on the number of current sources for various ambient temperature values.

**Figure 22** Amplitude of the test pulse generator depending on the number of current sources for supply voltages of 2.97 V, 3.30 V, and 3.63 V.

Figure 23 Coarse and fine delay of the test pulse generator. PLL STEP is set to 32.

#### 7. Power Consumption

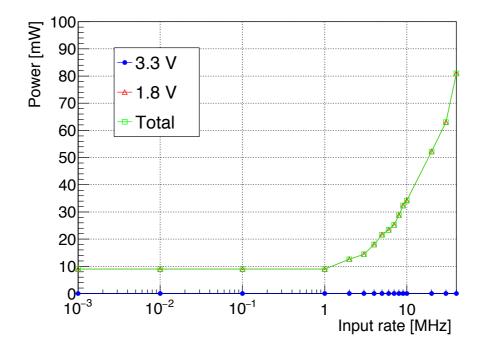

The power consumption was measured as a function of the rate of input signals (Figure 24). The input signals are provided simultaneously to all of the 32 channels of a chip. Test pulse driver is disabled during the measurement. A chip consumes  $\sim 10$  mW under an expected hit rate of  $\sim 0.2$  MHz per channel at a luminosity of 7.5 x  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. Note that the power consumption per chip increases to  $\sim 75$  mW when test pulse driver is enabled and the number of current sources is set to 8 for each of the A and B channels. This result suggests to disable test pulse driver during normal data taking.

Figure 24 Power consumption as a function of the rate of input signal for each channel.

## 8. Yield

The yield has been studied with 200 chips of v1. For all channels of all tested chips, two sets of pulse input, 10 kHz and 10 MHz, were provided, and reasonable output signals were observed. The power consumption was measured with the number of current source set to 2 for each of A and B channels. The measured power consumption for 199 chips ranges from 19 mW to 24 mW (from 44 mW to 49 mW) for 10 kHz (10 MHz) input. The measured power consumption for one chip was significantly higher, 44 mW (71 mW) for 10 kHz (10 MHz) input, and this chip is treated as a bad chip. From these measurements, we conclude that the yield for v1 chips provided from this particular wafer is 99.5%  $\pm$  0.5%.

# 9. Signal I/O Definition

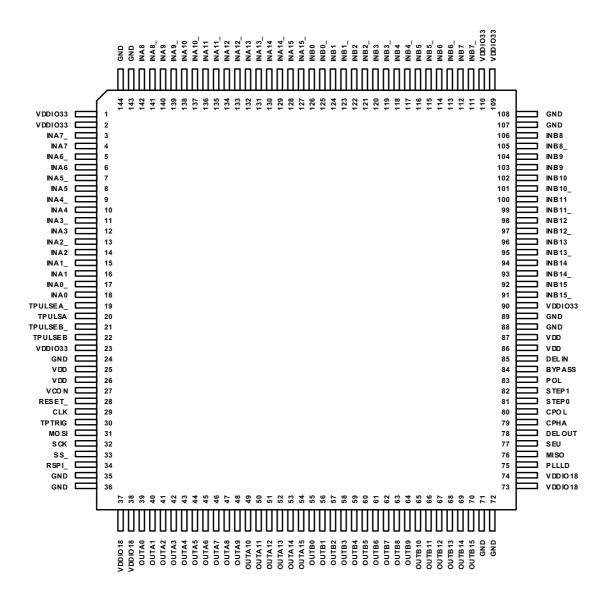

The assignment of the signals and pins are summarized in Figure 25 and Table 1.

| Name             | Pin                                    | Туре    | Signal                                               |  |  |

|------------------|----------------------------------------|---------|------------------------------------------------------|--|--|

| Port-A           |                                        |         |                                                      |  |  |

| INA0             | 18                                     | LVDS IN | Raw LVDS Signals from an ASD Board: 16-channel       |  |  |

| INA 0_           | 17                                     |         | raw LVDS signals from an ASD Board are received      |  |  |

| INA1             | 16                                     |         | by LVDS receivers and are converted to CMOS          |  |  |

| INA1_            | 15                                     |         | level. Further signal processing is decided by POL   |  |  |

| INA2             | 14                                     |         | and BYPASS signals.                                  |  |  |

| INA2_            | 13                                     |         |                                                      |  |  |

| INA3             | 12                                     |         | Signal from anode:                                   |  |  |

| INA3_            | 11                                     |         | INA receives a positive logic signal (hit=H).        |  |  |

| INA4             | 10                                     |         | INA_ receives a negative logic signal (hit=L).       |  |  |

| INA4_            | 9                                      |         | Signal from cathode:                                 |  |  |

| INA5             | 8                                      |         | INA receives a negative logic signal (hit=L).        |  |  |

| INA5_            | 7                                      |         | INA_ received a positive logic signal (hit=H).       |  |  |

| INA6             | 6                                      |         |                                                      |  |  |

| INA6_            | 5                                      |         | POL = L                                              |  |  |

| INA7             | 4                                      |         | Raw signals from anode wires.                        |  |  |

| INA7_            | 3                                      |         | Output signals from LVDS receivers are not           |  |  |

| INA8             | 142                                    |         | inverted.                                            |  |  |

| INA8_            | 141                                    |         | POL = H                                              |  |  |

| INA9             | 140                                    |         | Raw signals from strips                              |  |  |

| INA9_            | 139                                    |         | Output signals from LVDS receivers are               |  |  |

| INA10            | 138                                    |         | inverted.                                            |  |  |

| INA10_           | 137                                    |         |                                                      |  |  |

| INA11            | 136                                    |         | BYPASS = L                                           |  |  |

| INA11_           | 135                                    |         | Signals are fad to variable delay circuits and       |  |  |

| INA12            | 134                                    |         | then bunch-identification circuits.                  |  |  |

| INA12_           | 133                                    |         | BYPASS = H                                           |  |  |

| INA13            | 132                                    |         | Signals are fad to outputs as OUTA signals           |  |  |

| INA13_           | 131                                    |         | directly. Neither variable delay circuit nor         |  |  |

| INA14            | 130                                    |         | bunch-identification circuit.                        |  |  |

| INA14_           | 129                                    |         |                                                      |  |  |

| INA15            | 128                                    |         |                                                      |  |  |

| INA15_           | 127                                    | CIMOC   |                                                      |  |  |

| OUTA0            | 39                                     | CMOS    | Hit Signals: 16-bit hit signals are output. Positive |  |  |

| OUTA1            | 40                                     | OUT     | logic.                                               |  |  |

| OUTA2            | 41                                     |         | BYPASS=L                                             |  |  |

| OUTA3            | 42                                     |         |                                                      |  |  |

| OUTA4            | 43                                     |         | Bunch-identified hit signals are output.             |  |  |

| OUTA5            | 44                                     |         | BYPASS=H                                             |  |  |

| OUTA6<br>OUTA7   | 45                                     |         | Asynchronous hit signals are output.                 |  |  |

|                  | 46                                     |         |                                                      |  |  |

| OUTA8<br>OUTA9   | $\begin{array}{c} 47\\ 48 \end{array}$ |         |                                                      |  |  |

| OUTA9<br>OUTA10  | $48 \\ 49$                             |         |                                                      |  |  |

| OUTA10<br>OUTA11 | $\frac{49}{50}$                        |         |                                                      |  |  |

| OUTA11<br>OUTA12 | $\frac{50}{51}$                        |         |                                                      |  |  |

| OUTA12<br>OUTA13 | 51<br>52                               |         |                                                      |  |  |

|                  | $\frac{52}{53}$                        |         |                                                      |  |  |

| OUTA14           | <b>ə</b> ð                             |         |                                                      |  |  |

Table 1Signal I/O definition of Patch-Panel ASIC.

| OUTA15   | 54  |            |                                                        |

|----------|-----|------------|--------------------------------------------------------|

| TPULSEA  | 20  | Open-Drain | Test Pulse Output Signal to an ASD Board: Test         |

| TPULSEA_ | 19  | OUT        | pulse is output to an ASD Board. The signal is         |

|          | 10  | 001        | differential. The amplitude and the delay from         |

|          |     |            | TPTRG can be set via SPI. The pulse width is $3 \mu s$ |

|          |     |            | (fixed value, to be defined).                          |

|          |     |            | (incu value, to be defined).                           |

|          |     |            | POL=L (anode)                                          |

|          |     |            | TPULSEA is a positive logic signal.                    |

|          |     |            | TPULSEA_ is a negative logic signal.                   |

|          |     |            | POL=H (cathode)                                        |

|          |     |            | TPULSEA is a negative logic signal.                    |

|          |     |            | TPULSEA_ is a positive logic signal.                   |

| Port-B   |     |            |                                                        |

| INB0     | 126 | LVDS IN    | Raw LVDS Signals from an ASD Board: 16-channel         |

| INB0_    | 125 |            | raw LVDS signals from an ASD Board are received        |

| INB1     | 124 |            | by LVDS receivers and are converted to CMOS            |

| INB1_    | 123 |            | level. Further signal processing is decided by POL     |

| INB2     | 122 |            | and BYPASS signals.                                    |

| INB2_    | 121 |            |                                                        |

| INB3     | 120 |            | Signal from anode:                                     |

| INB3_    | 119 |            | INB receives a positive logic signal (hit=H).          |

| INB4     | 118 |            | INB_ receives a negative logic signal (hit=L).         |

| INB4_    | 117 |            | Signal from cathode:                                   |

| INB5     | 116 |            | INB receives a negative logic signal (hit=L).          |

| INB5_    | 115 |            | INB_ received a positive logic signal (hit=H).         |

| INB6     | 114 |            |                                                        |

| INB6_    | 113 |            | POL = L                                                |

| INB7     | 112 |            | Raw signals from anode wires.                          |

| INB7_    | 111 |            | Output signals from LVDS receivers are not             |

| INB8     | 106 |            | inverted.                                              |

| INB8_    | 105 |            | POL = H                                                |

| INB9     | 104 |            | Raw signals from strips                                |

| INB9_    | 103 |            | Output signals from LVDS receivers are                 |

| INB10    | 102 |            | inverted.                                              |

| INB10_   | 101 |            |                                                        |

| INB11    | 100 |            | BYPASS = L                                             |

| INB11_   | 99  |            | Signals are fad to variable delay circuits and         |

| INB12    | 98  |            | then bunch-identification circuits.                    |

| INB12_   | 97  |            | BYPASS = H                                             |

| INB13    | 96  |            | Signals are fad to outputs as OUTA signals             |

| INB13_   | 95  |            | directly. Neither variable delay circuit nor           |

| INB14    | 94  |            | bunch-identification circuit.                          |

| INB14_   | 93  |            |                                                        |

| INB15    | 93  |            |                                                        |

| INB15_   | 91  |            |                                                        |

| OUTB0    | 55  | CMOS       | Hit Signals: 16-bit hit signals are output. Positive   |

| OUTB1    | 56  | OUT        | logic.                                                 |

| OUTB2    | 57  |            |                                                        |

| OUTB3    | 58  |            | BYPASS=L                                               |

| OUTB4    | 59  |            | Bunch-identified hit signals are output.               |

| OUTB5               | 60       |                   | BYPASS=H                                                                                                                                                                                                                         |

|---------------------|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTB6               | 61       |                   | Asynchronous hit signals are output.                                                                                                                                                                                             |

| OUTB7               | 61       |                   | risynom onous int signais are output.                                                                                                                                                                                            |

| OUTB8               | 63       |                   |                                                                                                                                                                                                                                  |

|                     | 63<br>64 |                   |                                                                                                                                                                                                                                  |

| OUTB9               |          |                   |                                                                                                                                                                                                                                  |

| OUTB10              | 65       |                   |                                                                                                                                                                                                                                  |

| OUTB11              | 66       |                   |                                                                                                                                                                                                                                  |

| OUTB12              | 67       |                   |                                                                                                                                                                                                                                  |

| OUTB13              | 68       |                   |                                                                                                                                                                                                                                  |

| OUTB14              | 69       |                   |                                                                                                                                                                                                                                  |

| OUTB15              | 70       |                   |                                                                                                                                                                                                                                  |

| TPULSEB<br>TPULSEB_ | 22<br>21 | Open-Drain<br>OUT | Test Pulse Output Signal to an ASD Board: Test pulse is output to a ASD Board. The signal is differential. The amplitude and the delay from TPTRG can be set via SPI. The pulse width is $3 \mu s$ (fixed value, to be defined). |

|                     |          |                   | POL=L (anode)<br>TPULSEA is a positive logic signal.<br>TPULSEA_ is a negative logic signal.<br>POL=H (cathode)<br>TPULSEA is a negative logic signal.<br>TPULSEA_ is a positive logic signal.                                   |

| COMMON              |          | •                 |                                                                                                                                                                                                                                  |

| DELIN               | 85       | CMOS IN           | <b>Input Signal to Variable Delay:</b> The input signal is delayed in the Variable Delay circuit. The delay can be set via SPI.                                                                                                  |

| DELOUT              | 78       | CMOS<br>OUT       | <b>Output Signal from Variable Delay:</b> The delayed signal from the Variable Delay circuit. The delay can be set via SPI.                                                                                                      |

| POL                 | 83       | CMOS IN           | <b>Signal Polarity:</b> Polarity selection of raw input signals.                                                                                                                                                                 |

|                     |          |                   | POL = L                                                                                                                                                                                                                          |

|                     |          |                   |                                                                                                                                                                                                                                  |

|                     |          |                   | Raw LVDS signals from a wire ASD Board.                                                                                                                                                                                          |

|                     |          |                   | POL = H                                                                                                                                                                                                                          |

|                     | - ·      |                   | Raw LVDS signals from a strip ASD Board.                                                                                                                                                                                         |

| BYPASS              | 84       | CMOS IN           | <b>Bypass of Variable Delay and BCID:</b> Selection of bunch-identification mode or bypass mode.                                                                                                                                 |

|                     |          |                   | DVDACC - I                                                                                                                                                                                                                       |

|                     |          |                   | BYPASS = L                                                                                                                                                                                                                       |

|                     |          |                   | Signals are fad to variable delay circuits and                                                                                                                                                                                   |

|                     |          |                   | then bunch-identification circuits.                                                                                                                                                                                              |

|                     |          |                   | BYPASS = H                                                                                                                                                                                                                       |

|                     |          |                   | Signals are fad to outputs as OUTA signals                                                                                                                                                                                       |

|                     |          |                   | directly. Neither variable delay circuit nor                                                                                                                                                                                     |

|                     |          |                   | bunch-identification circuit.                                                                                                                                                                                                    |

| CLK                 | 29       | CMOS IN           | System Clock: 40 MHz system clock from TTC Rx.                                                                                                                                                                                   |

| TPTRIG              | 30       | CMOS IN           | Test Pulse Trigger: Test pulse trigger signal from                                                                                                                                                                               |

|                     |          |                   | TTC Rx. Positive logic. The signal is taken at a                                                                                                                                                                                 |

|                     |          |                   | rising edge of CLK.                                                                                                                                                                                                              |

| <u> </u>            |          |                   |                                                                                                                                                                                                                                  |

| SEU      | 77                                    | CMOS               | Single Event Unget signal: Single quant unget is                                   |  |  |  |  |

|----------|---------------------------------------|--------------------|------------------------------------------------------------------------------------|--|--|--|--|

| SEU      | 11                                    | OUT                | <b>Single Event Upset signal:</b> Single event upset is detected in SPI registers. |  |  |  |  |

|          |                                       | 001                | SEU = $H$ : SEU is detected.                                                       |  |  |  |  |

|          |                                       |                    | SEU = L: SEU is not detected.                                                      |  |  |  |  |

| RESET_   | 28                                    | CMOS IN            | System Reset: System Reset signal from TTC Rx.                                     |  |  |  |  |

| NESEI_   | 20                                    | CINOS IN           | Negative logic. The signal sets all registers defaults.                            |  |  |  |  |

| PLL      |                                       |                    | Negative logic. The signal sets an registers defaults.                             |  |  |  |  |

| PLLLD    | 75                                    | CMOS               | PLL Lock status: PLL lock detection signal                                         |  |  |  |  |

| I LLLD   | 10                                    | OUT                | PLLLD=L Unlocked.                                                                  |  |  |  |  |

|          |                                       | 001                | PLLLD=H Locked.                                                                    |  |  |  |  |

| STEP0    | 81                                    | CMOS IN            | PLL Depth: Setting of the number of delay units in                                 |  |  |  |  |

| STEP1    | 82                                    |                    | the ring oscillator of the PLL                                                     |  |  |  |  |

| DIDI I   | 02                                    |                    | STEP=0: 32                                                                         |  |  |  |  |

|          |                                       |                    | STEP=1: 28                                                                         |  |  |  |  |

|          |                                       |                    | STEP=2: 24                                                                         |  |  |  |  |

|          |                                       |                    | STEP=3: 20                                                                         |  |  |  |  |

| VCON     | 27                                    |                    | <b>Control Voltage:</b> DC voltage to control delay units.                         |  |  |  |  |

|          |                                       |                    | An R/C network for the low pass filter shall be                                    |  |  |  |  |

|          |                                       |                    | connected to the pin.                                                              |  |  |  |  |

| SPI      |                                       | <u> </u>           |                                                                                    |  |  |  |  |

| MOSI     | 31                                    | CMOS IN            | Master Out Slave In: Input Data signal of SPI.                                     |  |  |  |  |

| SS_      | 33                                    | CMOS IN            | Slave Select: Slave Select signal of SPI.                                          |  |  |  |  |

| SCK      | 32                                    | CMOS IN<br>CMOS IN | Serial Clock: Serial Clock signal of SPI.                                          |  |  |  |  |

| MISO     | 76                                    | CMOS IN            | Master In Slave Out: Output data signal of SPI.                                    |  |  |  |  |

|          |                                       | OUT                |                                                                                    |  |  |  |  |

| CPOL     | 80                                    | CMOS IN            | Configuration signals of SPI: Polarity and edge                                    |  |  |  |  |

| CPHA     | 79                                    |                    | selection of SCK. See Appendix 1.                                                  |  |  |  |  |

| RSPI_    | 34                                    | CMOS IN            | SPI Reset: SPI reset. Negative logic. The signal sets                              |  |  |  |  |

|          |                                       |                    | all registers defaults (See section 9).                                            |  |  |  |  |

| POWER    |                                       |                    |                                                                                    |  |  |  |  |

| GND      | 24                                    |                    | Ground: 0 volts.                                                                   |  |  |  |  |

|          | 35                                    |                    |                                                                                    |  |  |  |  |

|          | 36                                    |                    |                                                                                    |  |  |  |  |

|          | 71                                    |                    |                                                                                    |  |  |  |  |

|          | 72                                    |                    |                                                                                    |  |  |  |  |

|          | 88                                    |                    |                                                                                    |  |  |  |  |

|          | 89<br>107                             |                    |                                                                                    |  |  |  |  |

|          | 107                                   |                    |                                                                                    |  |  |  |  |

|          | 108                                   |                    |                                                                                    |  |  |  |  |

|          | 143                                   |                    |                                                                                    |  |  |  |  |

| VDD      | 144                                   |                    |                                                                                    |  |  |  |  |

| VDD      | 25<br>26                              |                    | <b>Power:</b> 1.8 volts for core circuits.                                         |  |  |  |  |

|          | 26<br>80                              |                    |                                                                                    |  |  |  |  |

|          | 86<br>87                              |                    |                                                                                    |  |  |  |  |

| VDDIO33  | 87                                    |                    | <b>Power:</b> 3.3 volts for IO circuits.                                           |  |  |  |  |

| 4 001099 | $\begin{array}{c} 1 \\ 2 \end{array}$ |                    | rower. 5.5 voits for 10 circuits.                                                  |  |  |  |  |

|          |                                       |                    |                                                                                    |  |  |  |  |

|          | 23                                    |                    |                                                                                    |  |  |  |  |

|          | 90                                    |                    |                                                                                    |  |  |  |  |

|          | 109                                   |                    |                                                                                    |  |  |  |  |

|          | 110                                   | L                  |                                                                                    |  |  |  |  |

| VDDIO18 | 37 | <b>Power:</b> 1.8 volts for IO circuits. |

|---------|----|------------------------------------------|

|         | 38 |                                          |

|         | 73 |                                          |

|         | 74 |                                          |

# **10.** Control

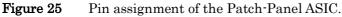

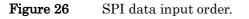

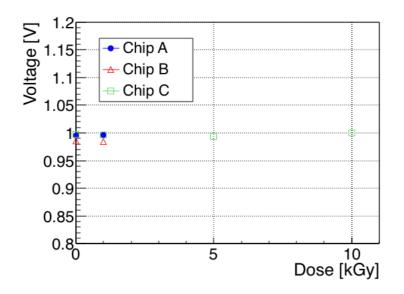

Most of the control are based on SPI protocol. The instruction is given in Table 2. A Patch-Panel ASIC covers two 16-channel ASD boards (Channels A and B), and one can set parameters for each part independently. The voting logic is introduced to the data registers in order to cope with the radiation immunity against single event upset. Figure 26 shows the data input order of SPI. Figure 27 shows basic information of the SPI protocol.

Table 2Patch-Panel ASIC SPI Instructions(a) Channel A and B (12 byte / each)

| N am e            | #ofbit | In it ia I cond it ion | Function                                                            | Rem arks                                               | Address   |

|-------------------|--------|------------------------|---------------------------------------------------------------------|--------------------------------------------------------|-----------|

| DL_POL            | 16     | ALL O                  | De kay line pokarity con trol<br>0 :n on − in verted, 1 : in verted | External cotrolpin<br>can be used.<br>Default:External | < 15:0>   |

| DL_BYPASS         | 16     | ALL 1                  | Delay line bypass control<br>O'non-bypass, 1 bypass                 | External cotrolpin<br>can be used.<br>Default:External | < 31 :16> |

| DL_MASK           | 16     | ALL 1                  | Delay line m ask control<br>Om asked, 1 non-m asked                 |                                                        | < 47 32>  |

| DL_DLY_CONT       | 6      | 101111                 | Delay line delay control<br>000000 (m in)-101111 (m ax)             | 1ns step<br>(PLL dependent)                            | < 53 :48> |

| TEST_POL          | 1      | 0                      | Test in put pokalrity con trol<br>0 'n on − in verted, 1 ∶in verted | External cotrolpin<br>can be used.<br>Default:External | < 54>     |

| TEST_DLY_CONT     | 6      | 101111                 | Test input de lay con tro l<br>000000 (m in)-101111 (m ax)          | 1ns step<br>(PLL dependent)                            | < 60 55>  |

| TPG_POL_ <b>N</b> | 1      | 0                      | TPG TRLG edge control<br>O∶rising edge, 1∶falling edge              |                                                        | < 61>     |

| TPG_POL_OUT       | 1      | 0                      | TPG outputpolarity control<br>0:positive, 1:negative                |                                                        | < 62>     |

| TPG_DLY_CONT_C    | 3      | 111                    | TPG coarse de lay control<br>000 (m in)-111 (m ax)                  | 1 CLK step (25ns)                                      | < 65:63>  |

| TPG_DLY_CONT_F    | 6      | 101111                 | TPG fine de lay control<br>000000 (m in)-101111 (m ax)              | 1ns step<br>(PLL dependent)                            | < 71 :66> |

| TPG_PW_CONT       | 12     | 000110010000           | TPG pulsewidth control<br>ALLO(min)-ALL1(max)                       | 1 CLK step (25ns)<br>In itia l: 10us                   | < 83 :72> |

| BCD_DLY_CONT      | 6      | 000000                 | BCD delay control<br>000000 (m in)-101111 (m ax)                    | 1ns step<br>(PLL dependent)                            | < 89 :84> |

| BCD_GATE_CONT     | 6      | 000000                 | BCD gate control<br>000000(m in)-101111(m ax)                       | 1ns step<br>(PLL dependent)                            | < 95 :90> |

(b) PLL (1 byte)

| N am e       | #ofbit | In itia I cond ition | Function                | Rem arks               | Address |

|--------------|--------|----------------------|-------------------------|------------------------|---------|

| PLL_DLY_CONT | 5      | 11111                | PLL de lay line control | 11111 (32),11011 (28)  | < 4 :0> |

|              |        |                      | 00000(m in)-11111(m ax) | 10111 (24), 10011 (20) |         |

| PLL_CP_CONT  | 2      | 01                   | CP bias current control |                        | < 6 :5> |

|              |        |                      | 00(m in)-11(m ax)       |                        |         |

| PLL_CP_0N    |        | 1                    | CP Enable               | In case of 0, VCON is  | < 7>    |

|              | 1      |                      | 1 Enable, 0 D isable    | floating.              |         |

(c) Common (3 byte)

| Name           | # of bit | In it ia I cond it ion | Function                        | Rem arks            | Address  |

|----------------|----------|------------------------|---------------------------------|---------------------|----------|

| PLL_DLY_SEL    | 1        | 1                      | PLL de lay line control code    |                     | < 0>     |

| FLL_DLI_3LL    | 1        |                        | EXT(1)/ <b>N</b> T(0) select    |                     | < 0>     |

| DL_POL_SEL     | 1        | 1                      | D e lay line po larity contro l |                     | <1>      |

|                |          | I                      | EXT(1)/ <b>N</b> T(0) select    |                     | × 17     |

| DL_BYPASS_SEL  | 1        | 1                      | D e lay line po larity contro l |                     | < 2>     |

| DL_DIFA33_3LL  | 1        | I                      | EXT(1)/ <b>N</b> T(0) select    |                     | \Z/      |

| TPG DRV CONT A | 4        | 0000                   | TPG_A D rivab ility con tro l   | 0000:TPG Driver is  | < 6:3>   |

|                | 4        | 0000                   | 0000(m in)-1111(m ax)           | d isab led          | < 0.3/   |

| TPG DRV CONT B | 4        | 0000                   | TPG_B D rivab ility con tro l   | 0000:TPG Driver is  | < 10:7>  |

|                |          |                        | 0000(m in)-1111(m ax)           | d isab led          |          |

| TPG BIAS CONT  | 2        | 00                     | TPG Bias current control        | 0.5, 0.75, 1.0, 2.0 | <12:11>  |

|                |          |                        | 00 (m in)-11 (m ax)             |                     |          |

| TPG BIAS ENB   | 1        | 0                      | TPG Bias Enable                 |                     | <13>     |

|                |          | U                      | 0∶Bias En able 1∶Disable        |                     |          |

| RX BIAS CONT   | 2        | 10                     | LVDS(Rx)Biascurrent             | 0.5, 0.75, 1.0, 2.0 | < 15:14> |

|                | 2        |                        | control00(m in)-11(m ax)        | 0.0, 0.70, 1.0, 2.0 |          |

| CM OS OUT CONT | 2        | 01                     | CM OSD rivability control       | 0.5, 1.0, 1.5, 2.0  | < 17:16> |

|                |          |                        | 00(m in)-11(m ax)               | 0.0, 1.0, 1.0, 2.0  | × 17.10/ |

| N C            | 6        | 000000                 | N on-connect                    | reserve             | < 23:18> |

- Circuit order

- − Common $\rightarrow$ PLL $\rightarrow$ Channel A $\rightarrow$ Channel B

- Data input order

– Channel B $\rightarrow$ Channel A $\rightarrow$ PLL $\rightarrow$ Common, MSB First

Ex.) For PLL

**Figure 27** SPI mode and timing chart taken from Wikipedia (https://en.wikipedia.org/wiki/Serial\_Peripheral\_Interface\_Bus).

### 11. Radiation Tolerance for Total Ionizing Dose

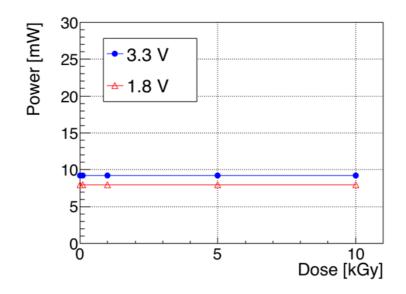

The Patch-Panel ASIC produced for the ATLAS experiment at HL-LHC shall have the radiation tolerance sufficient for the use in the experimental cavern during the whole duration of the machine operation. The requirement on the total ionizing dose is 27 Gy. This value is obtained from a product of the simulated radiation level (6 Gy) and the safety factor (4.5). The radiation level has been simulated with FLUGG for an integrated luminosity of 4000 fb<sup>-1</sup>. The value for a radial coordinate of 8 m, the innermost region of the Patch-Panel ASIC location, has been extracted. The safety factor for the difference in the dose rate between the test and the actual experiment (1.5), and the safety factor for the variations of radiation tolerance from lot to lot and within lots (2).

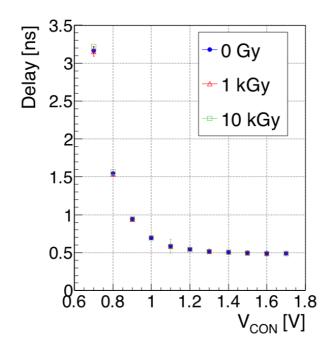

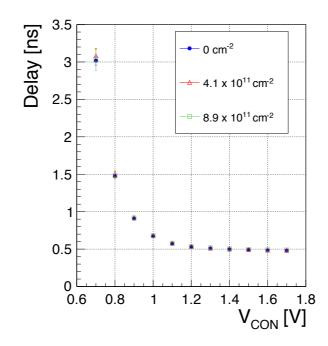

Three prototype chips of the Patch-Panel ASIC produced in 2018 were irradiated, and no degradation of the performance was observed. The test was performed at the Cobalt-60 facility of Nagoya University in Japan. The three chips were irradiated up to 1 kGy. One chip among the three was further irradiated up to 10 kGy. The dose rate was 8.2 Gy/min. Figures 28-30 show the test results for PLL and variable-delay blocks. No significant change was observed in the relations between the control voltage and the delay. The frequency of the reference clock for which PLL is locked ranges from 28-31 MHz to 57-58 MHz. This range covers the frequency for the actual operation 40 MHz with margin. Figure 31 shows the test result for the test pulse generator. The linearity was unchanged by the irradiation. Figure 32 shows the power consumption depending on the dose. No significant increase was observed. For all tests, no failure was observed in the chip control with SPI.

**Figure 28** Relation between the control voltage  $V_{cos}$  and the measured delay of a delay unit for total ionizing doses of 0 Gy, 1 kGy, and 10 kGy. The result is shown for one prototype chip (v0).

**Figure 29** The control voltage  $V_{\alpha s}$  for the PLL circuit locked with a reference clock of 40 MHz depending on the ionizing dose. The result is shown for three prototype chips (v0). One of them is irradiated up to 10 kGy, while the other two up to 1 kGy.

**Figure 30** Relation between the setup of the number of delay units ("delay step") and the measured delay of the variable delay for total ionizing doses of 0 Gy, 1 kGy, and 10 kGy. The result is shown for one prototype chip (v0).

**Figure 31** The amplitude of the test pulse generator output depending on the number of current sources for total ionizing doses of 0 Gy, 1 kGy, and 10 kGy. The result is shown for one prototype chip (v0).

**Figure 32** The power consumption depending on the ionizing dose. The result is shown for one prototype chip (v0).

### 12. Radiation Tolerance for Non-Ionizing Energy Loss

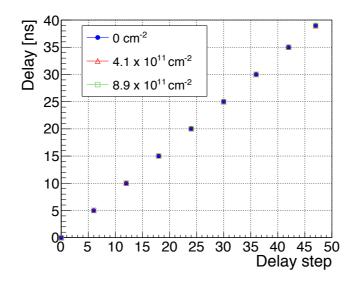

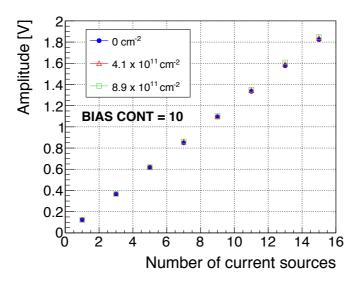

The Patch-Panel ASICs are pure CMOS devices, and the ATLAS rule does not require the test of non-ionizing energy loss (NIEL). However, we held a neutron irradiation test for confirmation. Neutrons were irradiated at the tandem electrostatic accelerator at Kobe University in Japan. We acknowledge A. Ochi and Y. Mori, both from Kobe University, for various supports for the operation of the accelerator. Estimated total number of neutrons is 8.9 x  $10^{11}$  cm<sup>-2</sup>. The energy distribution of the neutrons has a peak at around 2 MeV. The energy loss of neutrons with 2 MeV is similar to that of 1 MeV. We evaluated the performances of PLL, variable delay, and test pulse generator. No degradation of the performance was observed (Figures 33, 34, and 35).

**Figure 33** Relation between the control voltage  $V_{cos}$  and the measured delay of a delay unit for neutron flux up to 8.9 x 10<sup>11</sup> cm<sup>-2</sup>. The result is shown for one prototype chip (v0).

**Figure 34** Relation between the setup of the number of delay units ("delay step") and the measured delay of the variable delay for neutron flux up to  $8.9 \times 10^{11}$  cm<sup>-2</sup>. The result is shown for one prototype chip (v0).

**Figure 35** Amplitude of the test pulse generator output depending on the number of current sources for neutron flux up to  $8.9 \times 10^{11}$  cm<sup>-2</sup>. The result is shown for one prototype chip (v0).

#### 13. Radiation Tolerance for Single Event Effect

The Patch-Panel ASICs have voting logic for the registers as described in Section 10, and would have a high tolerance to the single event effect. The TGC system has multiple layers and the coincidence provides robustness for trigger. Therefore, single bit flip for signal data has negligible impact on the trigger performance.