# 先端エレクトロニクスDAQセミナーアナログ・デジタル変換技術 2020/07/29

高エネルギー加速器研究機構 素粒子原子核研究所 宮原 正也

### 自分が作る計測機器で必要となるADCの選定、評価ができるくらいを目指します。

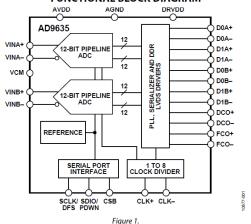

ANALOG Dual, 12-Bit, 80 MSPS/125 MSPS, Serial LVDS 1.8 V Analog-to-Digital Converter

AD9635 **Data Sheet**

#### **FEATURES**

1.8 V supply operation

Low power: 115 mW per channel at 125 MSPS with scalable power options

SNR = 71 dBFS (to Nyquist)

SFDR = 93 dBc at 70 MHz

DNL = -0.1 LSB to +0.2 LSB (typical); INL =  $\pm 0.4$  LSB (typical)

Serial LVDS (ANSI-644, default) and low power, reduced range option (similar to IEEE 1596.3)

650 MHz full power analog bandwidth

2 V p-p input voltage range

Serial port control

Full chip and individual channel power-down modes

Flexible bit orientation

Built-in and custom digital test pattern generation

Clock divider

Programmable output clock and data alignment

Programmable output resolution

Standby mode

#### APPLICATIONS

Communications

Diversity radio systems

Multimode digital receivers

GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA

I/Q demodulation systems

Smart antenna systems

**Broadband data applications**

**Battery-powered instruments**

Handheld scope meters

Portable medical imaging and ultrasound

Radar/LIDAR

#### **GENERAL DESCRIPTION**

The AD9635 is a dual, 12-bit, 80 MSPS/125 MSPS analog-to-

#### **FUNCTIONAL BLOCK DIAGRAM**

The ADC automatically multiplies the sample rate clock for the appropriate LVDS serial data rate. A data clock output (DCO) for capturing data on the output and a frame clock output (FCO) for signaling a new output byte are provided. Individual channel power-down is supported; the AD9635 typically consumes less than 2 mW in the full power-down state. The ADC provides several features designed to maximize flexibility and minimize system cost, such as programmable output clock and data alignment and digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).

The AD9635 is available in a RoHS-compliant, 32-lead LFCSP. It is specified over the industrial temperature range of -40°C to ±8500

http://www.analog.com/media/en/technical-documentation/data-sheets/AD9635.pdf

- 1. ADCの基本機能

- 量子化

- サンプリング定理

- 2. ADCの性能表現

- 3. ADCの主要な変換方法

- 変換アーキテクチャの概要とトレンド

- 4. ADCの設計例

- SAR ADC

- 5. ADCの評価方法

- アナログ・デジタル変換器(ADC)とは

- アナログ信号をデジタル信号に変換する回路

- アナログ信号: 自然界の信号

- デジタル信号: デジタル世界の信号

- ADCは異世界をつなぐインターフェース

- 両世界が存在し、両世界をつなぐ必要性がある限り永遠 に必要とされる回路。

デジタル信号

### ADCの基本機能

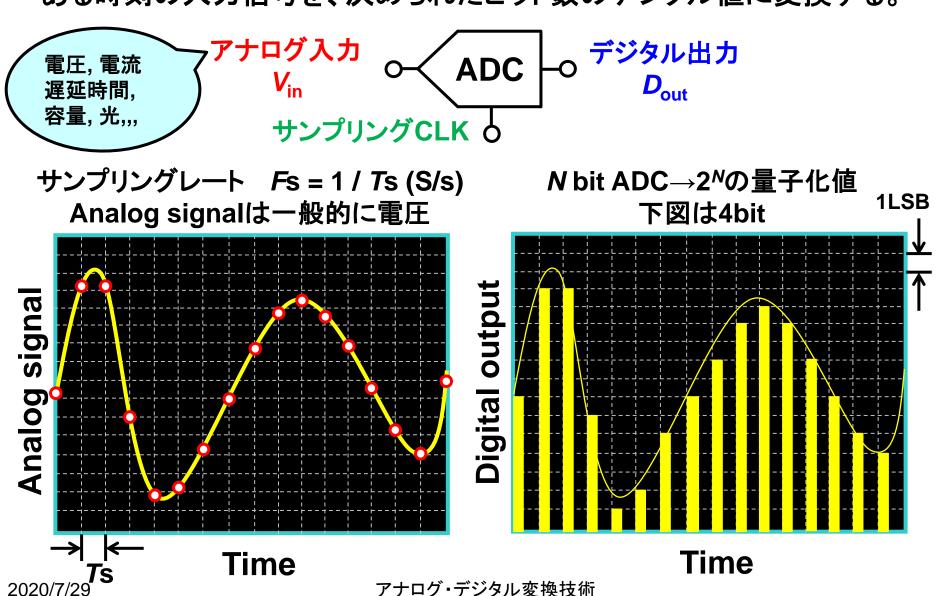

ある時刻の入力信号を、決められたビット数のデジタル値に変換する。

- デジタル回路は2進数を取り扱う

- ADCの出力も2進数で出力される

- ADCの分解能:N bit → 2<sup>N</sup> の階調を持つ

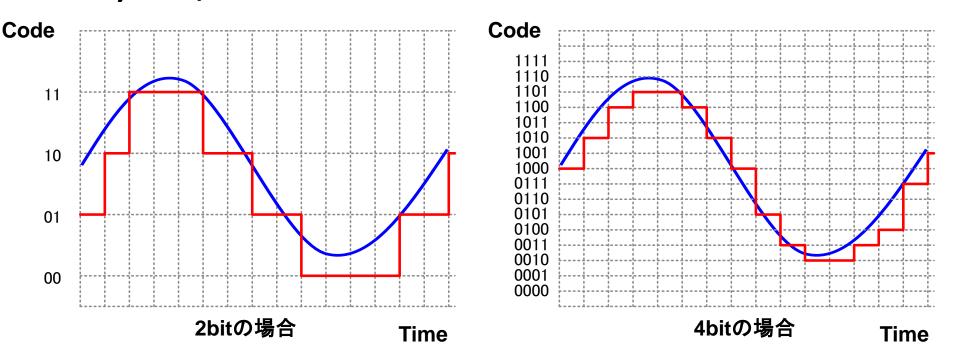

Ex.) 2bit, 4bit分解能のADC

高い分解能を持つほど信号の再現度は高い

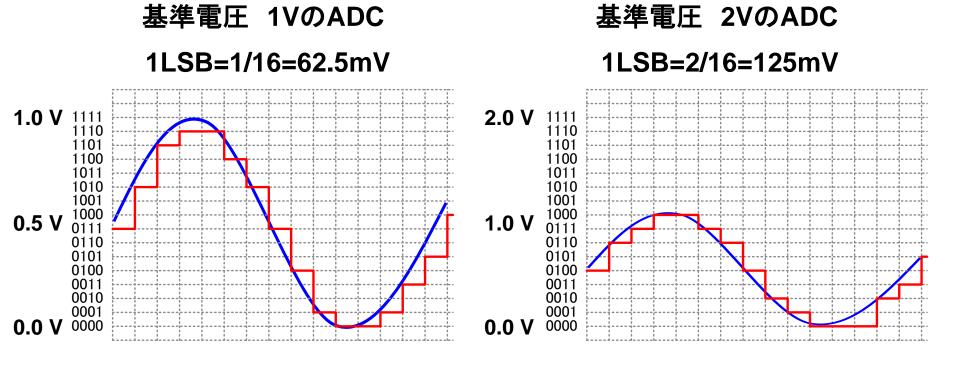

- ADCの入力範囲を決定するために基準となる信号が必要

- Ex.) 1Vp-pの振幅の信号を異なる基準電圧のADCに入力

基準信号が異なれば、同じコードでも表す物理量は異なる。

- アプリケーションの要求によって必要な分解能 は異なる

- 必要な階調 = 測定レンジ/最小感度

- 必要なビット数=log2(必要な階調)

- Ex.) -100°C~100°Cの温度を測りたい!

- •1℃の精度で測りたい場合

- (Max Min) / Step = (100- (-100)) /1 =200 » log₂(200) = 7.64 → 8bit以上のADCが必要

- 0.1℃の精度で測りたい場合

- (Max Min) / Step = (100- (-100)) / 0.1 = 2000 » log<sub>2</sub>(2000) = 10.97 → 11bit以上のADCが必要

実際は測定マージンやノイズなどの影響を考慮して十分余裕を持った分解能のADCを使用する必要がある。

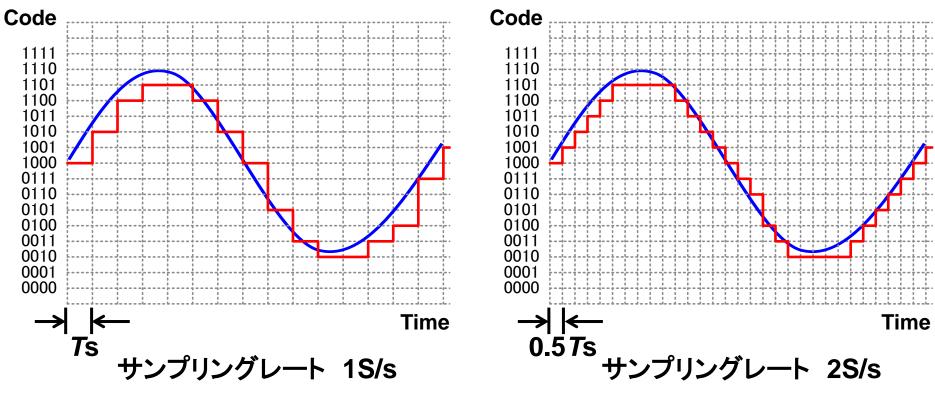

- ADCはある決められた時刻の信号をサンプリングする

- サンプリングタイミングを与えるために基準CLKを入力する

サンプリングレート Fs = 1 / Ts (S/s)

高サンプリングレートほど信号の再現度は高い

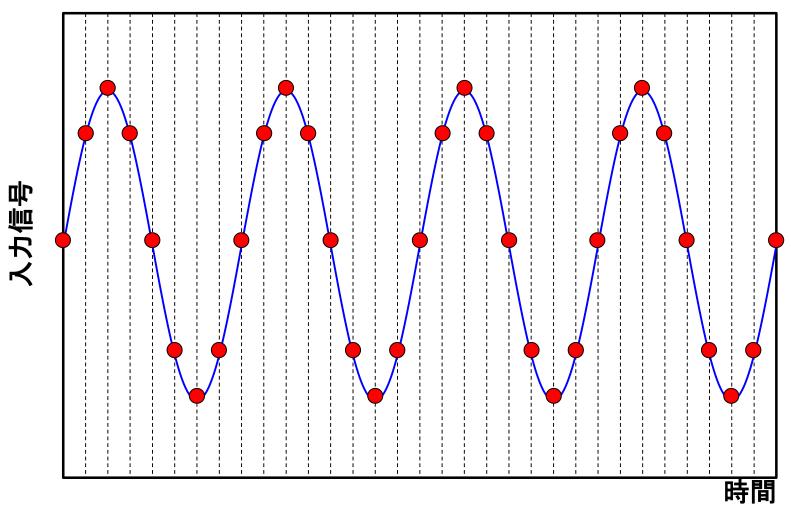

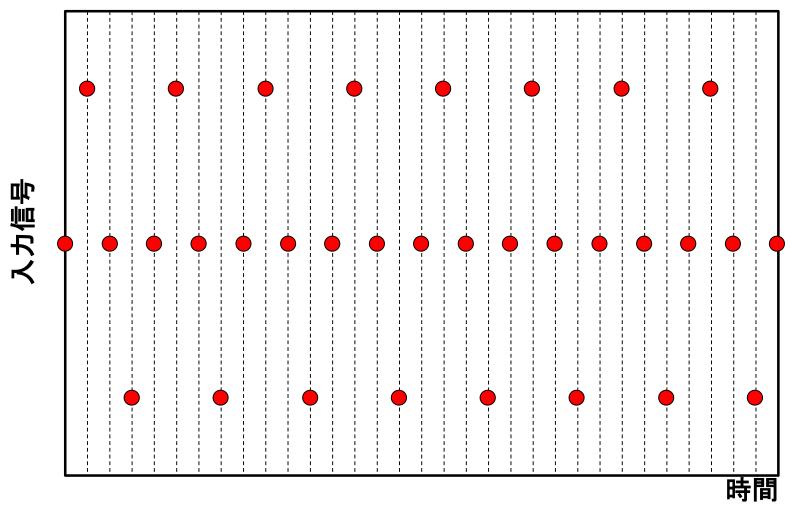

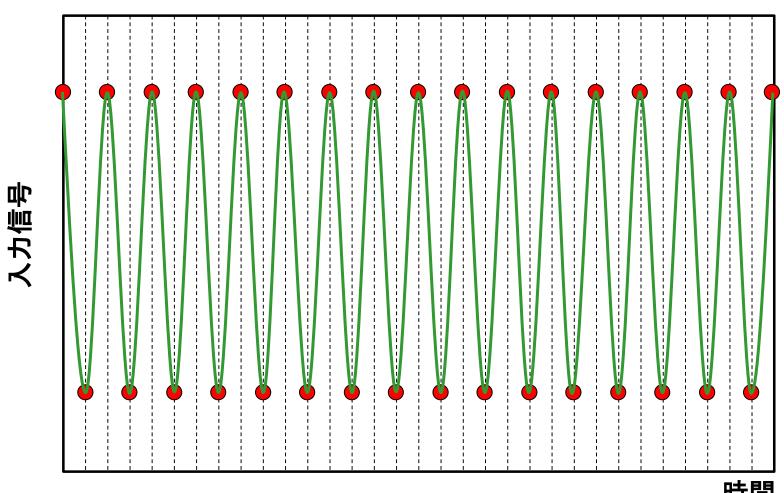

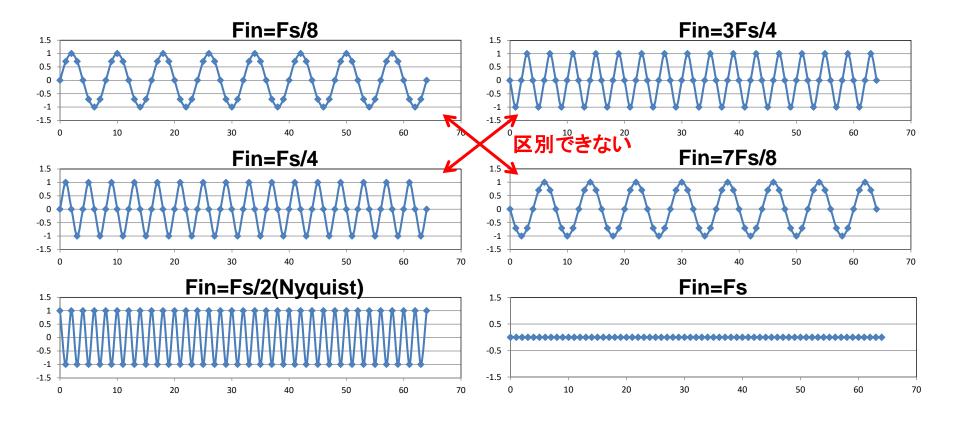

### Fin(入力周波数)=Fs(サンプリング周波数)/8 の場合

サンプリングポイント

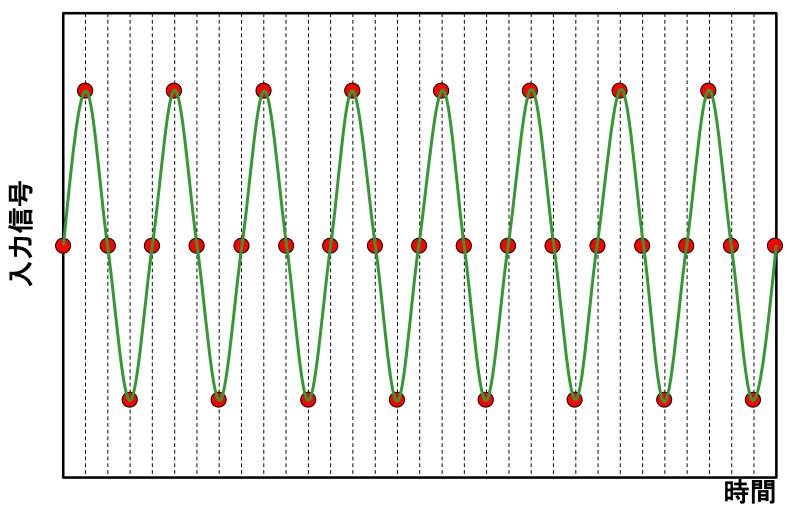

### Fin=Fs/8 の場合 サンプリング点を順番になぞってみる

サンプリングポイント

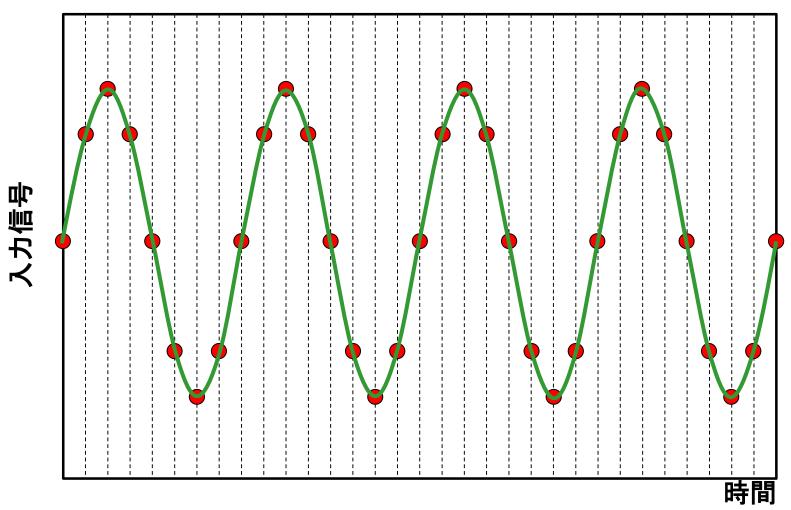

### Fin=Fs/8 の場合→信号再生できる

● サンプリングポイント

### Fin(入力周波数)=Fs(サンプリング周波数)/4 の場合

サンプリングポイント

### Fin=Fs/4 の場合 サンプリングポイントを順番になぞってみる

サンプリングポイント

### Fin=Fs/4 の場合→信号再生できる

● サンプリングポイント

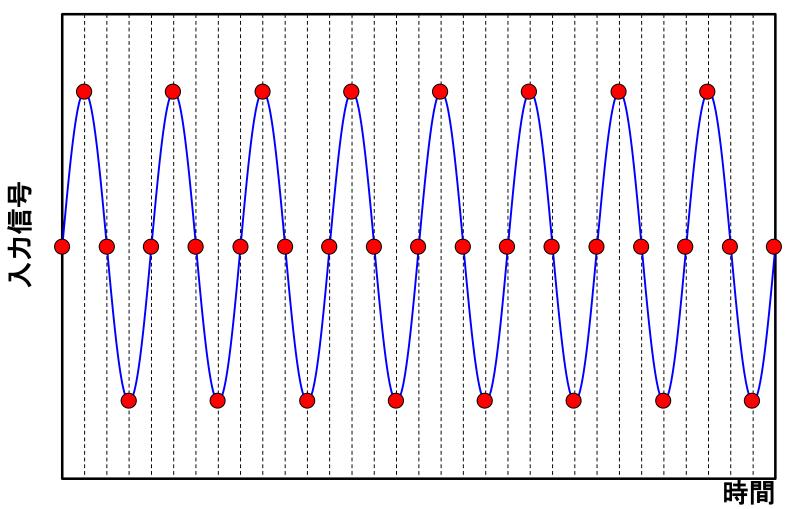

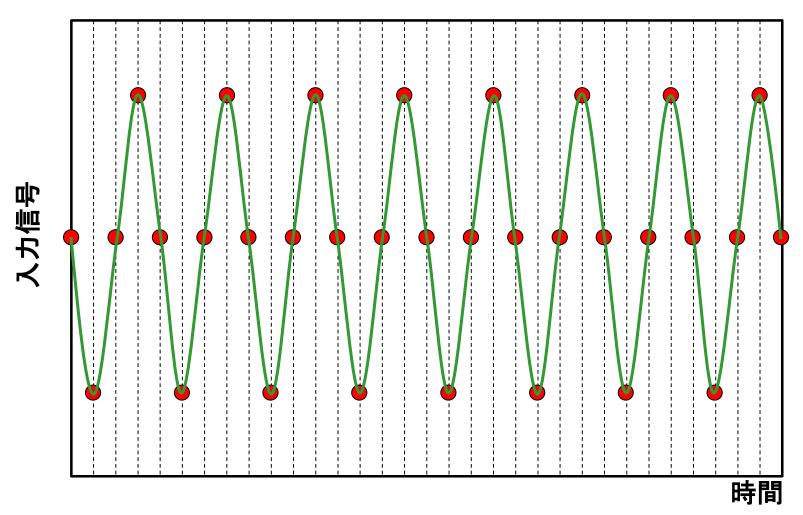

### Fin(入力周波数)=Fs(サンプリング周波数)/2 の場合

サンプリングポイント

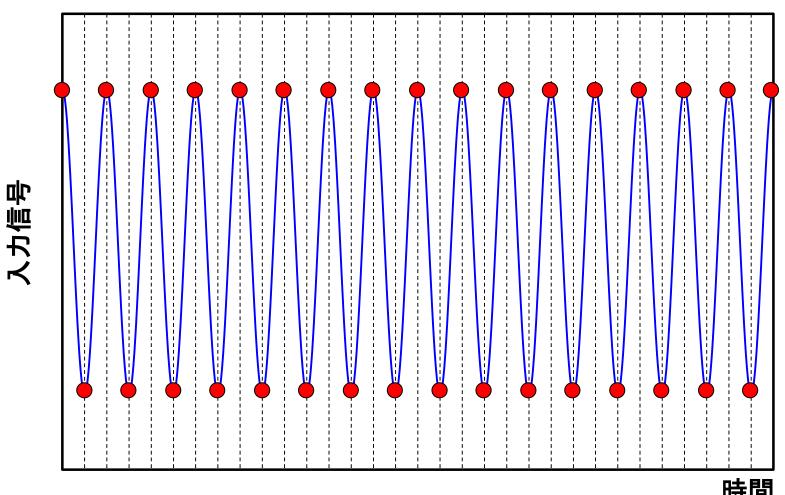

### Fin=Fs/2 の場合 サンプリングポイントを順番になぞってみる

サンプリングポイント

### Fin=Fs/2 の場合→(ぎりぎり)信号再生できる

サンプリングポイント

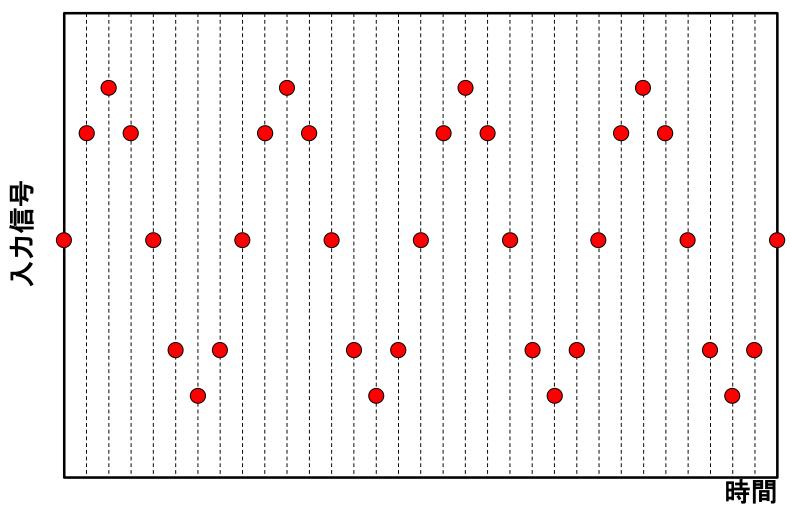

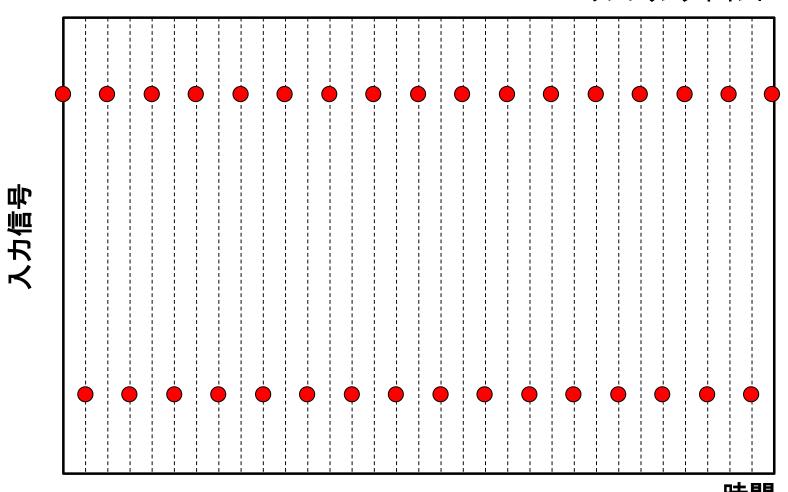

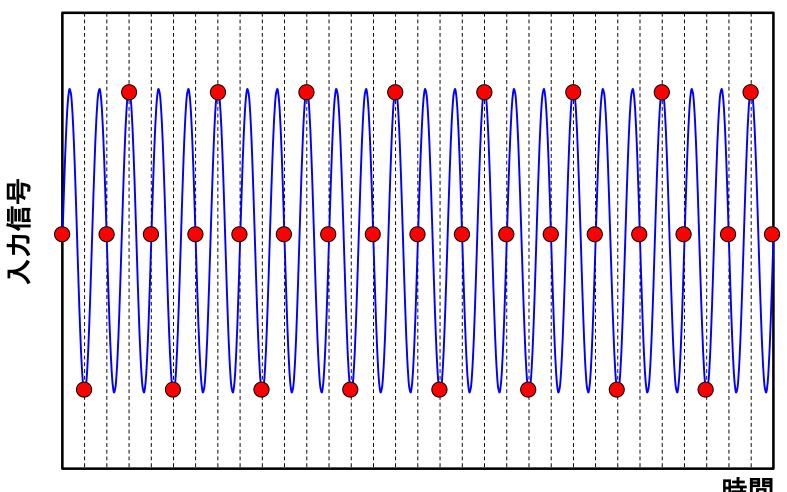

### Fin(入力周波数)=3Fs(サンプリング周波数)/4 の場合

サンプリングポイント

### Fin=3Fs/4 の場合 サンプリングポイントを順番になぞってみる

サンプリングポイント

### Fin=3Fs/4 の場合→信号再生できない

● サンプリングポイント

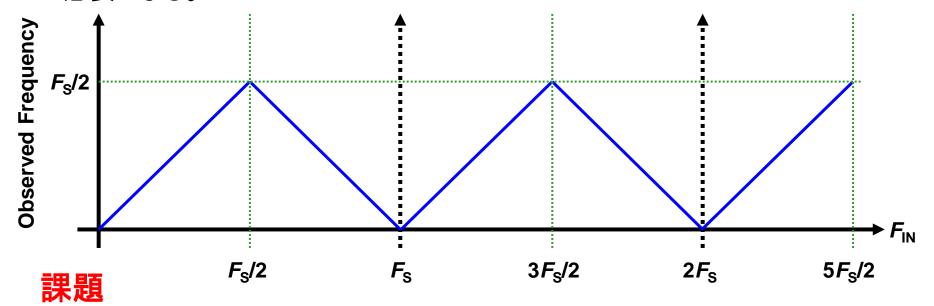

### Nyquist周波数

入力周波数が $F_s$ /2を超えると折り返し信号(エイリアシング)が発生し、波形を再現できない。この再現限界のことを標本化(サンプリング)定理という。標本化定理を示したHarry Nyquistにちなんで $F_s$ /2をNyquist(ナイキスト)周波数という。

アナログ・デジタル変換技術

### 信号の折り返し

Fs/2を超える周波数成分は帯域内に折り返してしまう。ノイズや妨害 波も折り返してしまうため、これを抑制するアンチエイリアスフィルタが 必要となる。

$F_s$ =1MS/sのADCに下記の入力信号周波数が与えられた場合、ADCの出力コードとして観測される信号の周波数を求めよ。

- ① 100kHz

- 2 700kHz

- **③ 1.2MHz**

- 分解能について

- アプリケーションに応じて必要な分解能、基準信号(測定可能範囲)を決めること。

- ・サンプリングレートについて

- ADCに入力される信号周波数の上限がナイキスト周波数(Fs/2)以下となるようにすること。

疑問:とにかく分解能、サンプリングレート共に高いものを選んで来ればよいのでは...?

- 1. ADCの基本機能

- 量子化

- サンプリング定理

- 2. ADCの性能表現

- 3. ADCの主要な変換方法

- 変換アーキテクチャの概要とトレンド

- 4. ADCの設計例

- SAR ADC

- 5. ADCの評価方法

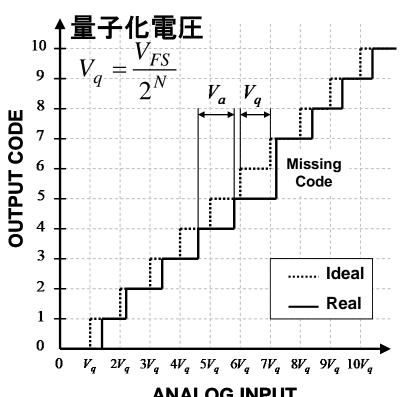

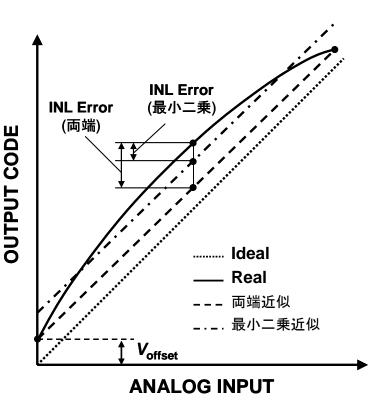

**DNL**(Differential non linearity) **INL(Integral non linearity)**

→ 1ステップ毎の誤差量

→ 理想の入出力直線に対する実際の入出力特性の誤差量

**ANALOG INPUT**

$$DNL(LSB) = \frac{V_a - V_q}{V_q}$$

DNLの下限値は-1(ミッシング)

### 分解能とSNRの関係

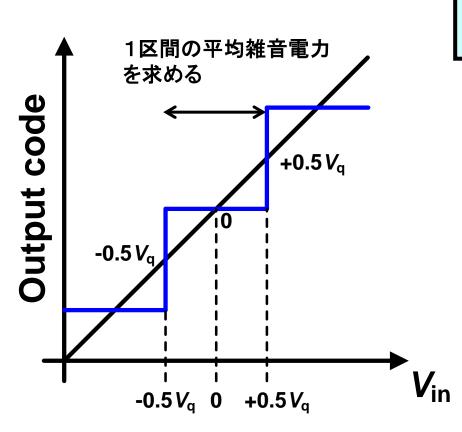

量子化は必ず量子化ノイズを伴い、ADCの分解能に応じて 得られるSNRの上限値が決まる。

SNR = 6.02N + 1.76 (dB)

#### 量子化雑音平均電力

$$P_{qn} = \frac{1}{V_{q}} \int_{-0.5V_{q}}^{+0.5V_{q}} v_{e}^{2} dV$$

$$= \frac{1}{3} \left( \frac{V_{q}}{2} \right)^{2} = \frac{1}{3} \left( \frac{V_{FS}}{2 \cdot 2^{N}} \right)^{2}$$

#### 信号電力(正弦波)

$$P_{\rm S} = \frac{1}{2} \left( \frac{V_{\rm FS}}{2} \right)^2$$

$$SNR = 10\log\left(\frac{P_{\rm S}}{P_{\rm N}}\right) = 20\log 2^N + 10\log\left(\frac{3}{2}\right)$$

理想的なADCの量子化雑音

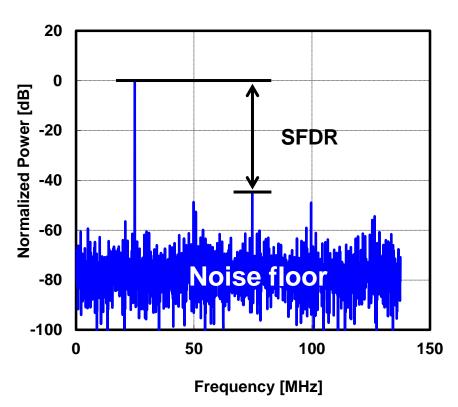

## ADCの動特性

### 動特性は入力信号と歪、ノイズ間の電力関係を表している。

$$SNR = 10\log\frac{P_S}{P_N} [dB]$$

$$SFDR = 10\log\frac{P_S}{P_{SP}}[dB]$$

$$THD = 10\log\frac{P_S}{P_{TH}}[dB]$$

$$SNDR = 10\log \frac{P_S}{P_N + P_{TH}} [dB]$$

$$ENOB = \frac{SNDR - 1.76}{6.02}$$

[bit]

$P_S$  = 信号電力, $P_N$  = ノイズ電力  $P_{SP}$  = 最大スプリアス電力, $P_{TH}$  = 高調波歪電力

$F_s$  = 275MS/s,  $F_{in}$  = 25MHz SFDR = 45.8 dB SNR = 40.2dB, SNDR = 38.2 dB

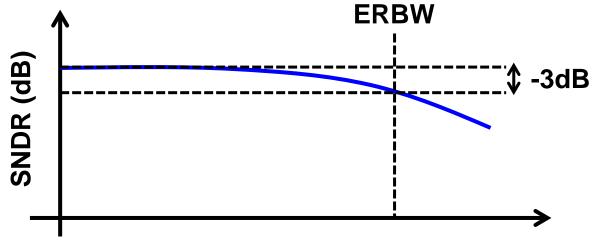

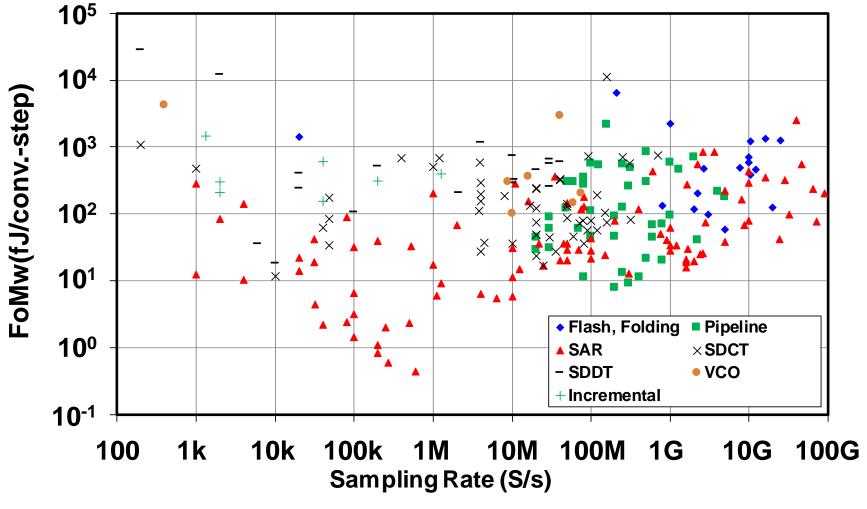

# 性能指標① Figure of Merit (FoM<sub>w</sub>)

異なる分解能、変換速度を持つADCに対して電力効率を比較するための性能指標の一つ。1変換・ステップ当たりに要するエネルギーを表す。

$$FoM_W = \frac{P_D}{2^{ENOB} \cdot Min(F_S, 2 \times ERBW)}$$

(J/conv. step)

ERBWは有効な信号帯域を表す。

**Input Frequency (Hz)**

FoMwが低いほど効率の良いADCといえる。 現状最も優れたFoMwは1fJ/conv.を切る程度

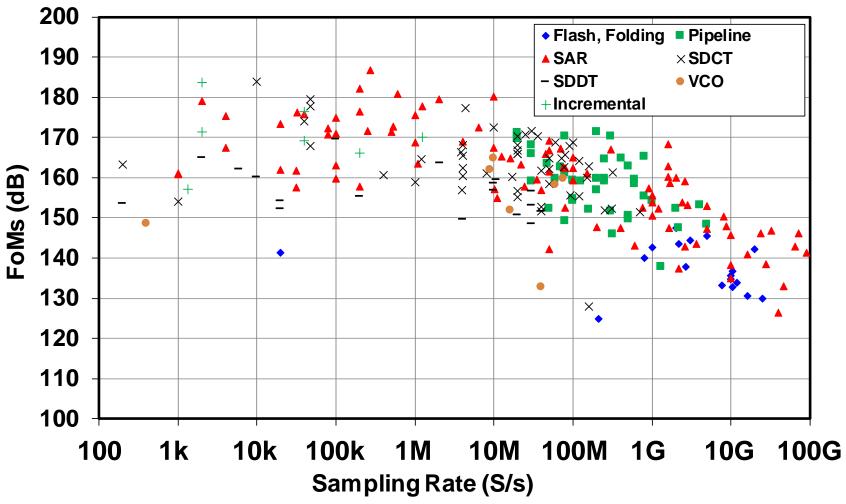

# 性能指標② Figure of Merit (FoMs)

異なる分解能、変換速度を持つADCに対して電力効率を比較するための 性能指標一つ。雑音電力によってSNRが決まる領域で有効な指標。

$$FoM_S = SNDR + 10\log_{10}\left(\frac{BW}{P_D}\right)$$

(dB)

FoMsが高いほど効率の良いADCといえる。 現状最も優れたFoMsは180dB程度

疑問:

FoMwとFoMsの違いは?どちらを使うべき?

# FoMwとFoMsの違い

- 分解能を1bit向上させるために必要となる消費 電力の増加量についての考え方の違い

- $-FoM_{\rm W} \qquad P_{\rm D} \propto 2^{N}$

- Flash型ADC⇒1bit増で比較器個数2倍

- ・ 回路規模が2倍になるのだから消費電力も2倍

- $-FoM_{\rm S}$   $P_{\rm D} \propto 2^{2N}$

- 1bit増で量子化電圧は1/2, 電力では1/4となる

- ・離散時間系の回路の熱雑音はkT/Cに比例する

- 熱雑音を1/4にするには容量Cを4倍にする

- ・速度一定の場合、消費電力は容量に比例する ⇒消費電力は4倍になる

10bit程度までは $FoM_w$ , それ以降は $FoM_s$ が用いられることが多い

- サンプリング周波数100MS/s,分解能 10bit のADCがある。SNDR=56.0dB, ERBW=80MHz、消費電力10mWの時、このADCのFoMw(fJ/conv.)を求めよ。

- ENOB=32 bit, サンプリング周波数 10GS/s, ERBW=5GHzのADCを実現するためには、どのくらいの消費電力(W)が必要か。現状実現できるFoMとして 1fJ/conv.-stepであるとする。

- 1. ADCの基本機能

- 量子化

- サンプリング定理

- 2. ADCの性能表現

- 3. ADCの主要な変換方法

- 変換アーキテクチャの概要とトレンド

- 4. ADCの設計例

- SAR ADC

- 5. ADCの評価方法

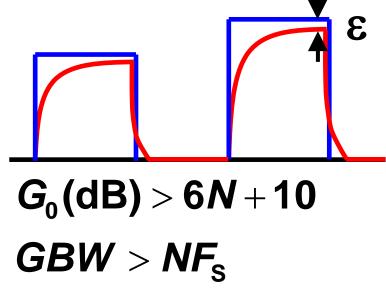

### ADC 主要な変換アーキテクチャ

並列型(Flash)

低精度,最高速,消費電力大

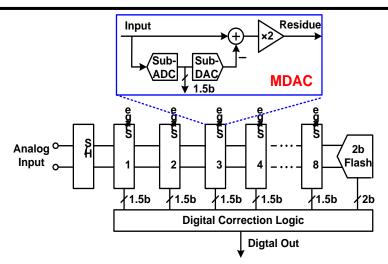

### Pipeline型

中~高精度, 高速, 消費電力中

逐次比較型(SAR) 中精度, 中速, 最小電力

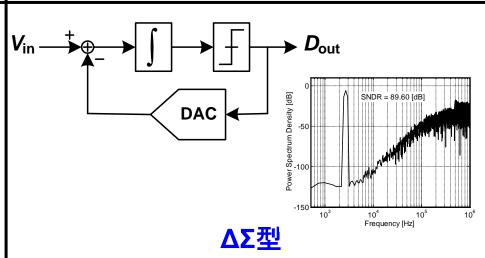

Over sampling & Noise Shaping 最高精度, 最低速, 消費電力大

本講義では省略

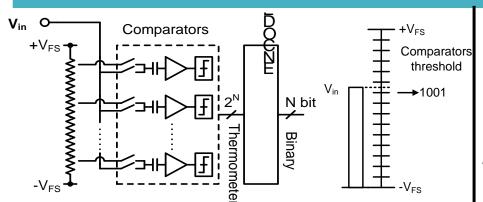

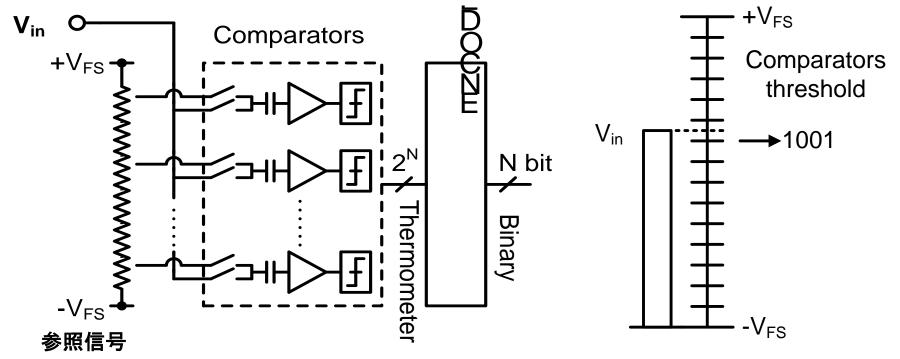

# 並列型(Flash) ADC

ものさしで長さを測る方式とよく似ている 目盛の生成には参照信号と比較器を用いる 基準信号と一斉に比較するので、最も高速な変換が可能 必要となる比較器個数 2<sup>N</sup>-1 →高分解能では回路規模大 高分解能ADCには向かず、~6bitくらいまで 比較器の性能がADCの性能の大半を決める

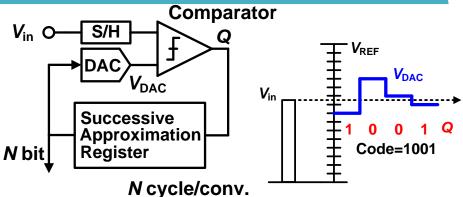

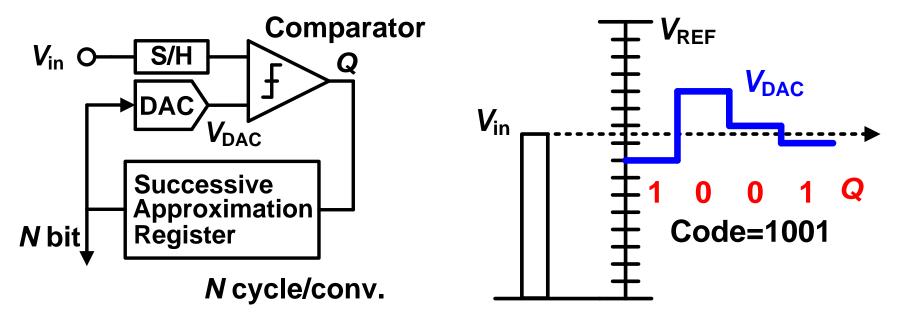

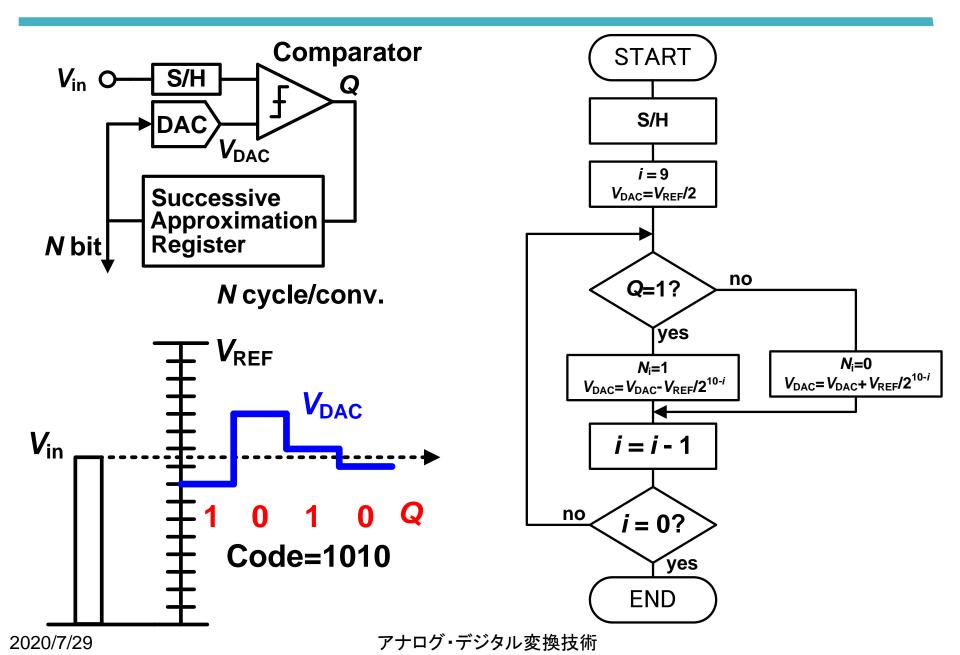

### 逐次比較型(SAR) ADC

DAC(重り)と比較器(天秤)を用いた変換方法。 正確なDACと高速、高精度な比較器が必要。

#### 課題

0~15枚の金貨が入った袋がある。天秤と金貨15枚を用いて、なるべく 少ない試行回数で袋の中の金貨の枚数を当てるにはどうすればよい か?ただし袋の重さは無視できるものとする。

## SAR ADCの構成と基本動作

比較器(天秤)、DAC(重り)、SAR Logic(制御回路)から構成される。

定常電流を消費する回路がなく、アルゴリズムとして一回の変換に必要となる比較器動作回数が最小のため最も低消費電力動作が可能。

反面一回の変換にNサイクルの試行が必要なため単体では高速動作には向かない。が、近年はSAR ADCを複数並べて順番に動作させサンプリングレートを向上させるインターリーブ動作によって高速サンプリングの領域もカバーするようになっている。

単体ADCとして8bit~14bit,~100MHz程度までをカバーする。

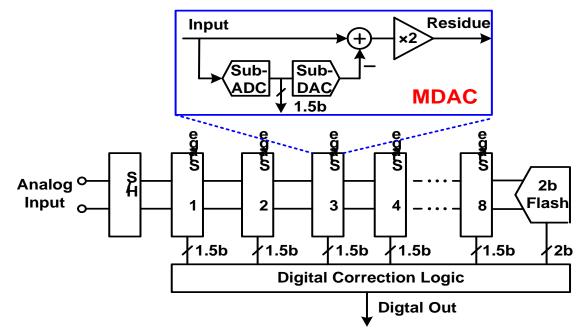

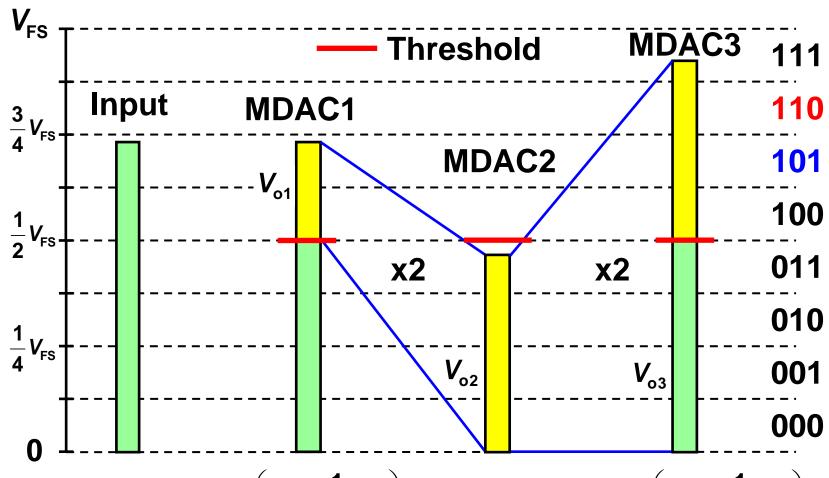

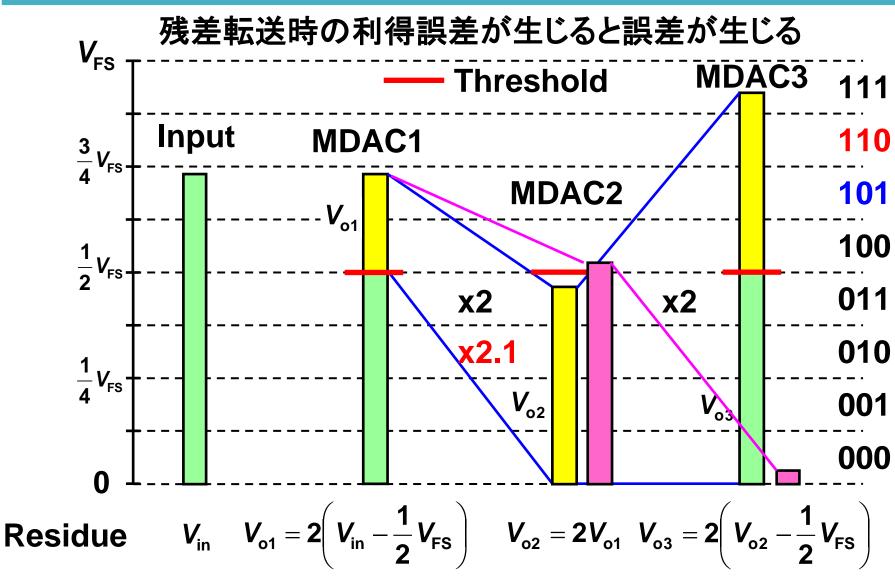

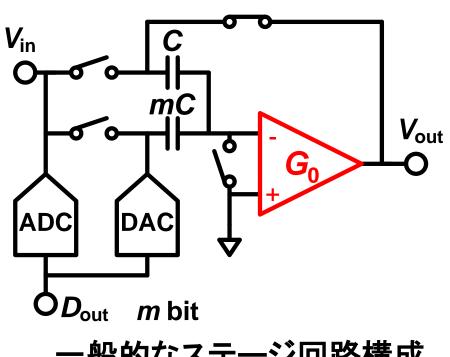

## パイプライン型ADC

デジタル回路でも用いられるパイプライン構造をとる。それぞれのステージでは 1~4bit程度の変換を行い、デジタル値を出力する。入力されたアナログ値から、出力するデジタル値をDACを通して引き算し、後段に一定の増幅率を持って 残差を送る。後段の回路は残差成分をアナログ入力とし、同様の変換を繰り返し行っていく。それぞれのステージは1CLKで上記の動作を繰り返し行うので、全ての出力が得られるまでステージ数分だけCLKが必要だが、パイプライン構造のためサンプリング速度は入力するCLK周波数と同等となるため高速動作に 向いている。(ただしレイテンシは大きいことに注意)。

アナログ・デジタル変換技術

### ・メリット

- パイプライン構造により動作速度を高めやすい

- 比較器の個数を抑えられる

- 1bit/stageの場合、最小10個(1個/stage)の比較器で構成可能

- 冗長構成をとれば比較器の精度はほとんど問題となら ない

- ただし比較器の必要個数は増える

- 1.5bit構成の場合、2個/stage

- 同じ回路構造の繰り返しでビット数を増やせるためビット拡張が比較的容易

- デメリット

- アナログ信号を正確に後段のステージに伝える必要が ある

- 動作速度の制限、消費電力の増加

Residue

$$V_{\text{in}} V_{\text{o1}} = 2 \left( V_{\text{in}} - \frac{1}{2} V_{\text{FS}} \right) V_{\text{o2}} = 2 V_{\text{o1}} V_{\text{o3}} = 2 \left( V_{\text{o2}} - \frac{1}{2} V_{\text{FS}} \right)$$

Output CODE 2020/7/29

**1 0** アナログ・デジタル変換技術

1

Output CODE 2020/7/29

$1 \rightarrow 0$

それぞれのステージは容量とオペアンプで構成されるスイッチトキャパシタアンプ を用いて正確な利得を実現している。

高速、高利得なオペアンプが必要となるため、消費電力が大きい。

微細化に伴いSAR ADCの高速化が実現されてきているためカバーできる性能 範囲が減っているが、比較的高精度(10~16bit)で高速サンプリング(100MS/s 以上)が必要な場合は用いられることが多い。

一般的なステージ回路構成

N: Number of bits

F<sub>s</sub>: Sampling freq.

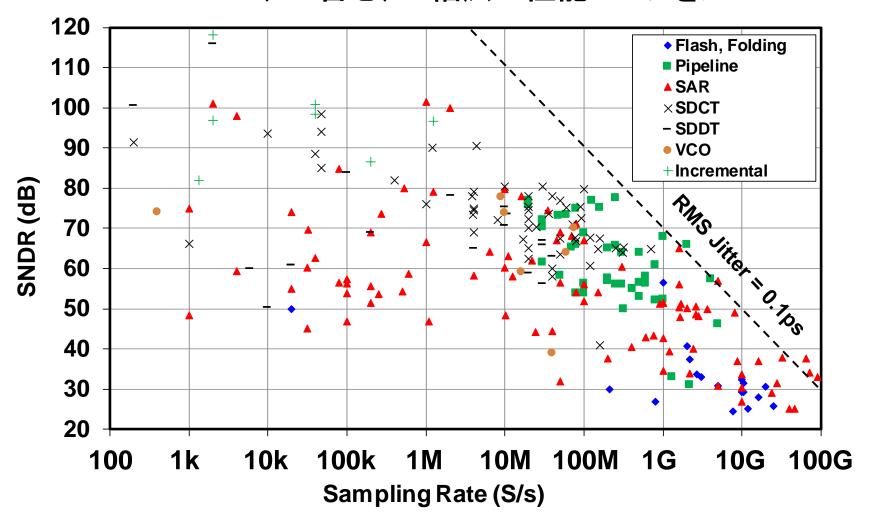

## ADCの性能と用途

### SAR ADC(OS含む)が幅広い性能レンジをカバー

B. Murmann, "ADC Performance Survey 1997-2018," [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

2020/7/29 アナログ・デジタル変換技術

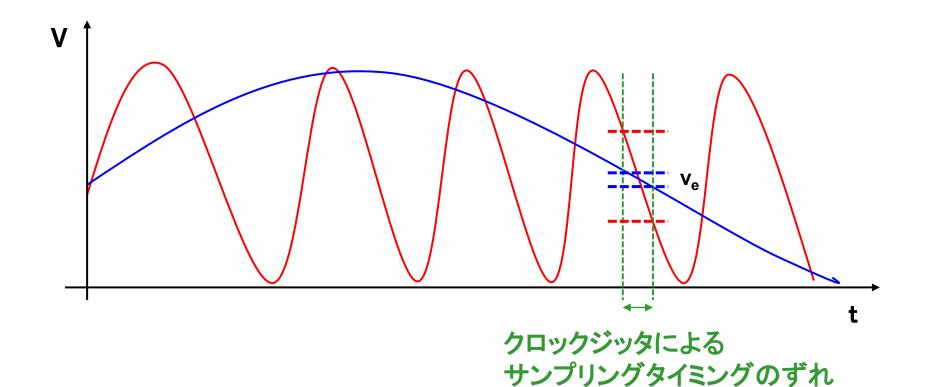

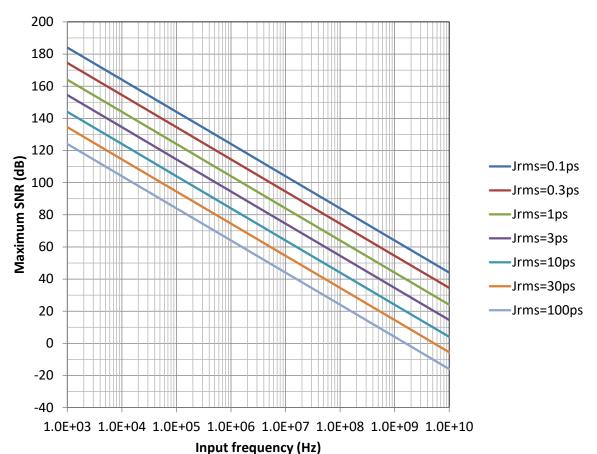

### 高周波信号ほどクロックジッタの影響を受けやすい

Maximum  $SNR(dB) = -20\log_{10}(2\pi \cdot F_{\text{in}} \cdot J_{\text{rms}})$

### 高周波信号ほどクロックジッタの影響を受けやすい

Maximum

$$SNR(dB) = -20\log_{10}(2\pi \cdot F_{\text{in}} \cdot J_{\text{rms}})$$

アナログ・デジタル変換技術

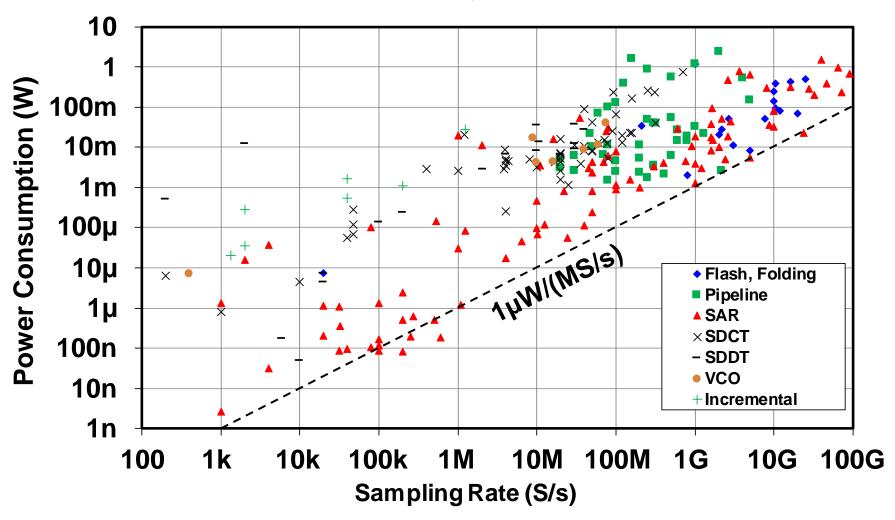

### SAR ADCが最も低消費電力動作に適する

B. Murmann, "ADC Performance Survey 1997-2018," [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

アナログ・デジタル変換技術

### ADCの技術動向 Fs vs. FoMw

オペアンプを必要とするパイプライン型、ΔΣ型は電力効率が悪くなりがち。 Flash型は比較器ベースであるが構造上電力効率は悪い。

B. Murmann, "ADC Performance Survey 1997-2018," [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

## ADCの技術動向 Fs vs. FoMs

FoMsの観点では最近のΔΣ型の電力効率は悪くない。 SNRが出にくい高サンプリングレートの領域はどの方式でも厳しい。

B. Murmann, "ADC Performance Survey 1997-2018," [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

#### SAR ADC

- 消費電力が低くサンプリングレートもそれなりで汎用性が高い。ΔΣ型ADCと組み合わせた低消費電力、高SNDRなハイブリッドADCも開発が進められている。

### • パイプライン型ADC

- 100MS/s以下の領域ではSAR ADCに勝ち目がないので、 更に高い周波数で高SNDRを達成すべき。

### ΔΣ型ADC

- 高SNDR領域で、低消費電力化を図るべき。アンチエイリアシングフィルタの設計容易さなどシステム全体を考えた時に有効性が出てくる。

### • Flash型ADC

- とにかく高速でなければ意味が無い。最低1GS/s以上で 低消費電力化を狙う。

- 1. ADCの基本機能

- 量子化

- サンプリング定理

- 2. ADCの性能表現

- 3. ADCの主要な変換方法

- 変換アーキテクチャの概要とトレンド

- 4. ADCの設計例

- SAR ADC

- 5. ADCの評価方法

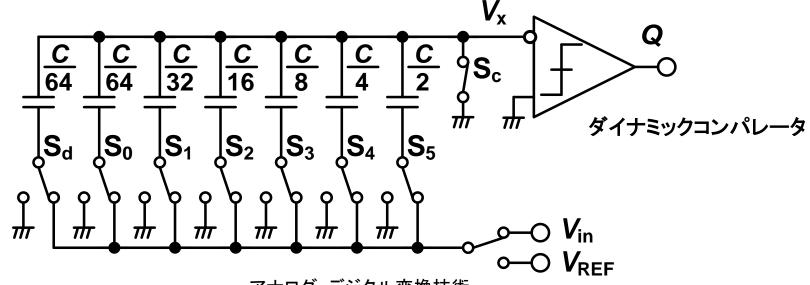

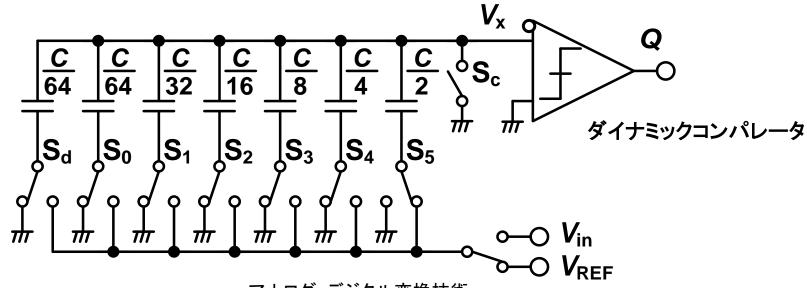

# SAR ADCの基本構成と動作

# SAR ADCの構成 サンプリング

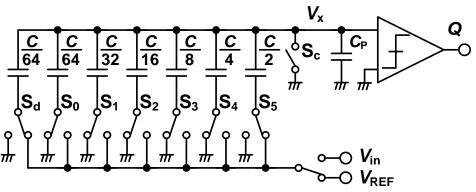

実際のSAR ADCは容量DACを用いてS/H機能とDAC動作を兼用する。 DACは容量比率の重みづけにより実現する。

### サンプリングモード

$$Q_S = CV_{in}$$

## SAR ADCの構成 MSB変換

実際のSAR ADCは容量DACを用いてS/H機能とDAC動作を兼用する。 DACは容量比率の重みづけにより実現する。

#### サンプリングモード

$$Q_S = CV_{in}$$

#### MSB変換モード

$$Q_{MSB} = \frac{C}{2}(V_{REF} - V_X) - \frac{C}{2}V_X$$

## SAR ADCの構成 MSB変換

実際のSAR ADCは容量DACを用いてS/H機能とDAC動作を兼用する。 DACは容量比率の重みづけにより実現する。

### サンプリングモード

$$Q_S = CV_{in}$$

$$Q_S = Q_{MSB}$$

より、

#### MSB変換モード

$$Q_{MSB} = \frac{C}{2}(V_{REF} - V_X) - \frac{C}{2}V_X$$

$$V_X = -\left(V_{in} - \frac{1}{2}V_{REF}\right)$$

- 容量DACがSAR ADCの精度の大半を決めてしまうため、注意深く設計する必要がある。

- 線形性

- 容量ばらつきによるDNL, INLの劣化

- ノイズ

- サンプリング時、変換時の熱雑音

- 応答特性

- SWのON抵抗

- 消費電力

- 参照電圧からの引き込み電流

設計方針としては、線形性、ノイズ特性を満たす最小の容量値を選ぶようにすればよい。

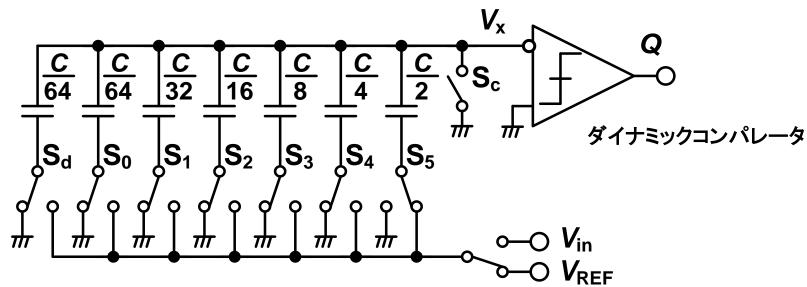

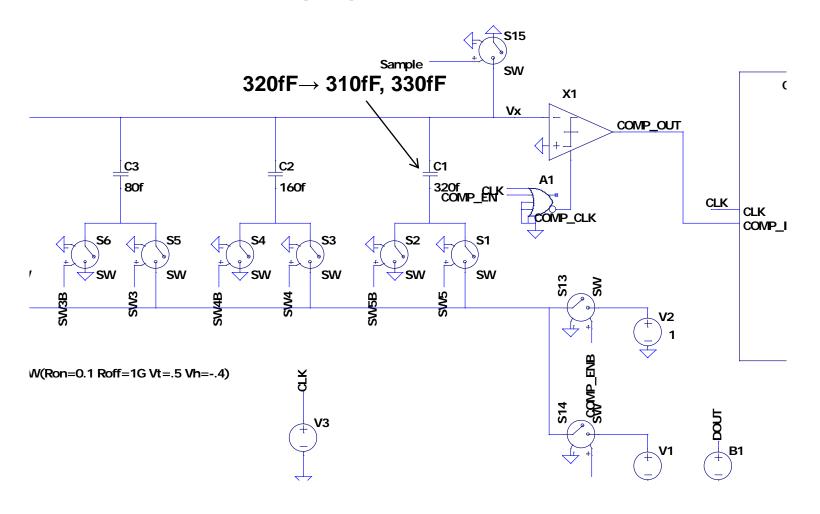

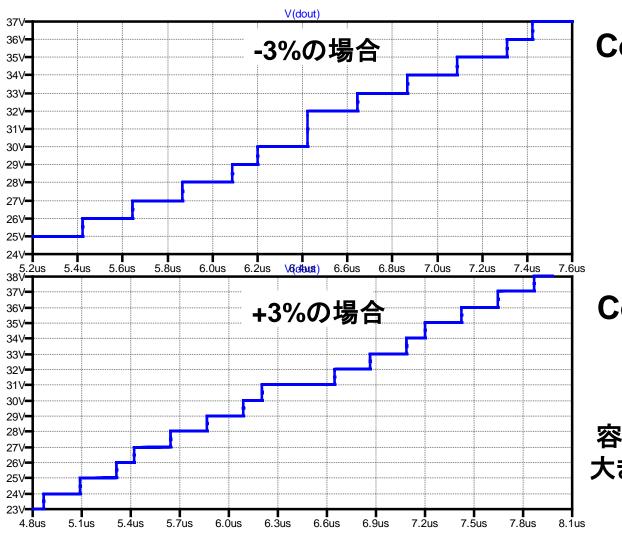

# 容量のミスマッチ (MSB)

### MSBの容量(C1)を3%程度ばらつかせてみる

# 容量のミスマッチの影響 (MSB)

#### MSBの容量にばらつきが生じた場合、 $V_{ES}/2$ で大きなDNL誤差が生じる

Code 31がミッシング (DNL=-1)

Code 31の期間が長い (DNL + ↑)

容量が小さいとマイナス、 大きいとプラスのDNL誤差

アナログ・デジタル変換技術

# 容量のミスマッチ (MSB-1)

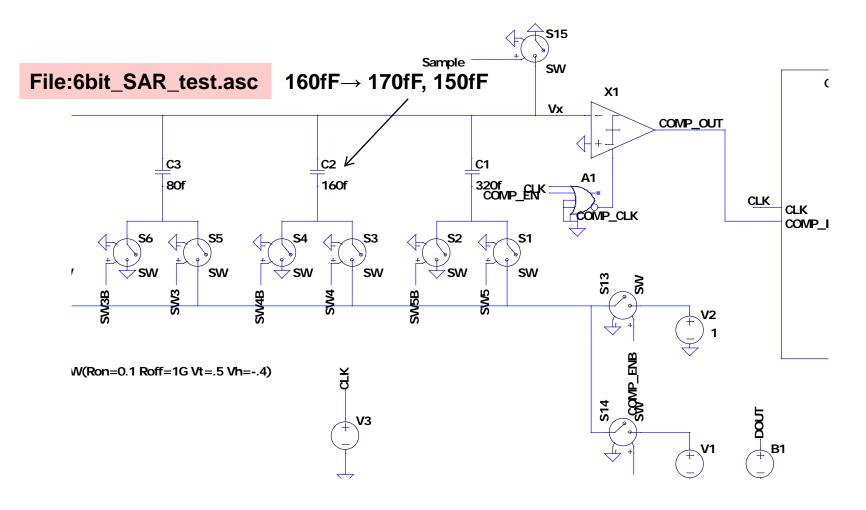

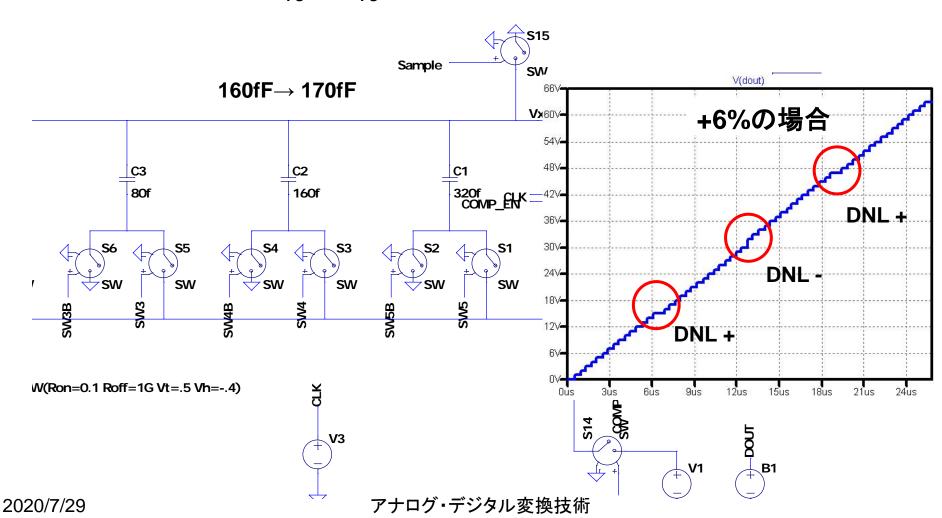

### MSB-1の容量(C2)を6%程度ばらつかせてみる

アナログ・デジタル変換技術

MSB-1の容量にばらつきが生じた場合、 $V_{FS}/4$ ,  $V_{FS}/2$ ,  $3V_{FS}/4$ で大きなDNL誤差が生じる

## 容量のミスマッチの誤差傾向

MSB vs. MSB-1以下の容量の総和で比べるとMSBが小さい

→ V<sub>FS</sub>/2にマイナスのDNL

MSB-1 vs. MSB-2以下の容量の総和で比べるとMSB-1が大きい

→ V<sub>FS</sub>/4, 3V<sub>FS</sub>/4にプラスのDNL

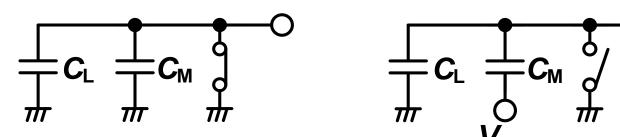

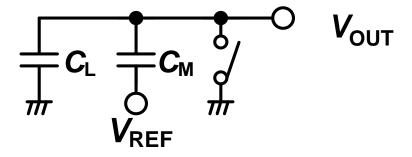

## 容量ミスマッチの許容値

#### MSBの変換の場合を考える

リセット

DAC動作

出力電圧

$$V_{\text{OUT}} = \frac{C_{\text{M}}}{C_{\text{M}} + C_{\text{L}}} V_{\text{REF}}$$

# ばらつき感度

$$\Delta V_{\text{OUT}} = \frac{\partial V_{\text{OUT}}}{\partial C_{\text{M}}} \Delta C_{\text{M}} + \frac{\partial V_{\text{OUT}}}{\partial C_{\text{L}}} \Delta C_{\text{L}} = \frac{C_{\text{L}} \Delta C_{\text{M}} - C_{\text{M}} \Delta C_{\text{L}}}{\left(C_{\text{M}} + C_{\text{L}}\right)^{2}} V_{\text{REF}}$$

$$= \frac{\left(\Delta C_{\text{M}} - \Delta C_{\text{L}}\right)}{4C_{\text{S}}} V_{\text{REF}} \qquad \because C_{\text{M}} = C_{\text{L}} = C_{\text{S}}$$

アナログ・デジタル変換技術

## 容量ミスマッチの許容値 Cont'd

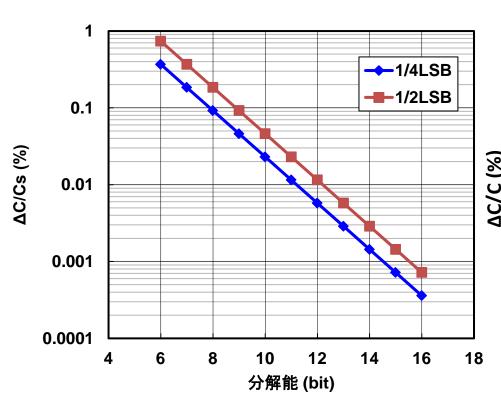

### DNL<1/4LSBを達成するためには、

$$\frac{\left(\Delta C_{\mathrm{M}} - \Delta C_{\mathrm{L}}\right)}{4C_{\mathrm{S}}} V_{\mathrm{REF}} < \frac{V_{\mathrm{REF}}}{2^{N+2}} \qquad \qquad \qquad \qquad \frac{\Delta C_{\mathrm{M}} - \Delta C_{\mathrm{L}}}{C_{\mathrm{S}}} < \frac{1}{2^{N}}$$

### ΔCMとΔCLが無相関なばらつきを持っている場合、

$$\frac{\Delta C}{C_{\rm S}} < \frac{1}{2^{N+0.5}}$$

### 3σの範囲で1/4LSBを達成するためには

$$\frac{\Delta C}{C_{\rm S}}(\sigma) < \frac{1}{3} \frac{1}{2^{N+0.5}}$$

## 容量ミスマッチ 演習

#### 演習

- 1. 8bitのSAR ADCにおいてDNL < 1/4LSBを達成したい。 MSBの容量ばらつき $\Delta$ C/C $_s$ (%)の許容値はいくらか。

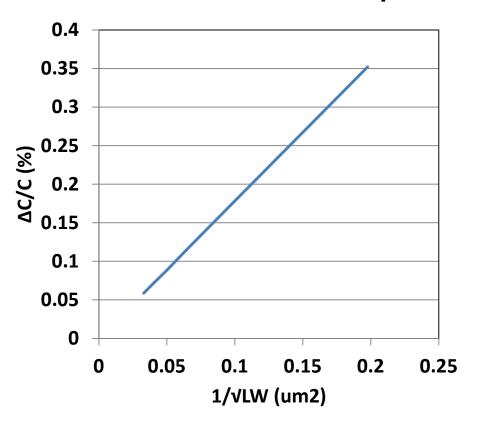

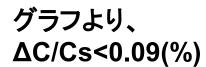

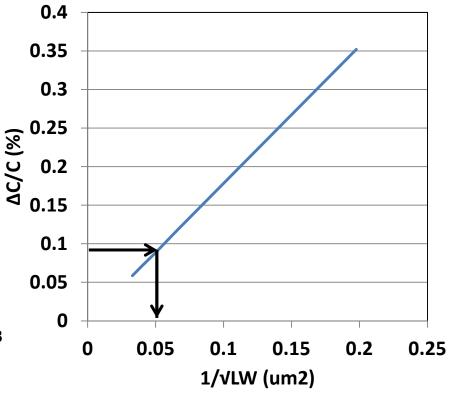

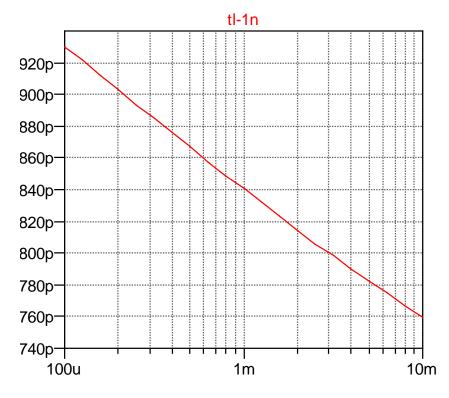

- 2. 下のグラフのようなばらつき特性を持つ容量を用いる場合、問1のMSBの容量値はいくらか。ただし単位面積容量は1fF/μm²とする。

単位面積容量 1fF/μm²

アナログ・デジタル変換技術

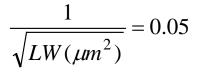

# 容量ミスマッチ 解答

$$LW(\mu m^2) = \frac{1}{0.05^2} = 400$$

容量值 = 単位面積容量×面積 = 400fF

アナログ・デジタル変換技術

SAR ADCではサンプリング時の雑音と変換時の雑音について注意を払う必要がある。ここではCDACに関わる雑音について解説する。

- サンプリング時の雑音

- 変換時の雑音

- CDACが発生する雑音

- リファレンス回路が発生する雑音

- ・比較器が発生する雑音

# 容量DAC サンプリング時の雑音

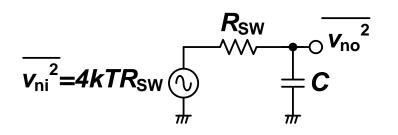

$rac{K_{SW}}{V_{ni}^2} = 4kTR_{SW}$   $rac{K_{SW}}{m}$   $rac{V_{no}^2}{m}$  1次のLPF特性を持つている場合は、

ノイズの実効帯域はカットオフ周波数に $\pi/2$ を乗じたものになる。 1次のLPF特性を持っている場合は、

#### ノイズ実効帯域

$$\Delta f_{\rm eff} = \frac{\pi}{2} \frac{1}{2\pi R_{\rm SW} C}$$

#### RMSノイズ

$$v_{\text{no}}^2 = \overline{v_{\text{ni}}^2} \Delta f_{\text{eff}} = \frac{kT}{C}$$

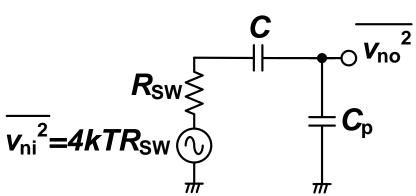

# 容量DAC 変換時の雑音

V<sub>x</sub>ノードにつく寄生容量をC<sub>p</sub>とした場合

#### 実効ノイズ帯域

$$\Delta f_{\text{eff}} = \frac{\pi}{2} \frac{1}{2\pi R_{\text{SW}} \frac{C_{\text{p}}}{1 + \frac{C_{\text{p}}}{C}}} \approx \frac{1}{4R_{\text{SW}}C_{\text{p}}}$$

通常 $C_p << C$

#### RMSノイズ

$$v_{\text{no}}^2 = \overline{v_{\text{ni}}^2} \Delta f_{\text{eff}} = \frac{kT}{C_{\text{p}}}$$

やたら大きくなってしまう?

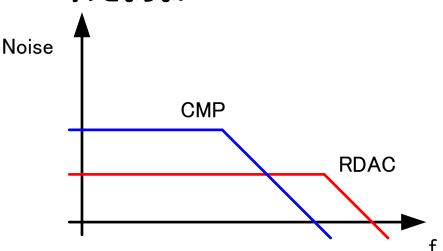

①f<sub>CMP</sub> < f<sub>RDAC</sub>の場合

CMPの実効帯域と4kTR<sub>SW</sub>で決まる →CMPの帯域を下げる or R<sub>sw</sub>を下げる

CMPの帯域を下げる ⇒ビットサイクルの速度低下 Rswを下げる

⇒スイッチング消費電力の増加するが 速度の向上も見込めるためトレード オフとならない

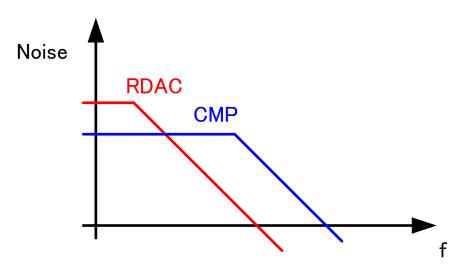

②f<sub>CMP</sub> > f<sub>RDAC</sub>の場合

KT/Cpで決まる。

→ Cpを上げるしかない。

CDACのセットリング時間の増加

- ⇒ビットサイクルの速度低下

- ⇒面積の増加

- ⇒CDAC利得の低下、比較器要件悪化

①の条件を満たすようにし、CMPの実効帯域内の雑音レベルを下げるほうが筋がよい

アナログ・デジタル変換技術

## CDACが発生する熱雑音 まとめ

### サンプリング時の雑音

$$v_{\text{no\_s}}^2 = \frac{kT}{C}$$

### • 変換時の雑音

$$v_{\text{no\_c}}^2 = v_{\text{ni}}^2 \Delta f_{\text{eff\_comp}} = ?$$

① $f_{\text{CMP}} < f_{\text{RDAC}}$ の場合  $v_{\text{no\_c}}^2 = \frac{kT}{C_{\text{p}}}$  ② $f_{\text{CMP}} > f_{\text{RDAC}}$ の場合

# ②のノイズ条件の場合

$$v_{\text{no\_t}}^2 = \frac{kT}{C} + \frac{kT}{C_p}$$

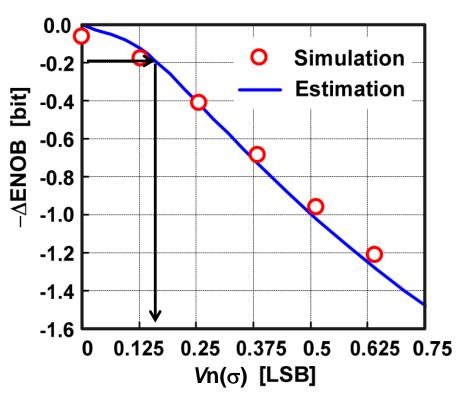

$$\Delta ENOB(bit) = -\frac{1}{2}\log_2\left(1 + 12\left(\frac{v_n}{V_q}\right)^2\right)$$

信号振幅を1Vppと仮定した場合、8bit ADCにおいて有効ビットの劣化量を 0.2bitとするには、

$$V_{\text{no_t}}(\sigma) < 0.14 \text{LSB}$$

= 0.14x1/2<sup>8</sup> = 547 $\mu$ V

C=C<sub>p</sub>の場合、

$$C > \frac{2kT}{v_{\text{no t}}^2} = 37\text{fF}$$

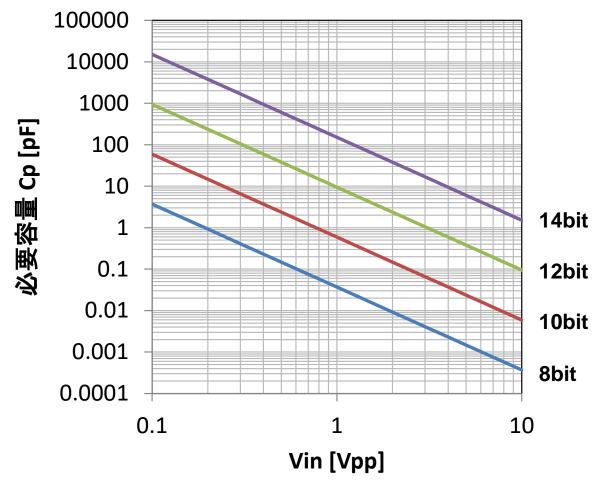

# ②のノイズ条件の場合 必要容量値

ADCの分解能が2bit上がると必要な容量値は16倍になる。 信号振幅を2倍にすると容量値は1/4に減じられる。

アナログ・デジタル変換技術

- 容量のサイズはADCの分解能に対して十分 な精度が確保できるサイズを選ぶこと。

- 容量DACの雑音はサンプリング時、変換時の雑音それぞれ考慮する必要がある。サンプリング時の雑音はサンプリング容量で決まるが、変換時の雑音は容量DACの出力につく寄生容量で決定されるので注意すること。

- 特に高分解能ADCでは雑音の要件が厳しくなるので(2bitの増加で16倍の容量が必要)、十分な容量値を確保するとともに、信号振幅を大きくするなど工夫が必要となる。

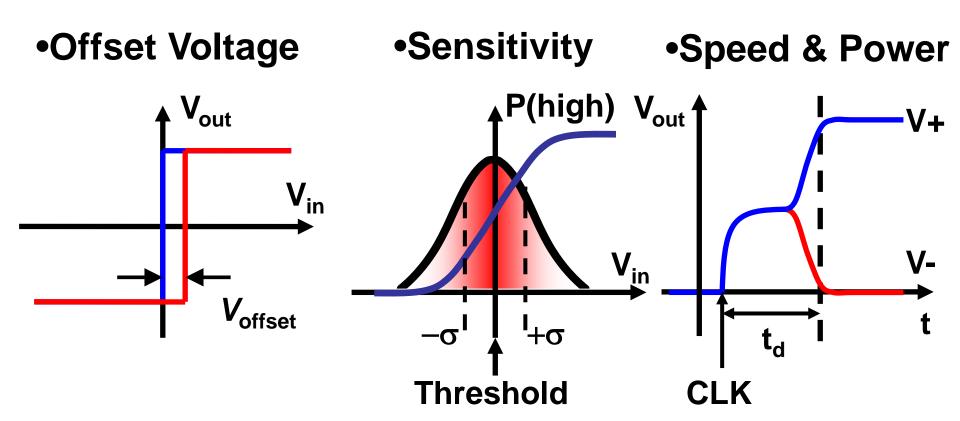

- Transistor mismatch

- Parasitic capacitance

- Transistor Noise

- Circuit topology

- Transistor size

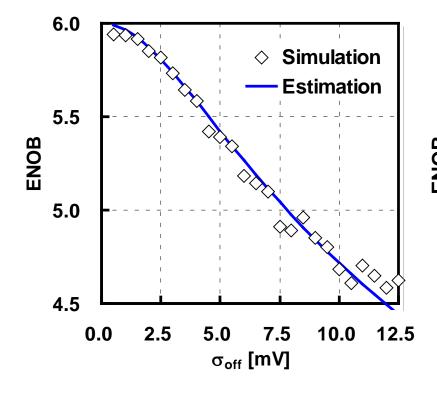

Flash型ADCやSAR ADCなどのコンパレータベースのADCではコンパレータのオフセット電圧やノイズによりADCの性能が劣化する。

$$ENOB = N - \frac{1}{2}\log_2(1 + 12\alpha^2) \alpha = \frac{V_{offset}(\sigma)}{V_q}$$

$$ENOB = N - \frac{1}{2}\log_2(1 + 12\gamma^2) \qquad \gamma = \frac{v_n(\sigma)}{V_{\sigma}}$$

オフセット電圧による性能劣化 (Flashの場合) ノイズによる性能劣化

アナログ・デジタル変換技術

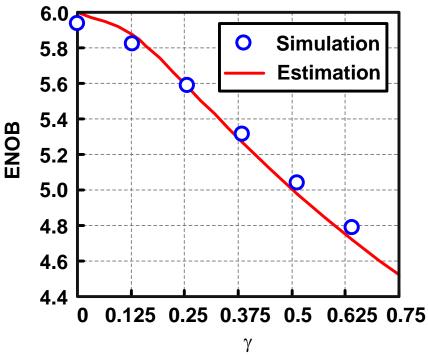

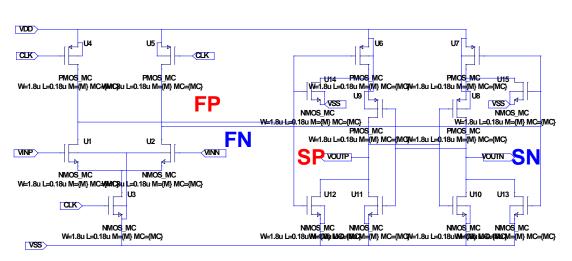

従来の比較器よりも低電圧動作に向き、低オフセット、低ノイズ。 近年様々な高性能ADCに用いられている。

単純化のため、全てのMOSトランジスタのサイズはW/L=1.8/0.18

File:comp.asc

M. Miyahara, et. al, A-SSCC 2008

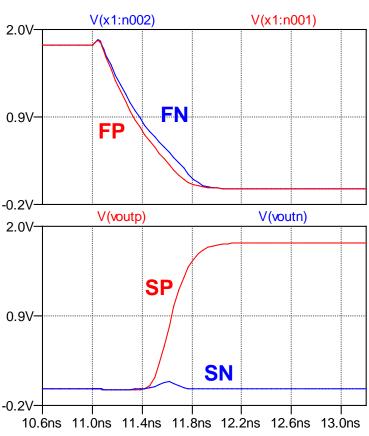

### コンパレータの動作

入力信号に応じて初段ステージの出力FP,FNの立下り時間がに差が生じ、 二段目のラッチ回路はこの差を検出して1,0判定をする。

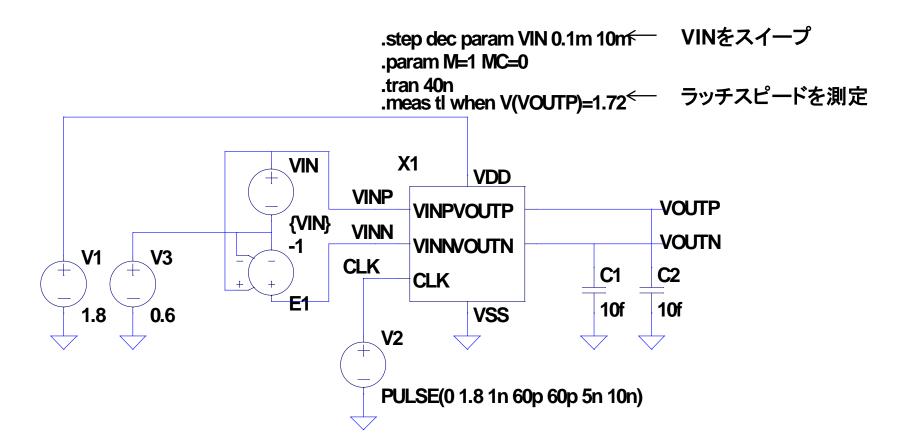

## 動作速度検証

### 入力信号をスイープし、動作速度を確かめる

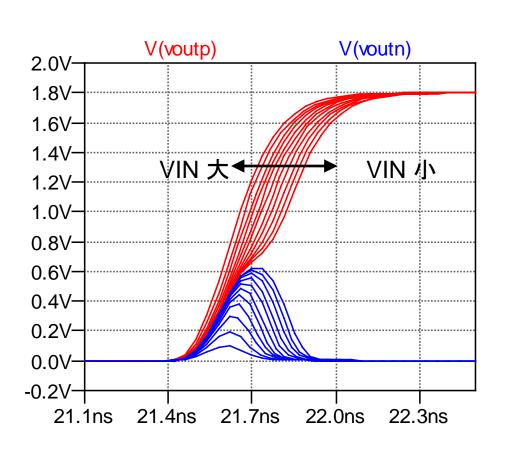

## 動作速度検証 結果

入力が小さくなるほどラッチスピードは遅くなっていく様子がわかる。 コンパレータ動作.logにラッチスピードが記載される。

| Measurement: ti |               |  |  |  |

|-----------------|---------------|--|--|--|

| step            | v(voutp)=1.72 |  |  |  |

| 1               | 2.0785e-009   |  |  |  |

| 2               | 2.06829e-009  |  |  |  |

| 3               | 2.06122e-009  |  |  |  |

| 4               | 2.05254e-009  |  |  |  |

| 5               | 2.04365e-009  |  |  |  |

| 6               | 2.03409e-009  |  |  |  |

| 7               | 2.02593e-009  |  |  |  |

| 8               | 2.01854e-009  |  |  |  |

| 9               | 2.00994e-009  |  |  |  |

| 10              | 2.0014e-009   |  |  |  |

| 11              | 1.99243e-009  |  |  |  |

| 12              | 1.98585e-009  |  |  |  |

| 13              | 1.97819e-009  |  |  |  |

| 14              | 1.971e-009    |  |  |  |

| 15              | 1.96386e-009  |  |  |  |

| 16              | 1.95586e-009  |  |  |  |

| 17              | 1.94859e-009  |  |  |  |

| 18              | 1.94055e-009  |  |  |  |

| 19              | 1.93064e-009  |  |  |  |

| 20              | 1.92225e-009  |  |  |  |

| 21              | 1.91024e-009  |  |  |  |

CLKは1nsで立ち上がるので上記から1nsを 減算したものが比較器の遅延時間

### 比較器の遅延時間

ラッチスピードは入力電圧の対数に比例して減少する。 入力が小さい時には著しくラッチスピードが低下する。 ⇒メタステーブルの発生, ADCの性能劣化の要因

$t_{l} \approx a \ln(V_{in}) + b$  [ps]

アナログ・デジタル変換技術

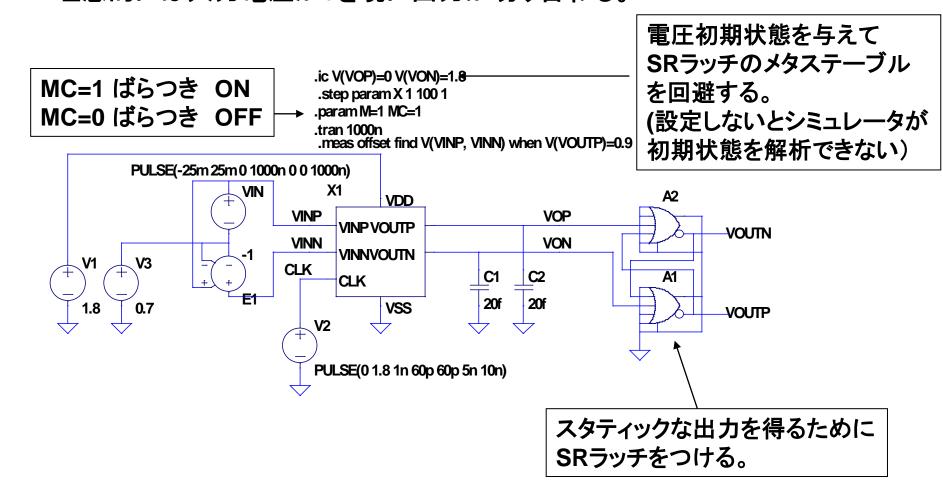

## コンパレータのオフセット電圧

ランプ波を入力し、コンパレータが切り替わった時の入力電圧を記憶する。 理想的には入力電圧が0を境に出力が切り替わる。

### オフセットシミュレーション準備

MC=1とすることでばらつきが発生していることを確かめる。 繰り返しシミュレーションをする前に、期待通りの結果が得られていることを 確認すること。

#### ばらつきが無い場合

#### ばらつきがある場合

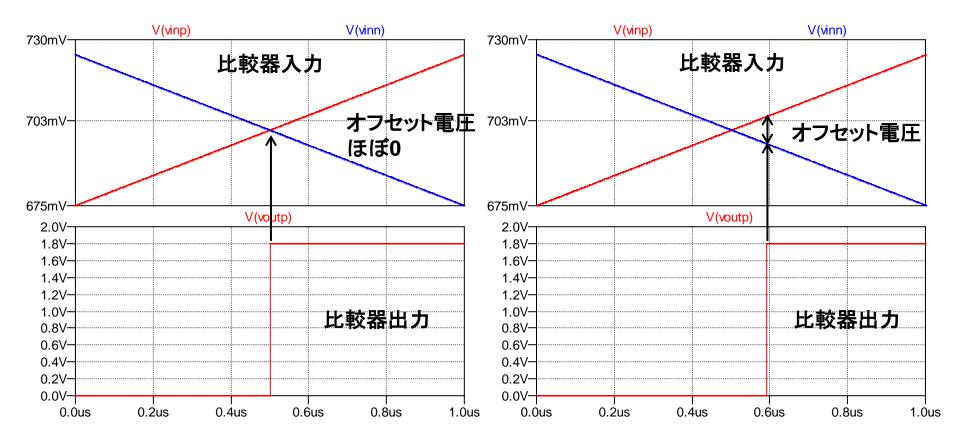

100回繰り返した場合の結果。 標準偏差やヒストグラムについては他のツールを用いて求める。

アナログ・デジタル変換技術

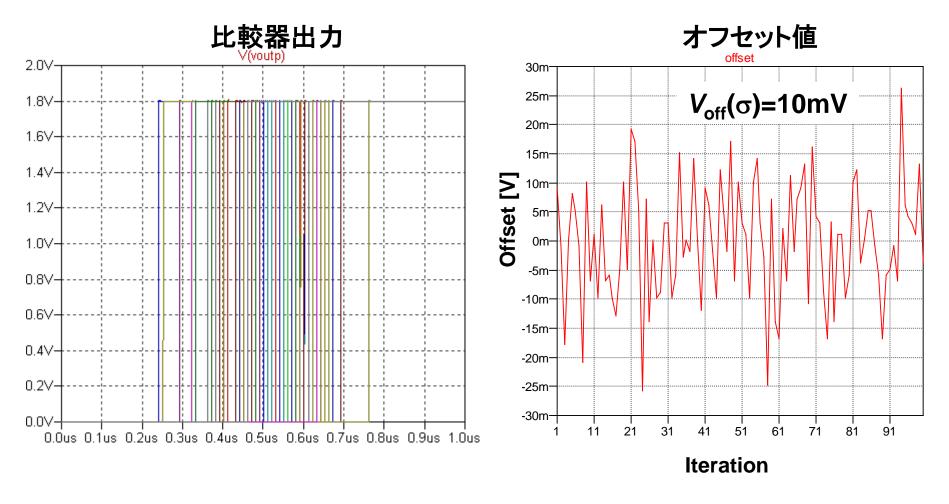

## オフセットのMOSサイズ依存性

### ダイナミックラッチ型コンパレータのオフセット電圧は しきい値電圧ばらつきが主要因

$$\Delta V_{\text{th}}(\sigma) \approx \alpha \frac{t_{\text{ox}}}{\sqrt{LW}}$$

tox=4n @0.18umプロセス  $\alpha$ はプロセスベンダーにより 異なる。このモデルでは  $\alpha$ =1に設定

| М                         | 1  | 4   | 9   |

|---------------------------|----|-----|-----|

| V <sub>off</sub> (σ) [mV] | 10 | 5   | 3.4 |

| 比率(M=1基準)                 | 1  | 1/2 | 1/3 |

面積、消費電力はMに比例。対してしきい値ばらつきは√Mに反比例。 ⇒ダイナミックラッチ型コンパレータのしきい値電圧を低減のために 面積を増加させることは非常に効率が悪い。

### 比較器のオフセット電圧計算

入力差動対のしきい値ばらつきは直接オフセット電圧につながるので、 主要因と考えられる。オフセット電圧への寄与率を考える。 MOS単体のしきい値ばらつきは、

$$\Delta V_{\text{th}}(\sigma) \approx \alpha \frac{t_{\text{ox}}}{\sqrt{LW}} = \frac{4 \times 10^{-9}}{\sqrt{0.18 \times 10^{-6} \times 1.8 \times 10^{-6}}} = 7\text{mV @M} = 1$$

差動入力であるから、2つの入力トランジスタ間のしきい値ばらつきは

$$\Delta V_{th}^{2}$$

diff  $(\sigma) = \Delta V_{th1}^{2}(\sigma) + \Delta V_{th2}^{2}(\sigma)$

$\Delta V_{th}(\sigma) = 7 \text{mV}$  の場合は

$$\Delta V_{th}$$

diff  $(\sigma) = 10$ mV

入力差動対のしきい値ばらつきでオフセットはほとんど決まってしまう。

- 1. ADCの基本機能

- 量子化

- サンプリング定理

- 2. ADCの性能表現

- 3. ADCの主要な変換方法

- 変換アーキテクチャの概要とトレンド

- 4. ADCの設計例

- SAR ADC

- 5. ADCの評価方法

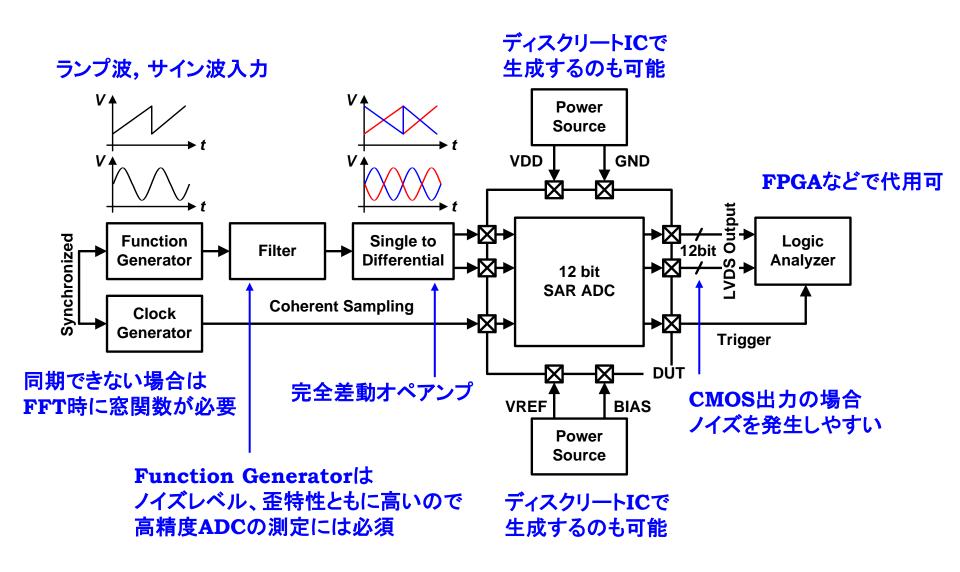

## ADCの評価方法 構成例

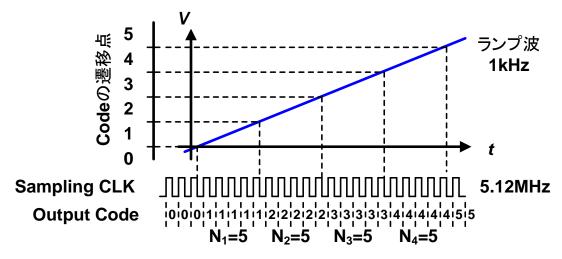

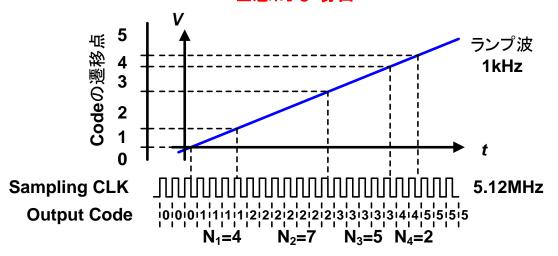

## ADCの評価方法 静特性

#### 理想的な場合

非理想的な場合

一般的に、静特性(DNL,INL)はランプ波入力時のヒストグラム法で行われる。

データポイントを大きく取れば1LSB 以下の精度で算出可能

$$DNL = \frac{N_{\rm i} - N_{\rm IDEAL}}{N_{\rm IDEAL}}$$

$$N_{\text{IDEAL}} = \frac{N_{\text{cycle}} f_{\text{s}}}{2^N f_{\text{in}}}$$

f。:サンプリング周波数

$f_{\text{in}}$ :入力周波数

$N_{

m IDEAL}$ : 理想的な場合のコード出現回数

N<sub>cvcle</sub>:ランプ波繰り返し入力回数

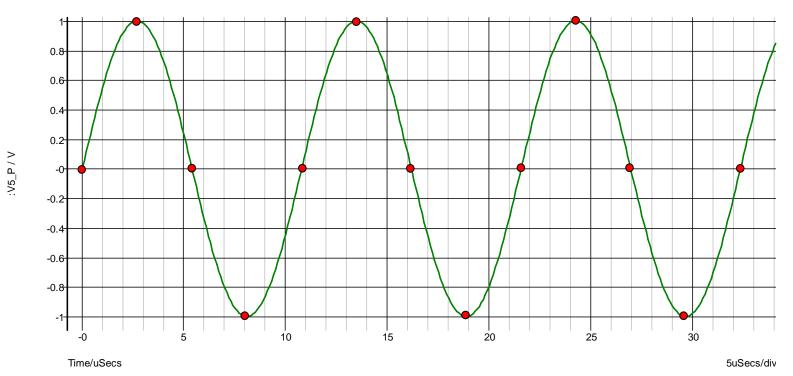

- FFT(DFT)解析によりSNR, SFDR, THD, SNDRなどを求める。

- ・サンプリング周波数と入力周波数、およびFFTポイント数に注意を払う必要がある。

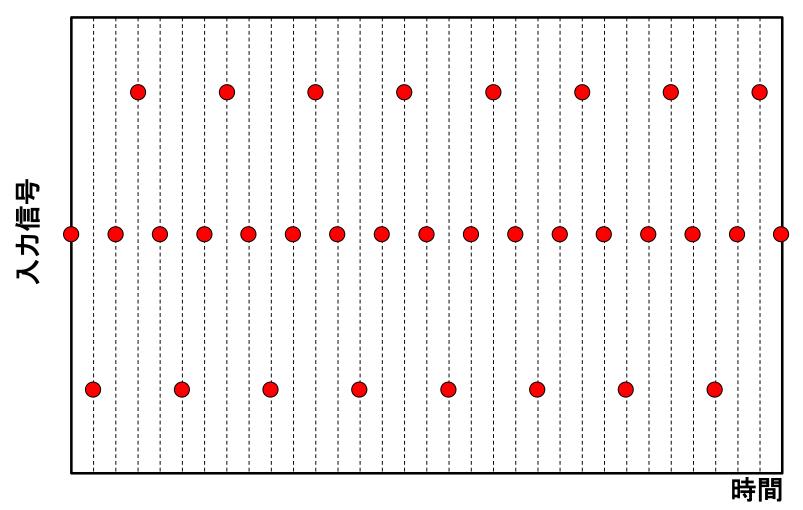

# コヒーレントサンプリングの必要性

サンプリング周波数と入力周波数が偶数倍の場合、繰り返し同じコードを 出してしまいすべてのコードを評価できない。

Fin=Fs/4の場合

アナログ・デジタル変換技術

ナイキストADCでの問題点

ナイキスト周波数近くの入力信号の特性を見る場合、高調波歪みを特定することが困難である。また、FFTをかけるときの窓関数が特性を変化させてしまう。

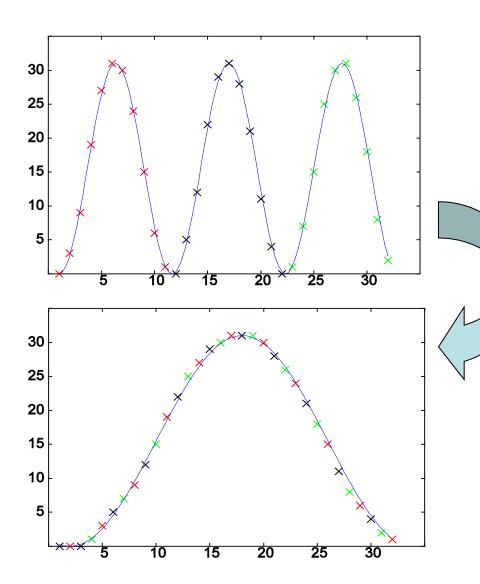

### coherent sampling

入力信号周期の素数または奇数倍の期間サンプリングをしそれを並び替えることによって、信号を仮想的に低い周波数へと変換する方法

これを用いるには

$$N_{cycle} imes T_{sig} = N imes T_{sampling}$$

の関係式を成立させる

N:サンプリング数

N<sub>cvcle</sub>:信号周期の奇数倍

T<sub>sig</sub>:信号周期

T<sub>sampling</sub>:サンプリング周期

並び替えの例

N<sub>cycle</sub>:3

N:32

coherent sampling

によってデータを並び替えると 一周期の信号へと変換できる

この例ではサンプリング周期を 11倍し、11個ずつ飛ばしながら データを並び替えている。 この周波数関係でFFTを行い、 SNR, SFDR(p.27参照)等を求める。

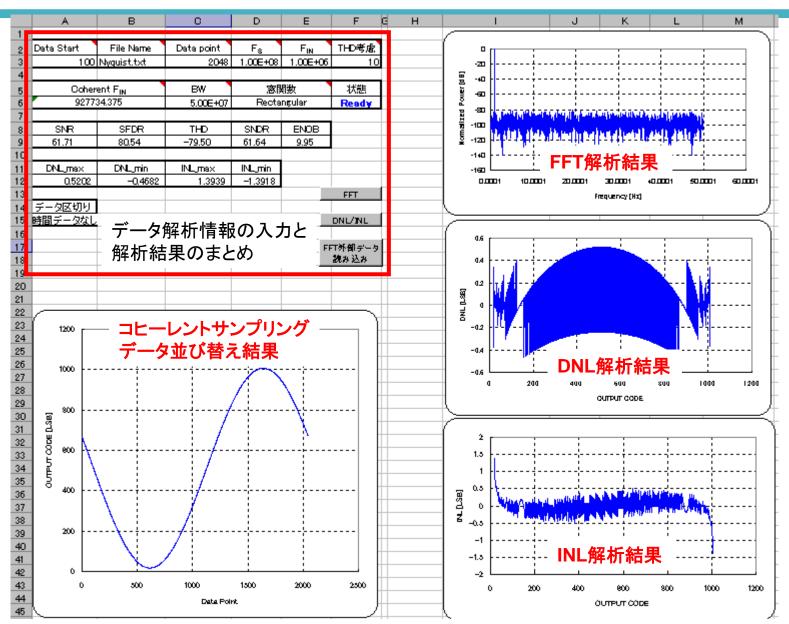

### ADCの動的特性を解析する上で役立つ ADC解析ツールを紹介する。

### ADC解析ツールで出来ること

- ●FFT解析

- ・Rectangular, Hann, Hamming, Blackmanが選択可能

- ·信号帯域を設定可能(ΣΔADCの解析が容易)

- ●コヒーレントサンプリング周波数の算出

- ●ADCの動的性能の自動算出

- SNR, SFDR, THD, SNDR, ENOB

- ●サインフィッティングによるDNL, INLの算出

- ●その他

- ・コヒーレントサンプリングのデータ並び替え機能

- •複数のデータタイプに対応(csv, タブ区切りなど)

(本ツールを使用してみたい方は masaya@post.kek.jp までご連絡ください)

# 表示画面の解説

アナログ・デジタル変換技術

- DNL, INLなどの線形性評価にはランプ波を入力し、ヒストグラム法を用いる。

- 十分なデータ点数を取ること。

- 入力信号源の線形性に注意すること。

- 多少ノイズが多くともデータ点数を大きくとればなんと かなる

- SNR, SFDR, SNDRなどの動特性の評価にはサイン波を入力し、FFT解析により信号、雑音、歪などの電力をそれぞれ算出して求める。

- 十分なデータ点数を取ること

- 入力信号源の雑音性能、線形性に注意すること。

- ノイズが大きいとデータ点数を大きくとっても正しくSNR を評価できない。