# J-PARC/MLF ミュオン施設における MPPC型陽電子検出器のFPGA

小嶋健児AB、幸田章宏AB、鈴木 聡C、門野良典AB、宮崎正範D、平石雅俊D、村上武AE、池野正弘AE、内田智久AE、田中真伸AE KEK Open-ItA、KEK物構研B、KEK計算センターC、総研大D、KEK素核研E

Kenji M. Kojima's CV

1991~1993: muon @ KEK

1993~1998: muon @TRIUMF/Columbia U.

1998~2009: Infrared @ U.Tokyo

2009.11~: muon @ J-PARC

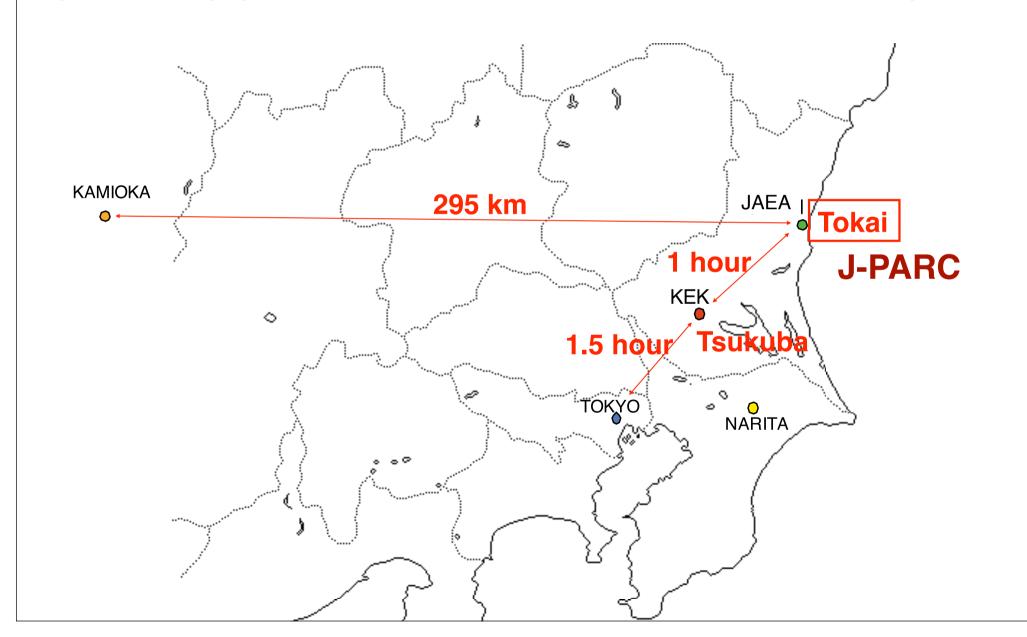

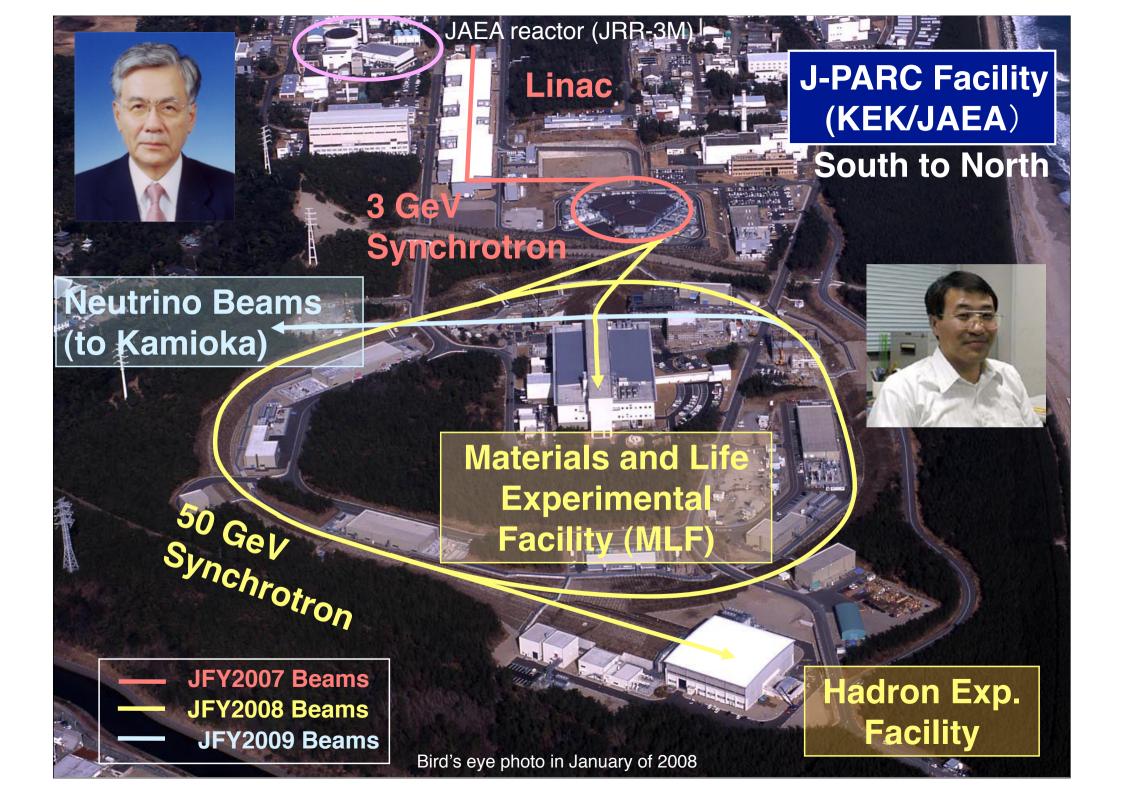

### Present status of J-PARC

J-PARC=Japan Particle Accelerator Research Complex

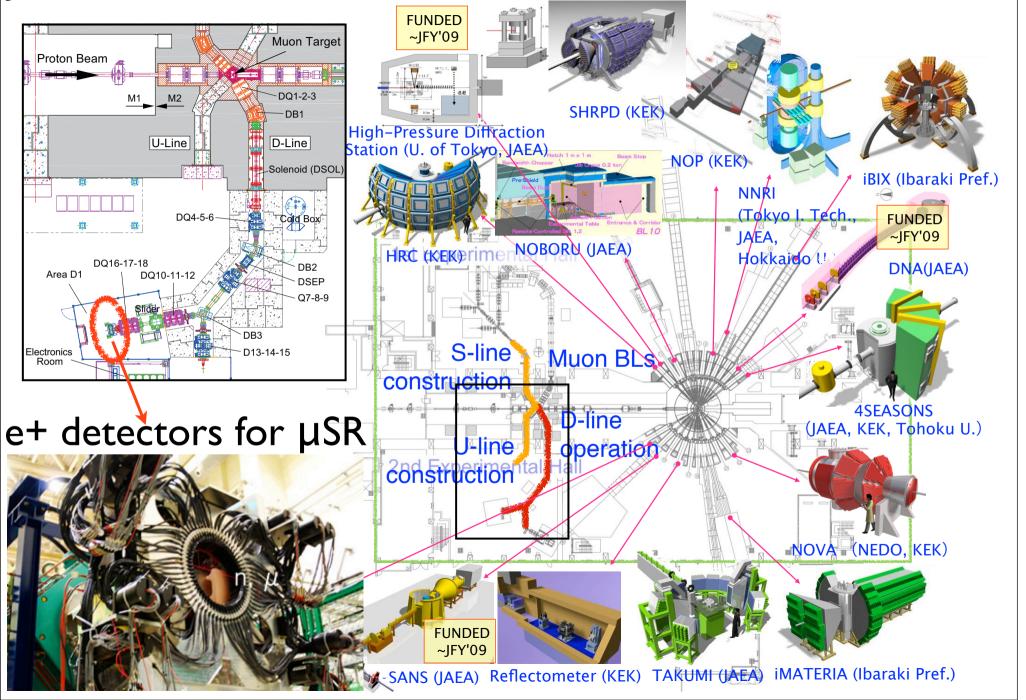

# J-PARC/MLFの中性子施設+ミュオン施設(MUSE)

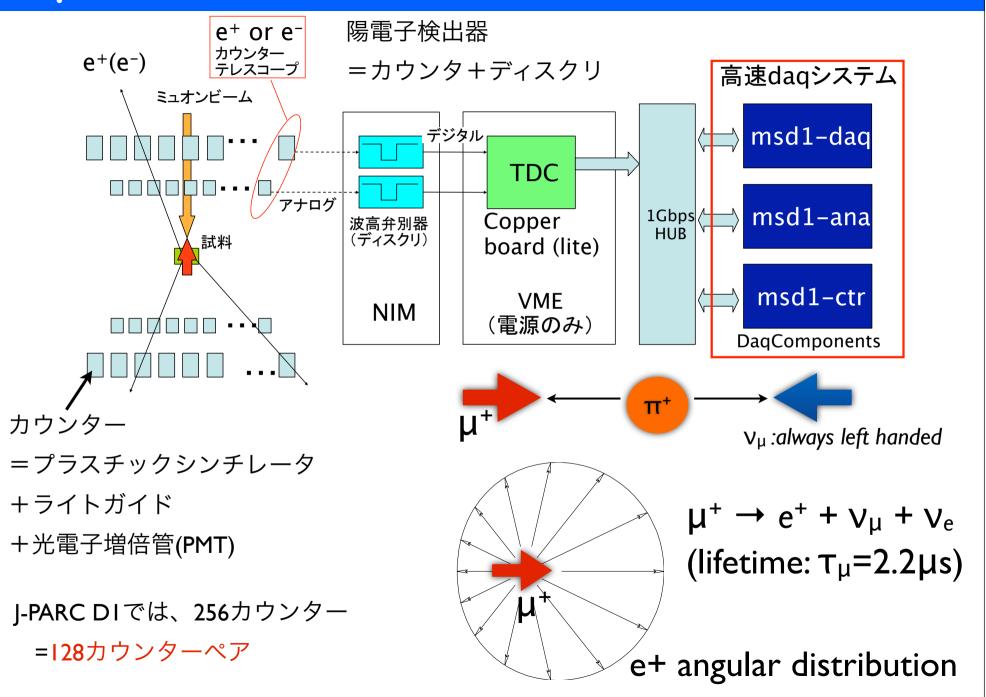

### μSR分光器(パルスミュオン)の概念図

### なぜ多数の陽電子カウンタに細分化するのか?

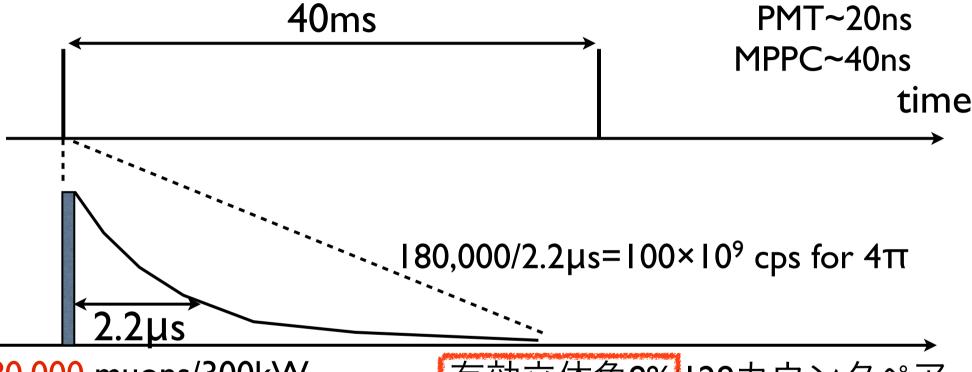

● パルス構造×ミュオン寿命×検出器の不感時間

180,000 muons/300kW φ40mm コリメータ

φI5mmコリメータ100kW

8000 muons/pulse

有効立体角8%/128カウンタペア

→ I00Gcps×0.08/I28=40Mcps or I00hits/counter=20ns separation

→5hits/counter=400ns separation

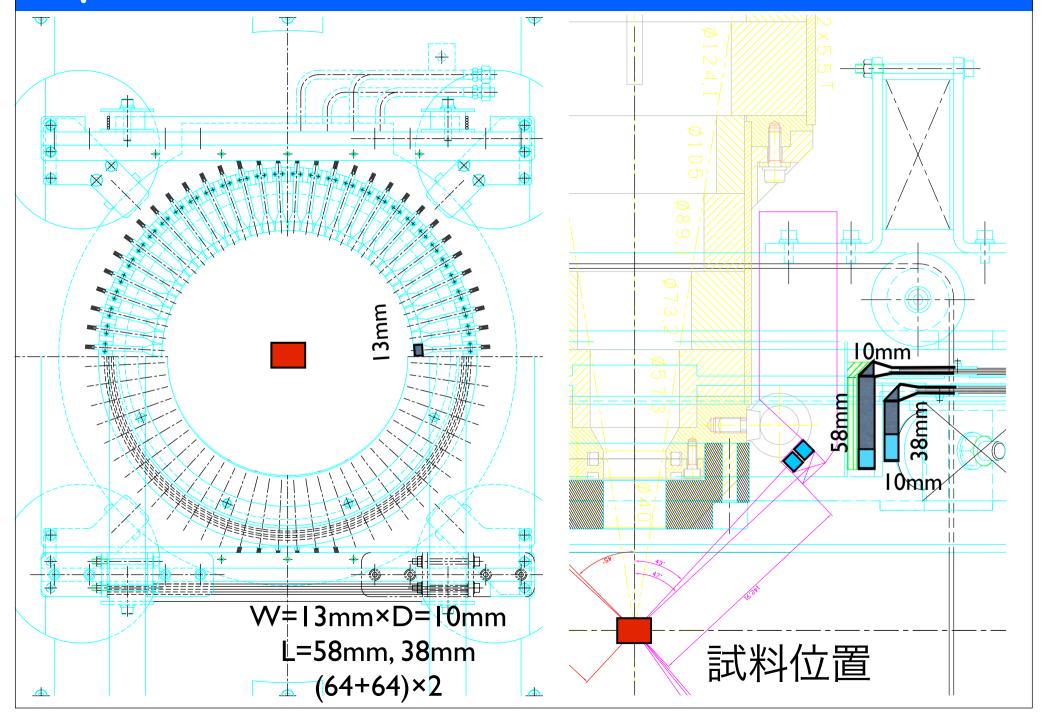

### μSR分光器 (DΩ1) のカウンター増強計画

### MPPCベース新型陽電子検出器開発

$D1汎用\mu SRスペクトロメータ(D\Omega1)$ は 陽電子検出器の立体角が5%しかない。

→RIKEN/RAL並に増強したい。

大強度=検出器の細分化の必要あり。 光電子増倍管は価格が高い、磁場に弱い。 →半導体ベースの検出器(MPPC)へ。

シンチ#1

シンチ#2

WLSファイバ

サポート

MPPC#1&2

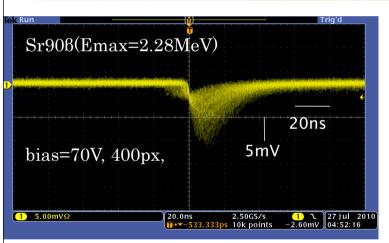

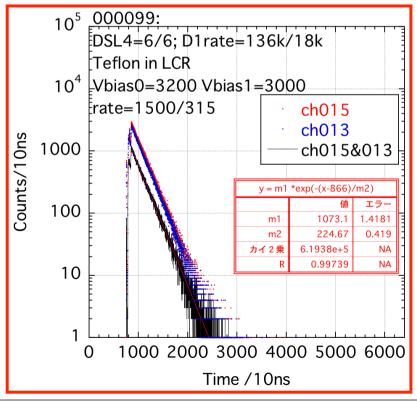

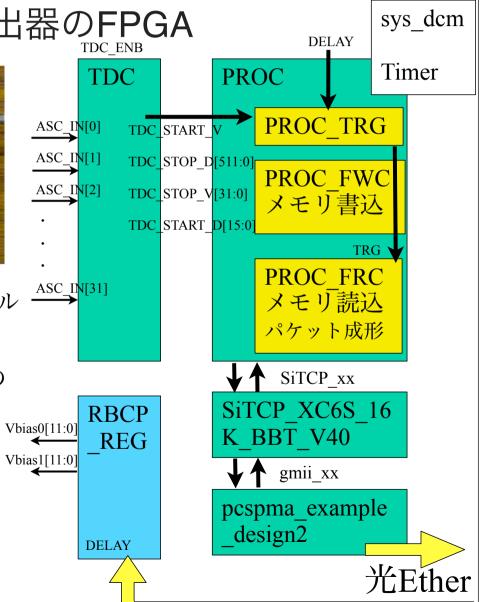

KEK素核研・計算機センターの助けを借りて 陽子パルスからミュオン崩壊陽電子信号までの 時間をメモリに保存し、TCPパケットでPCに送る システムを開発。NIMモジュール不要。 32チャンネルの検出器1ブロックから 1本の光イーサネットケーブルだけが出る。 D1にて最初のin-beamテスト結果(右図)。 μe崩壊時間スペクトルを確認。量産型を開発中。 受光面1.3mm×1.3mm バイアス電圧~70V 価格:約3000円/個

Rise-time: <1ns, recovery~40ns

## 失敗談

#### ~スケジューリング~

内田様、皆様、

FPGAのミュオンサイドの担当者になりました、小嶋です。

2010 10/5

小嶋様

FPGA設計をやっていただけると言う事でしょうか。それは期待してしまいます。

サンプルコードをもらった。いろいろ質問したら・・・

小嶋様

10/7

助けたいのは山々なのですが・・・・

細かい事をメールで教えるのは時間がとられてしまい厳しいです。

Webを探すと解説ページが沢山ありますので、それを参照してください。

10/12

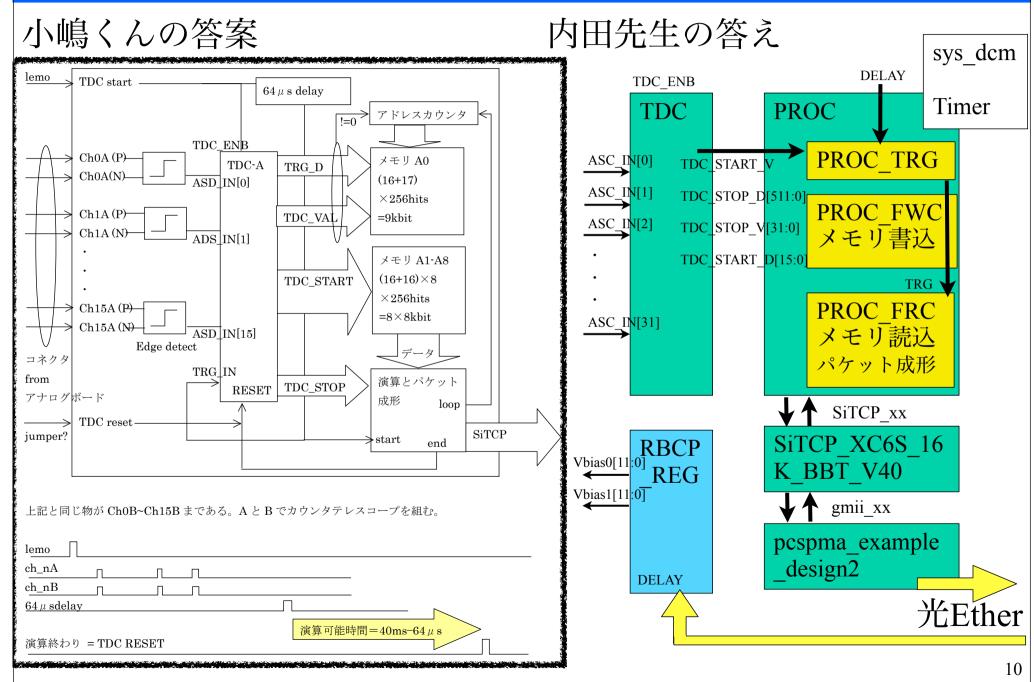

TDCは完成しているのでTDCとSiTCP間の詳細ブロック図を書いてください。

10/20

もうそろそろ、コードを書いてシミュレーションを始めた方が良いと思います。

コードは書けないのでブロック図を書いているうちに

小嶋様

これ以上始める時期が遅れると私の手には負えなく なるので今回は私に作らせてください。

事前に簡単なテストなど行いたいと思っていますので、その時に協力していた だけると嬉しいです。

次回以降は小嶋さんが修正をしていただけると大変助かりますので、完成した コードをシミュレーションしながら理解していただき、新しいコードを組み込 んでいただけたらと思っております。

よろしくお願いいたします。

内田

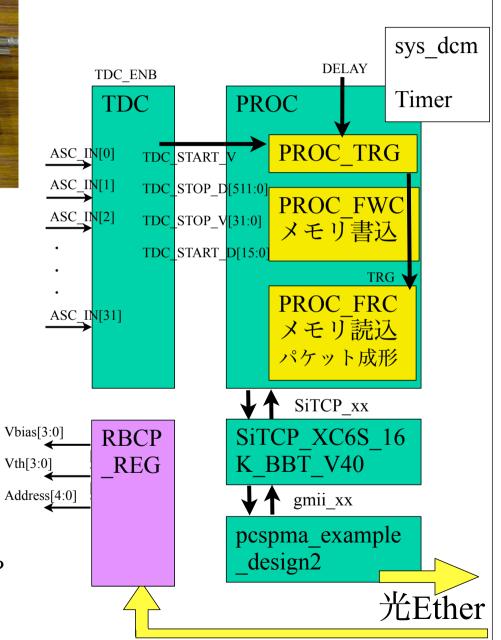

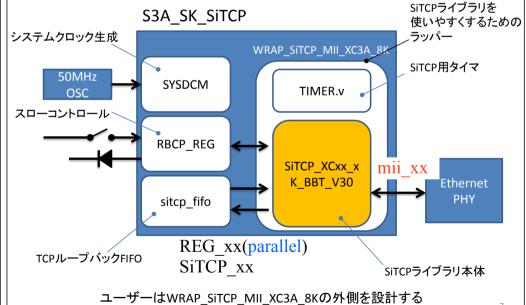

### Block diagram of FPGA code

### Improvement plan

(1) アナログボードの変更

Old ASIC $\mathcal{P} \mathcal{V} \mathcal{P}$ : (1ch)×2

→New ASICアンプ: (8ch)×4に変更

(2) ディスクリ閾値のデジタルコントロール

#### RBCP\_REGを書き換え

Vbias  $0\sim31$

Vthreshold 0~31

コネクタ端子が足りない?MPPCアドレスバス? 32チャンネルfull spec版の完成(FY2011初頭)

### 練習問題とトレーニング

#### 何だか順番が逆ですが・・・

1/6-7に内田先生にマンツーマン演習をしてもらいました。 (本当はFPGAトレーニングコースに出れたら良かったのだが。)

- 1. ISEの使い方(合成から書き込みまで)

- 2. μSR用の各モジュールの説明

- 3. テストベンチの説明とVeritakの使い方

この演習で

→FPGAトレーニングコースを自習

出来るようになりました。 (→2/4完了)

次に

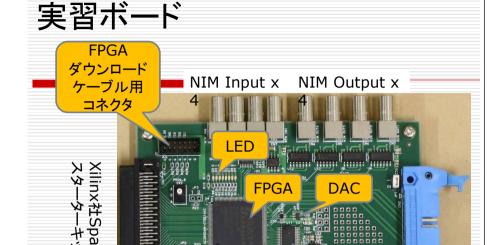

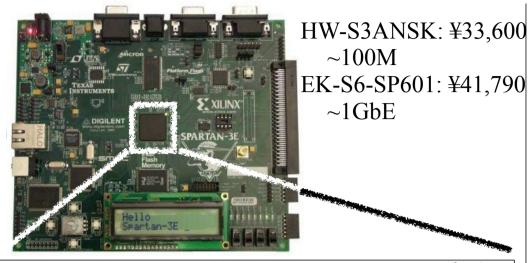

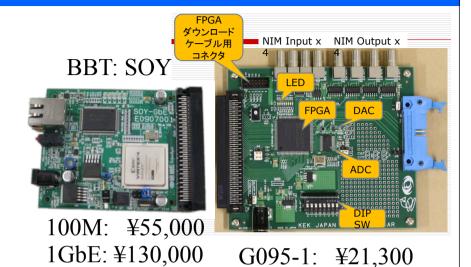

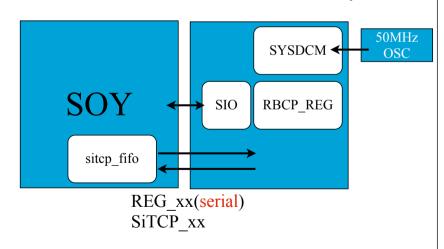

→BBTのSOY(SiTCP)を実習ボードにつないでSiTCPの訓練中。

FPGAトレーニングコースのSiTCPコース (Spartan 3/6 SK使用) のライブラリ (S3A\_SK\_SiTCPなど) がそのまま使えない。コネクタの信号線を読んでUCFを作る必要あり。 信号線がシリアルなので、RBCPにシリアル/パラレル変換 (SIO) が必要。

FPGA seminar 2010

### Xilinx SK vs. BBT SOY+seminar brd

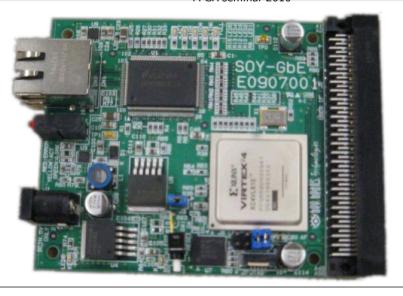

1GbEまで使えて価格が安い。

BBTがSiTCPのライブラリを配布している。

total: ¥76,300

NIM-in/outを使えるが価格が高い。 セミナボードのFPGAはSpartan 3だから、 1GbEは無理?

13

### まとめ

#### J-PARC/MLF ミュオン施設における

MPPC型陽電子検出器のFPGA

(1) 最初のビーム実験で、μe崩壊時間スペクトル ASC\_IN[31] は確認された。

(2) 2chテスト用アナログボードから、32ch用の アナログボードの変更が予定されている。

Old ASIC:  $(1ch) \times 2 \rightarrow New ASIC(8ch) \times 4$

- (3) ディスクリ閾値のデジタルコントロールも 予定されている。

- → RBCP\_REGの書き換え

### OpenITへの要望・提案

ゼロからのFPGAプログラミングを始めてみて・・・

#### FPGAトレーニングコースは重要:

最低限ISE、veritakなどのツールの使い方が分からないと始められない。 →年2回開催されるとうれしい?

#### 質問できる場が必要:

FPGAフォーラムのような掲示板サイト?BBTのSiTCPサイト?OpenIT-FPGA-ML? 書込んですぐ応答があるぐらいの人口があるのか?

手近な人=内田先生=に質問が集中するとおそらくパンクする。

初心者はウェブで検索するキーワードが分からない。(「概念」の検索は難しい)

#### 共通言語=ライブラリの整備がおそらく重要

BBTの配布しているライブラリがどれくらい一般的なのかよくわからない。 ハードウェア依存をどこまで許せるか。