# ネットワークベースDAQに対応した MPPC多チャンネル読み出しボード の開発

東北大学 原子核物理研究室 塩崎 健弘、 三輪 浩司、 本多 良太郎、 赤澤 雄也

KEK Open-It 池野 正弘、 内田 智久

#### 発表すること

- •J-PARC E40実験

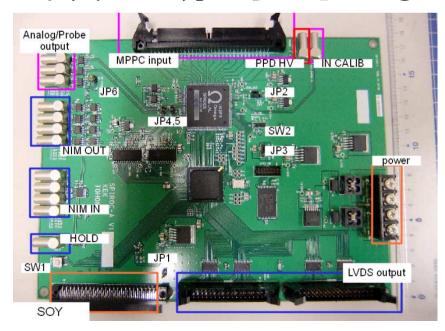

- EASIROCテストボード

- 只今製作中のボード

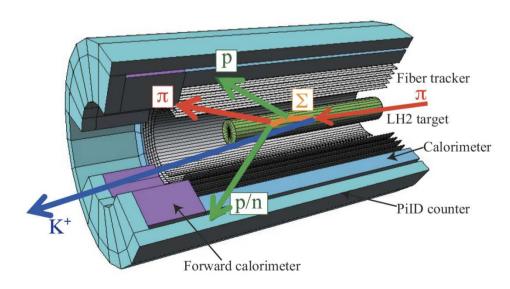

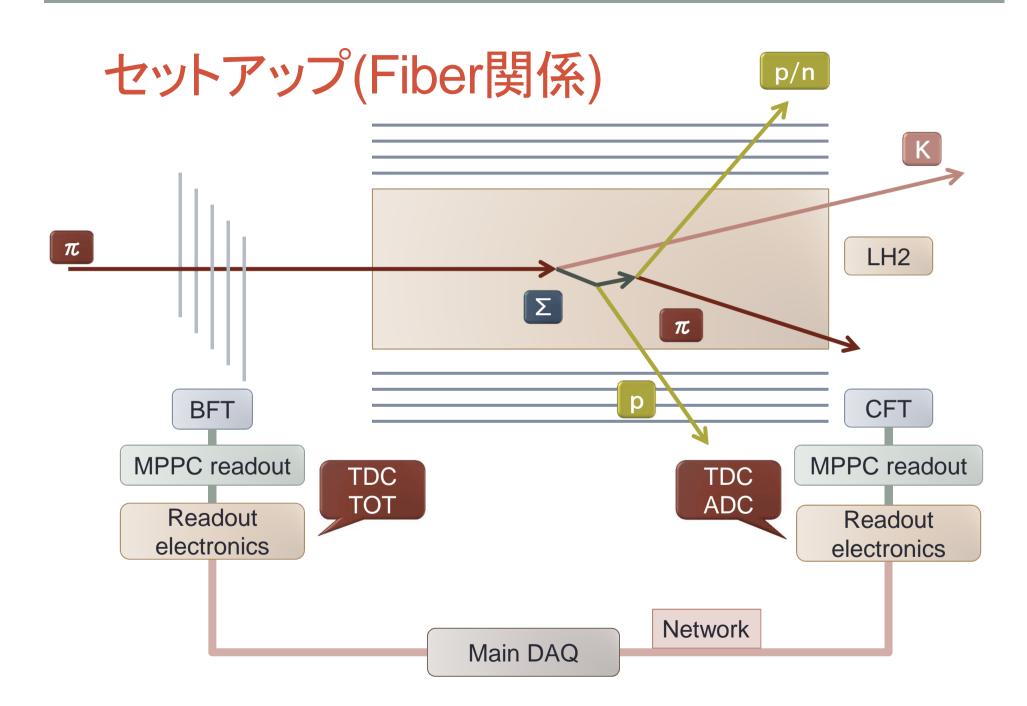

# J-PARC E40 Σp散乱実験

Σp散乱におけるdσ/dΩの測定

特徴: Σの運動量を直接測定せずに運動学的に再構成する

・散乱pの飛跡を検出するためのファイバートラッカー(CFT)を 製作中

#### 要求性能

- •5000~10000ch

- ADC, MHTDC

- Beam rate 10MHz

- Trigger rate 3kHz

- MPPCのゲイン調整

- ネットワークでデータ転送

- 非同期トリガー

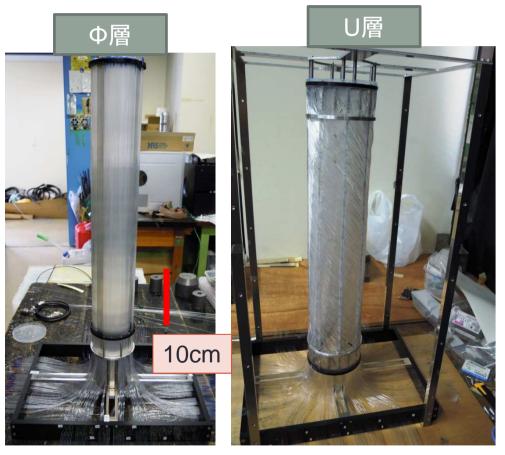

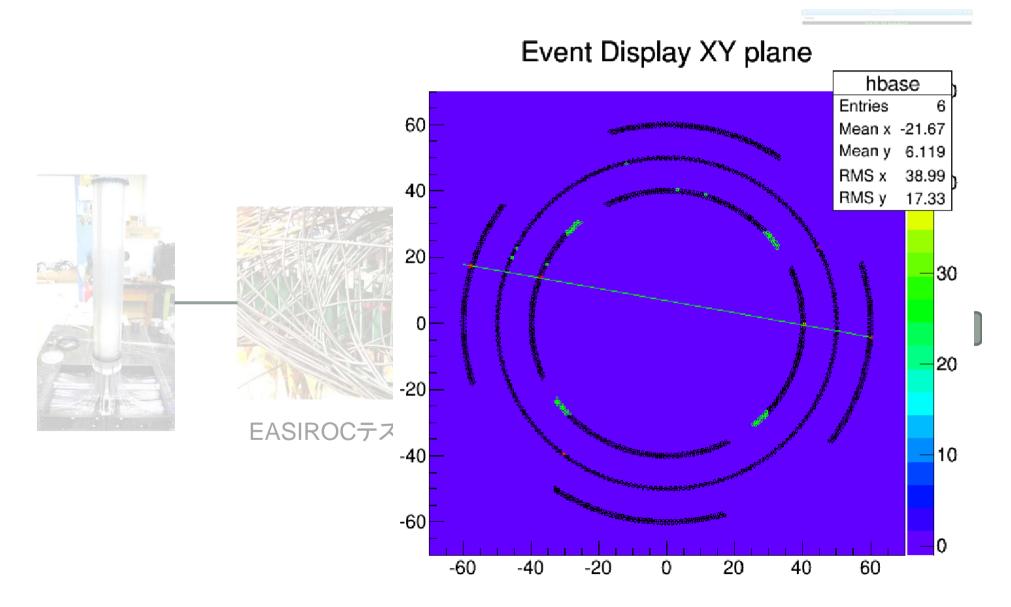

#### CFTプロトタイプ

- Φ層×2 U層×1の3層構造

- Φ1層 384ch

- U層 448ch

- Φ2層 384ch

- 合計 1216ch

• 7/24に東北大学サイクロトロンRI研究センターにて性能評価

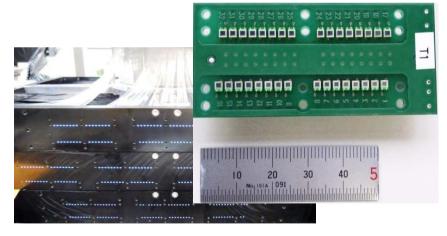

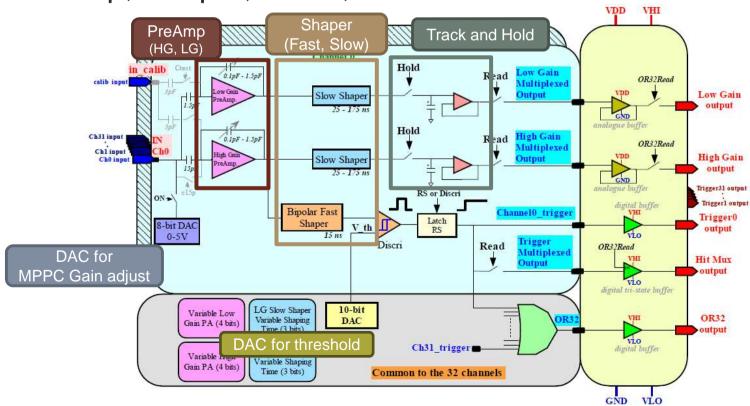

#### **EASIROC**

- OMEGA/IN2P3によって作られたMPPC読み出し用のASIC

- 1chipで32chのMPPCに対応

- PreAmp, Shaper, Discri, MPPCゲイン調整用DAC等の機能

#### MPPC readout

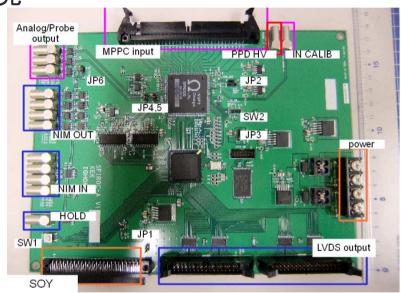

• MPPC readoutとしてEASIROCボードを開発

歴史 2011/04 EASIROCテストボード完成

2012/12 EASIROCテストボードがJ-PARC E10実験で beam momentum analyzerとして使用される

現在 EASIROCテストボードの欠点を改良した VME-EASIROCを開発中

# EASIROCテストボードの実績

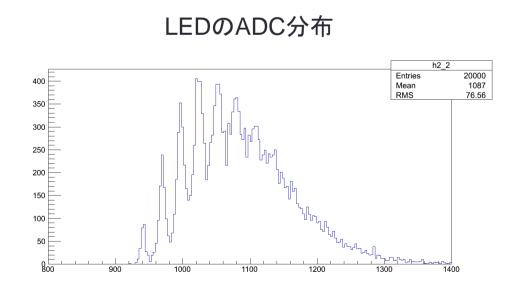

- EASIROCの制御方法を学べた

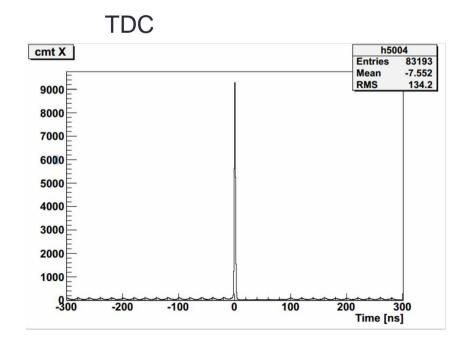

- FPGA内にMHTDCを実装できた(LSB=1nsでLeadingとTrailing)

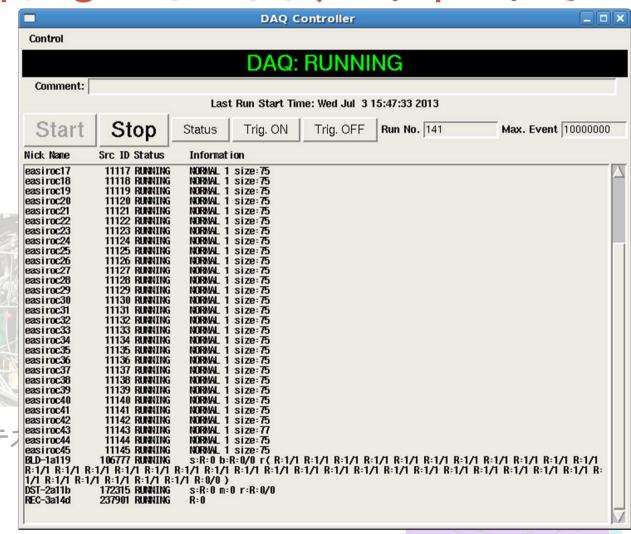

- SiTCP(SOY)を用い、ADCとMHTDCのデータをネットワーク経由で取得できた

- J-PARC E10実験に1500ch程度を読みだした

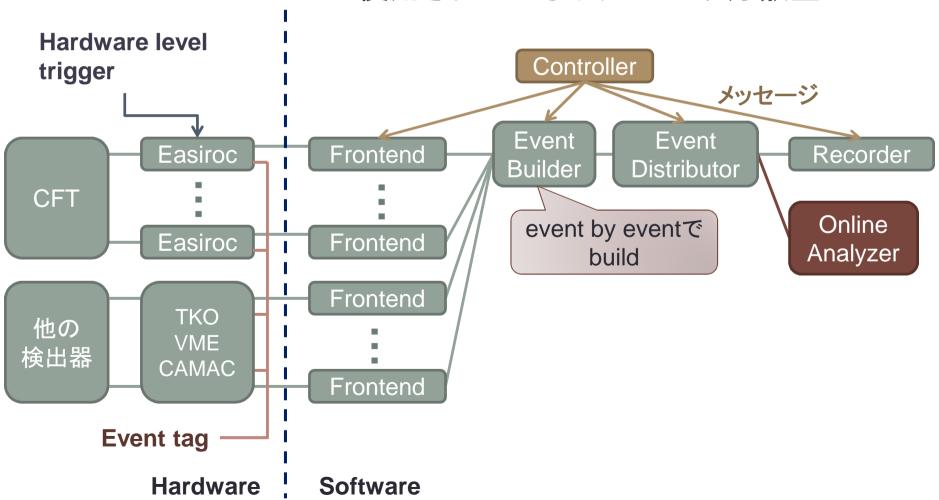

#### ハドロンDAQ

• J-PARC K1.1/K1.8で使用されているネットワーク分散型DAQ

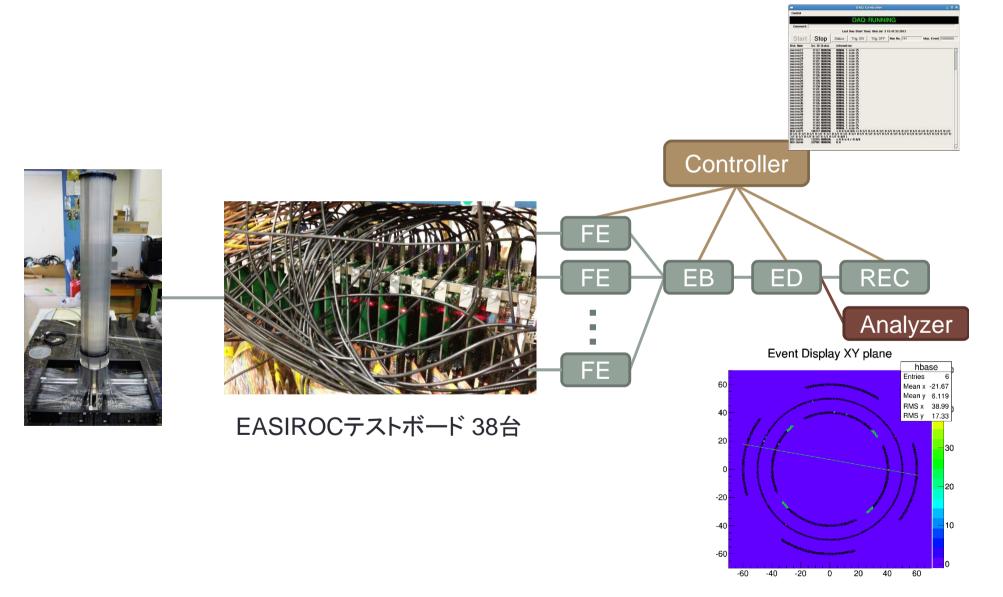

#### CFTプロトタイプもEASIROCテストボードで

#### CFTプロトタイプもEASIROCテストボードで

EASIROCT.

#### CFTプロトタイプもEASIROCテストボードで

#### EASIROCテストボードの問題点

- ADC周りの整備が不十分に終わってしまった

- SiTCPを外付け(SOY)にしてしまった

- イベントタグ非対応(強引な方法でLSBのみ受け取る)

- 基板が独自規格なので既存のクレートに挿せない

- コネクタが四方から生えているためケーブルの取り回しが面倒

# ここから新ボードの話

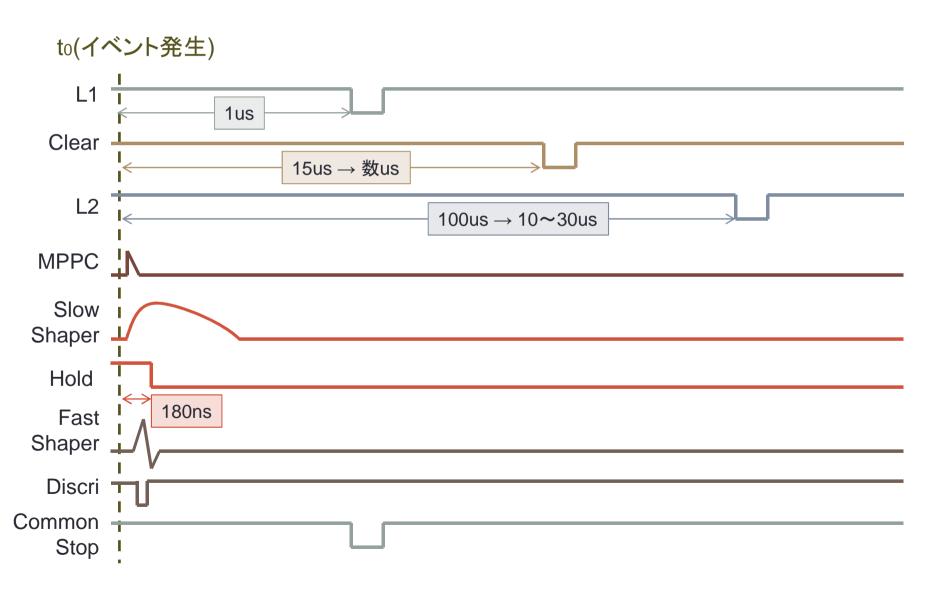

### タイミングチャート

#### 作るボードの仕様

- MPPC 64ch (EASIROC × 2)

- ADC

Deadtime 10us -

L2トリガーに間に合わせる

**Fastclear**

Zero suppression

MHTDC テストボードにLSB 1ns 搭載しているものをほぼ流用

window 可変

Deadtime 10us

Fastclear

DAQ

SiTCP 100Mbps ダブルバッファ COPPER Trigger 非同期動作 L1, L2, clear, Busy, EventTag

# 性能比較 (新 vs 旧)

|                  | EASIROC テストボード  | VME EASIROC     |

|------------------|-----------------|-----------------|

| ch数              | 32 (EASIROC ×1) | 64 (EASIROC ×2) |

| FPGA             | Spartan-6       | Artix-7         |

| SiTCP            | SOY(外付)         | FPGA内蔵          |

| 基板規格             | 独自              | VME 6U          |

| 電源               | 端子台             | VME J1          |

| ADC Fastclear    | ×               | 0               |

| Zero suppression | ×               | 0               |

| Deadtime         | 100us           | 10us            |

| MHTDC window     | 1us固定           | 可変              |

| イベントタグ           | 非対応             | 対応(VME J0)      |

| イベントバッファ         | シングル            | ダブル             |

#### 現状

・ 業者への発注が完了

• 9月にプロトタイプを納入してもらう予定

#### まとめ

J-PARC E40実験のためにネットワークでデータ収集可能な EASIROCボードを製作中

EASIROCテストボードではMPPPC 1500chのADC、MHTDC(LSB=1ns)をネットワークで取得することに成功

しかし、ADC周りの整備が不十分、イベントタグ非対応、基板が独自規格といった問題があった

これらの欠点を改良したボードVME-EASIROCを製作中9月ごろに納品してもらい性能評価予定