# 高輝度LHC-ATLAS 実験に向けた TGC 検出器トリガーにおける 前段回路試作機の動作検証

<u>皆川真輝<sup>A,B</sup></u>、戸本誠<sup>A, B,C</sup>、堀井泰之<sup>A,B</sup>、加納勇也<sup>A,B</sup>、山田敏大<sup>A,B</sup>、佐々木修<sup>B,C</sup>、田中真伸<sup>B,C</sup>、宮原正也<sup>B,C</sup>、池野正弘<sup>B,C</sup>、庄子正剛<sup>B,C</sup>、田内一弥<sup>B,C</sup>、他ATLAS 日本トリガーグループ

名大理A、Open-ItB、KEK素核研C

日本物理学会第76回年次大会

### はじめに

#### 高輝度LHC-ATLAS実験

- 2027年からLHC加速器を高輝度化する。

- 瞬間ルミノシティが現行の2.5倍以上に増強される。  $(5-7.5\times10^{34}\,\mathrm{cm}^{-2}\mathrm{s}^{-1}$ に到達予定)

- → ATLAS実験でのトリガー・読み出し回路の改良が要請される。

#### ATLAS検出器

### Thin Gap Chamber (TGC)

- エンドキャップ部トリガー用ミューオン検出器

- トリガー回路の刷新を行う。

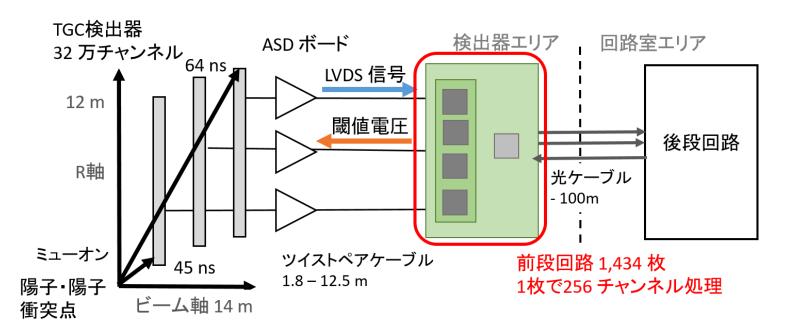

## 新たなTGCトリガー回路

### TGC全ヒット情報をもとに高速飛跡再構成

ASDボード

- TGC検出器信号の 増幅・成形・弁別

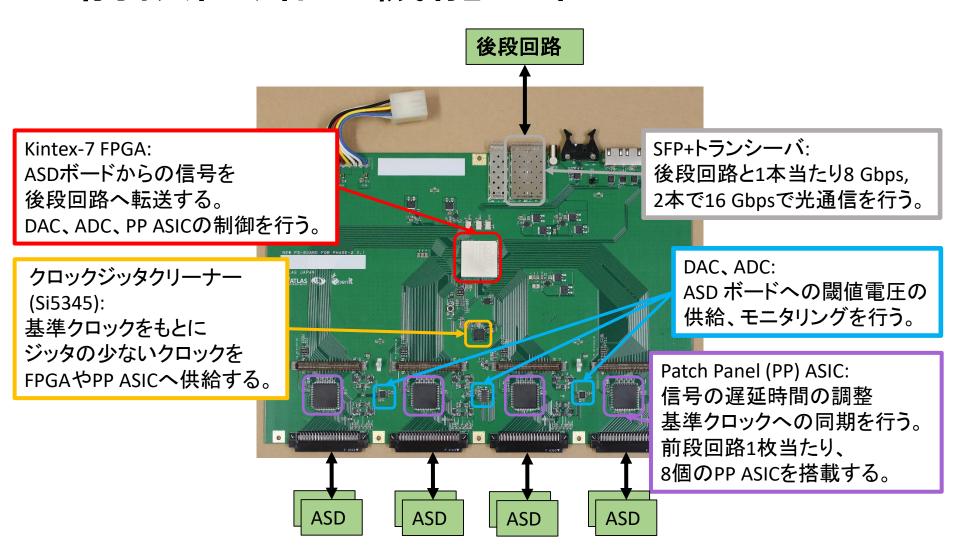

#### 前段回路

- 信号を基準クロックへ同期

- 信号を後段回路へデータ転送

- ASDボードへ閾値電圧の供給

#### 後段回路

- ミューオン飛跡を再構成

- 横運動量をもとにトリガー (14pT3-10 小林蓮 14pT3-11 三森由暉)

日本物理学会第76回年次大会

### 前段回路の機能と素子について

日本物理学会第76回年次大会

### 前段回路の開発タイムライン

2018 2019 2022 2025 2020 2021 PP ASIC 試作機 製作•検証 PP ASIC 量産品 量産•品質試験 前段回路第1試作機 前段回路 PP ASIC 量産品 製作•検証 第1試作機 前段回路第2試作機 製作•検証 前段回路最終機 本発表 量産•品質試験

インストール

### PP ASIC: 概要

| 構成要素        | 機能                                              | 仕様                                       |

|-------------|-------------------------------------------------|------------------------------------------|

| 可変遅延回路      | TGCからの信号のチャンネル間の<br>遅延時間の補正を行う。                 | 刻み幅:<1 ns<br>ダイナミックレンジ: >40 ns           |

| 陽子•陽子交差識別回路 | 基準クロック(40 MHz)と信号を同期<br>させ、 <b>陽子交差に割り当てる</b> 。 | 有効ゲート幅: 25 - 49 ns                       |

| テストパルス生成回路  | テストパルスをASDボードへ発行し、<br><b>回路系の動作試験</b> を行う。      | 波高: 60 mV - 2.8 V<br>幅: 25 ns - 102.4 μs |

#### その他の仕様

- プロセス: Silterra 0.18 µm CMOS

- チャンネル数: 32 チャンネル

(16 チャンネル×2)

- 供給電圧: 1.8 V (一部で 3.3 V使用)

- 消費電力: ~75 mW

PP ASIC  $(2.5 \text{ mm} \times 2.5 \text{ mm})$

### PP ASIC: 量産品試験について

- FPGA搭載のテストボードを用いた自動品質試験システムを構築した。

- FPGAでPP ASICに対する信号送受信とPCに対するデータ送受信を行う。

- 1個あたり40-80 秒で試験が実行可能である。 (日本物理学会2020年9月山田16pSF-6)

#### テスト項目

- 全SPIレジスタ

- 全チャンネル入出力

- 遅延制御回路

- 可変遅延回路

- 陽子バンチ識別回路

- テストパルス回路

- 消費電力

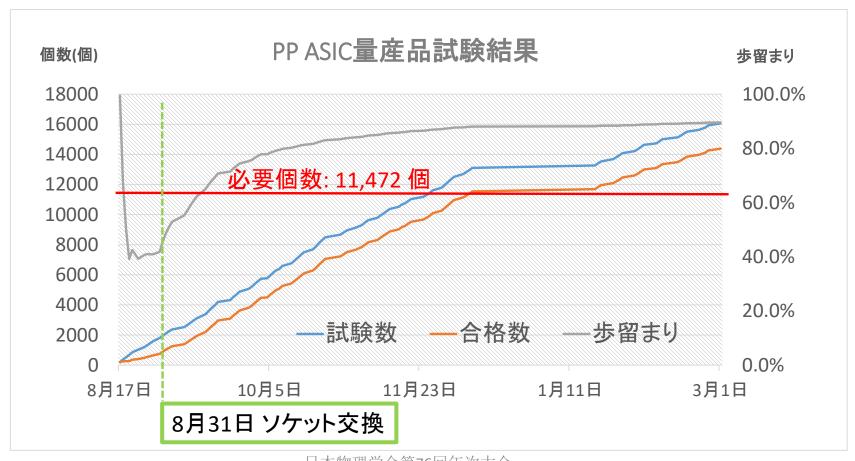

### PP ASIC: 量產品試験結果

- 全チップ25,000 個に対しての自動品質試験が2020年8月から開始された。

- 16,054個のPP ASICの試験を行い、14,375個の合格を確認した。(2021年2月現在)

- 実機で必要な個数を確保した。(必要個数: 11,472 個)

- 一部期間でソケットの不良による歩留まりの悪化が見られたが、改善済である。

日本物理学会第76回年次大会

### 前段回路: 動作検証試験

- ・前段回路第1試作機が2020年9月に納品された。

- 全ての項目で、基準の機能を満たすことを立証した。

- ・閾値電圧供給回路に関して、改良点を明らかにした。

- ・ 改良点をもとに、前段回路第2試作機を製作した。

| 試験項目                                   | 結果             |

|----------------------------------------|----------------|

| FPGA初期化•回復機構                           | ✓              |

| ASDボード接続試験(次ページ以降説明)                   | ✓              |

| クロックジッタークリーナー                          | ✓              |

| PP ASIC                                | ✓              |

| SFP+トランシーバー                            | ✓              |

| <u>閾値電圧供給回路(DAC,ADC)</u><br>(次ページ以降説明) | ✓<br>(改良の余地有り) |

| 消費電力                                   | ✓              |

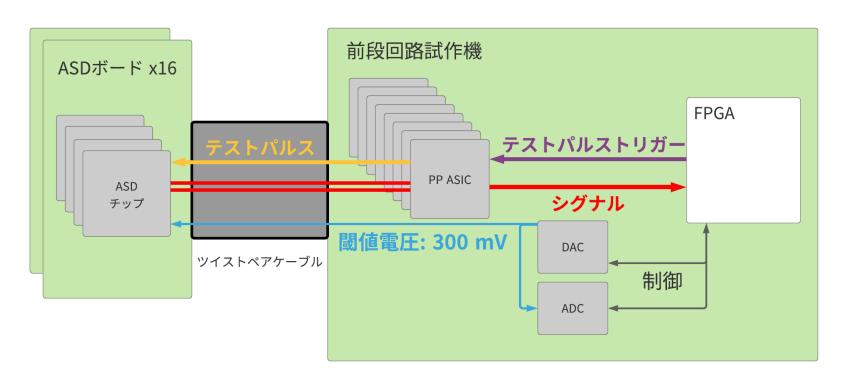

## ASDボード接続試験セットアップ

- ASDボードと前段回路試作機を接続し、データパスを検証した。

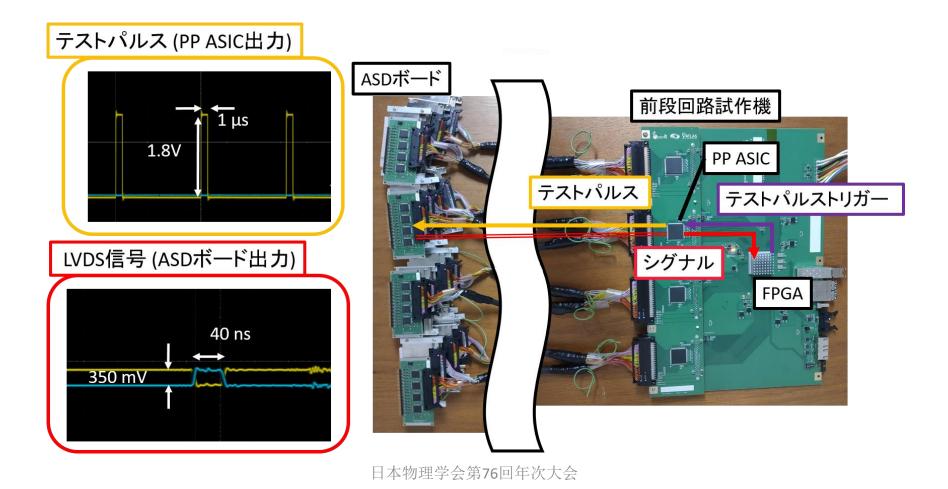

- PP ASICからのテストパルスをもとに、 ASDボードからのLVDS信号をFPGAで検知出来るかを確認した。

- また、それぞれの信号の状態(波高、幅、波形、タイミング)を確認した。

### ASDボード接続試験結果

- 設定や規格に準じた信号がやりとりされていることを確認した。

- ASDボードからのLVDS信号をFPGA上のチップスコープで検知できた。

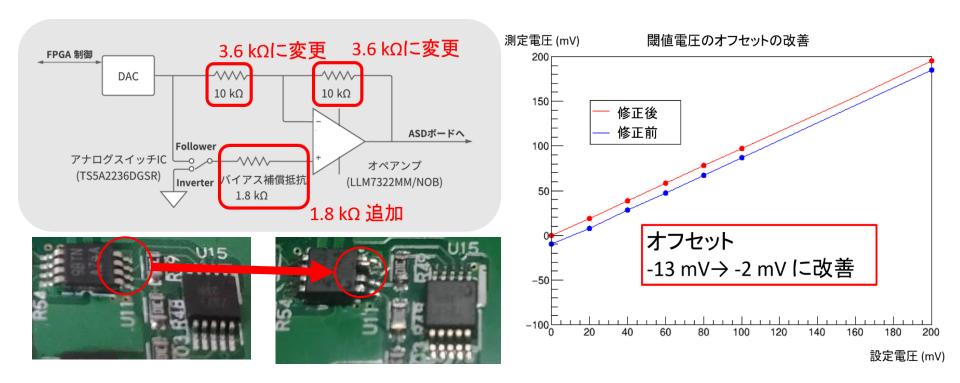

### 閾値電圧供給回路の改良点

- オペアンプのバイアス電流に起因する、-10 mV程のオフセットが存在した。→抵抗値を変更し、バイアス補償抵抗を付け加えた。

- 第1試作機で検証し、オフセットの改善を確認した。

- この改良により、閾値電圧値の設定の利便性の向上をさせた。

### まとめ

高輝度LHC-ATLAS実験に向けたTGC検出器トリガーにおける前段回路開発のために検証を行った。

#### 前段回路搭載PP ASICの量産品検証

- 14,375個 / 16,054個の合格を確認した。(2021年2月現在)

- ・ 実機で必要な個数を確保した。(実機で必要な個数: 11,472 個)

#### 前段回路の試作機試験

- 全ての項目で、基準の機能を満たすことを立証した。

- ・改良点を明らかにし、第2試作機を製作した。(2021年2月納品)

# Back up

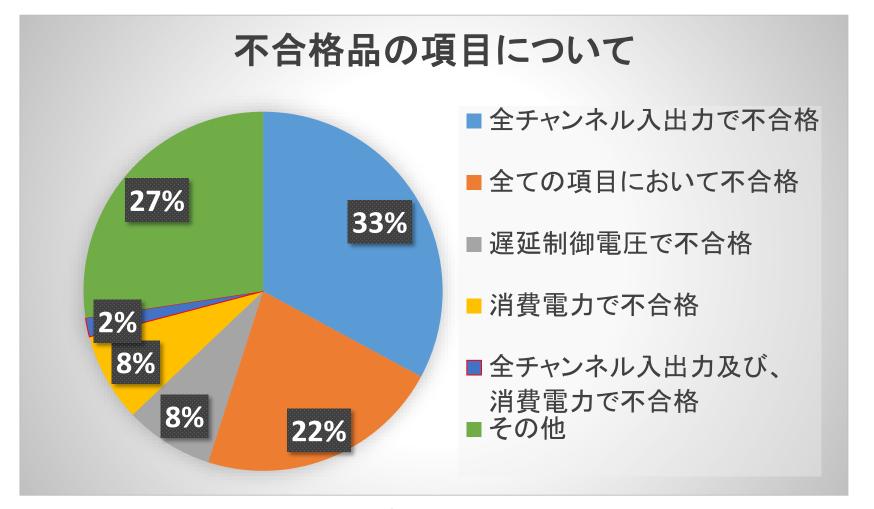

## PP ASIC: 不合格品

(各項目については排他的に個数を計上している。)

日本物理学会第76回年次大会

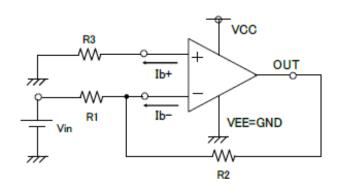

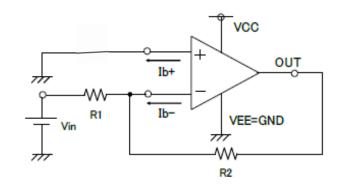

### 入力バイアス電流について

- ・ オペアンプの入力端子に入出力する電流

- バイポーラタイプのオペアンプでは主に入力段のトランジスタに流れるベース電流が要因

- 入力バイアス電流が存在するときは

$$V_{\text{out}} = -\frac{R_2}{R_1}V_{\text{in}} - R_2Ib^-$$

• ここにバイアス補償抵抗R3をオペアンプの+入力端子に加えると、

$$V_{\text{out}} = -\frac{R_2}{R_1}V_{\text{in}} - \left(1 + \frac{R_2}{R_1}\right) \left[ \left(\frac{R_1 \cdot R_2}{R_1 + R_2} - R_3\right) Ib - \left(\frac{R_1 \cdot R_2}{R_1 + R_2} + R_3\right) \frac{I_{\text{io}}}{2} \right]$$

$$(\Box \Box CIb = \frac{Ib^{+} + Ib^{-}}{2}, I_{io} = Ib^{+} - Ib^{-}$$

$I_{io}$ : 入力オフセット電流、+/- 端子のバイアス電流の差)

・

$$R_3=rac{R_1\cdot R_2}{R_1+R_2}$$

とすることで、バイアス電流の影響をキャンセルできる  $V_{

m out}=-rac{R_2}{R_1}V_{

m in}+R_2I_{

m io}$