# **AMC: Analog Memory Cell**

阿部利德 Representing AMC group Analog Memory Cell (以下AMC)の開発の目的、原理、原理、開発現状、今後の展開、について話します。

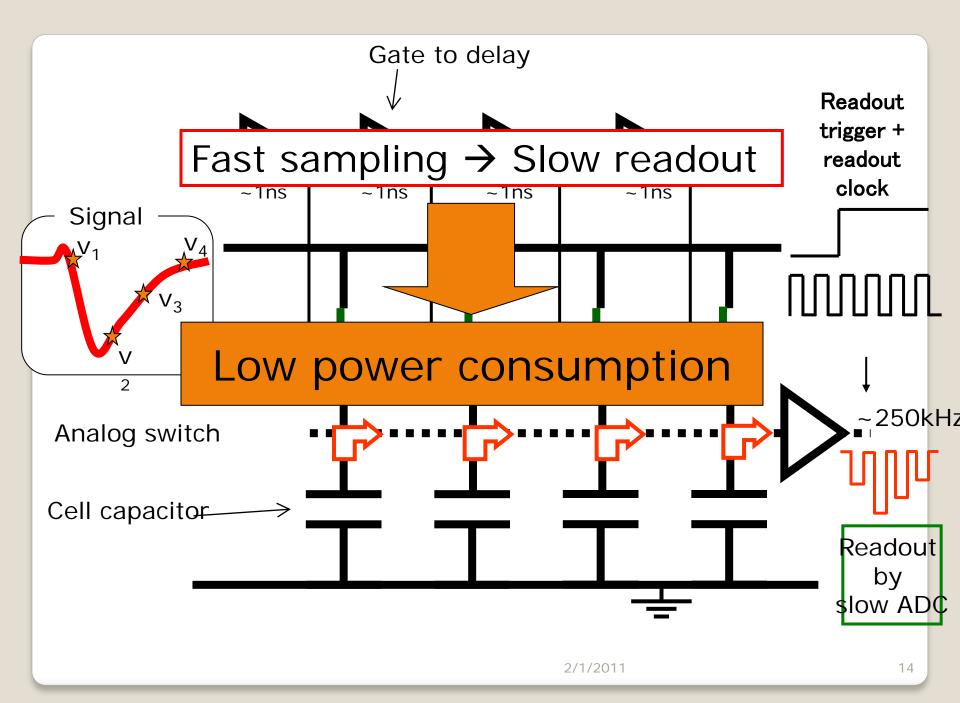

AMCは、高速波形サンプリング(~1 GHz)を高 分解能(≥10bit)で(低消費電力で)行うICです。

### イントロダクション

- 目的

- 動作原理

- ・開発の現状

- ・去年度までのAMCの性能

- UMCO.25umを用いたAMC(遠山、吉越、田中)

- ADC付きAMCとその改良(阿部、藤森、田中)

- 今後

### 冒次

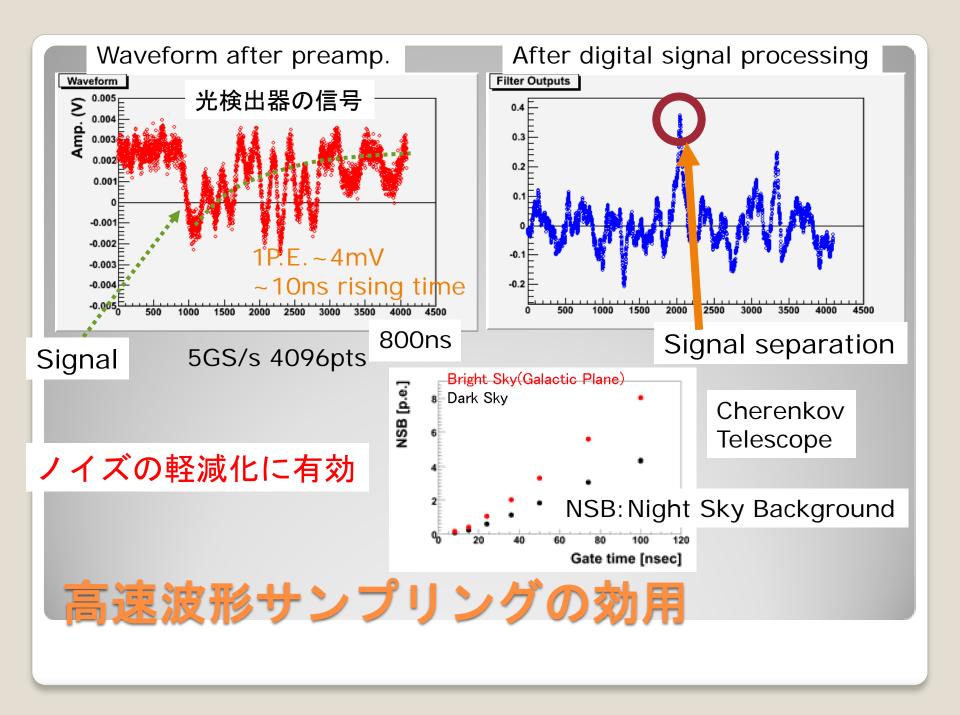

- 高速波形サンプリング(+Digital Signal Processing)を用いた読み出しは、しきい値型 読み出しに比べて、下記の特徴がある。

- 1. ノイズの軽減化に有効

- 2. Flexibilityがある

- 高速波形サンプリングを高分解能で行いたい。

- →AMCで実現

### 目的

- O要求

- 1. GHzの波形サンプル

- 2. 高分解能(≥10bit)

- 3. (低消費電力)

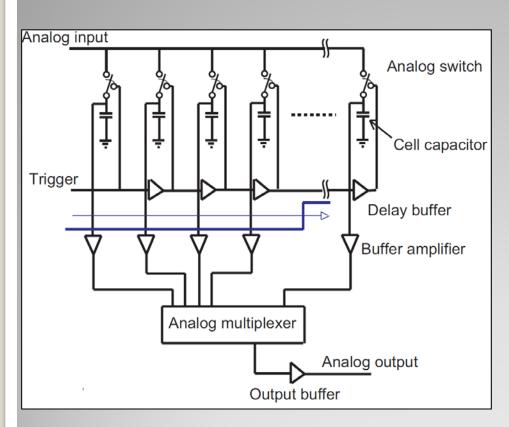

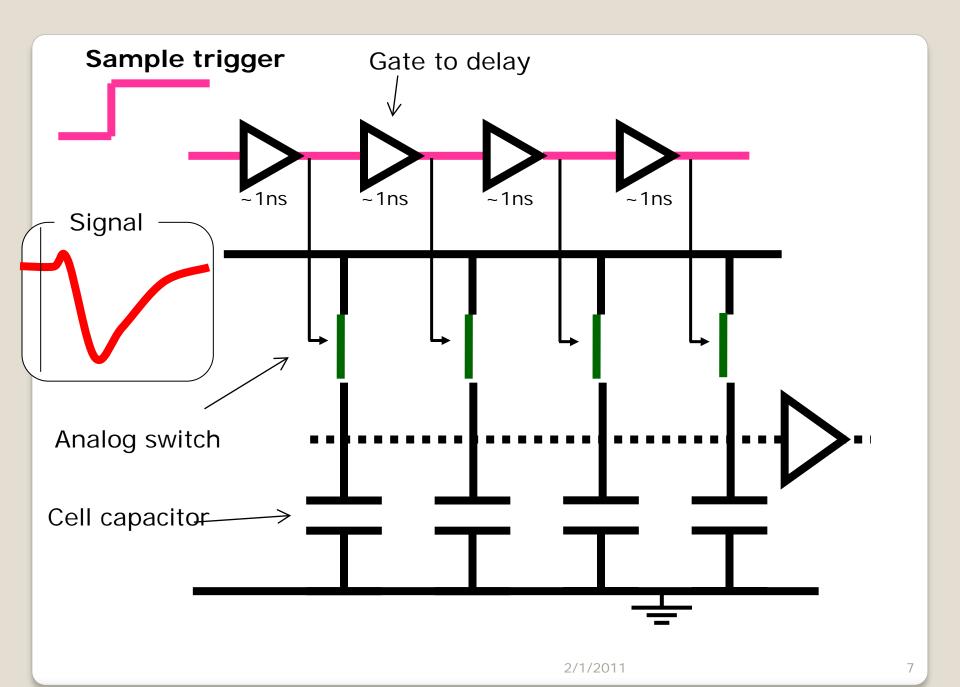

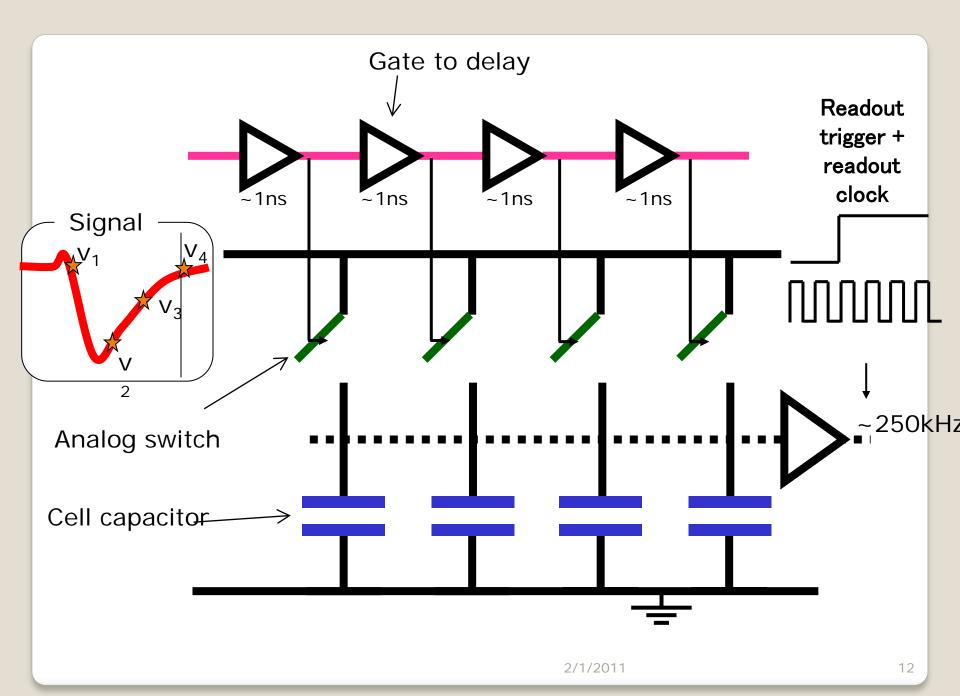

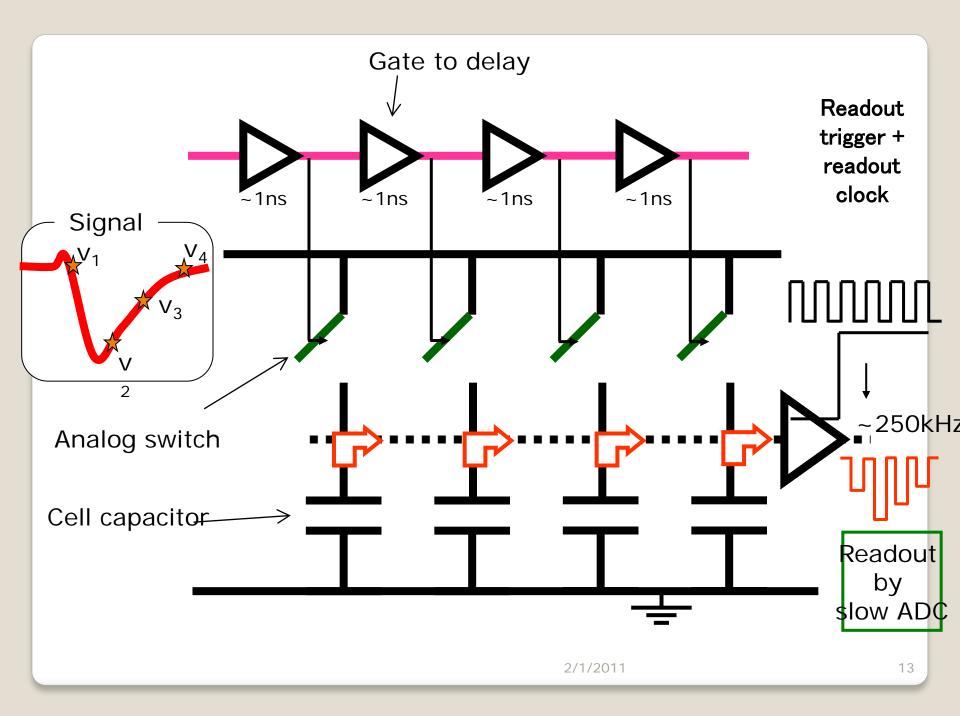

- O AMC

- → Switched Capacitor Array

- →サンプリング時間は 遅延バファアンプ

- →高速外部クロックが 必要ない

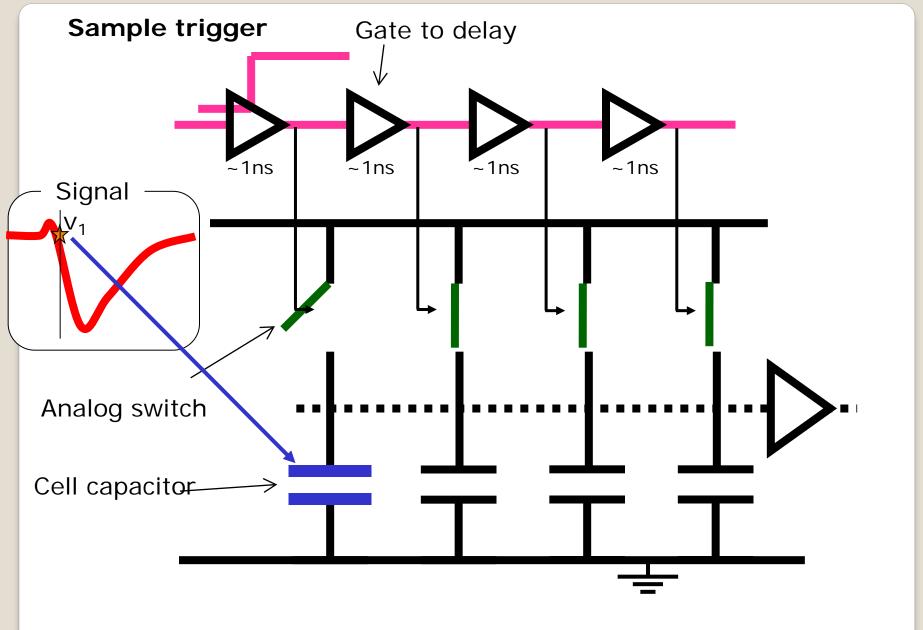

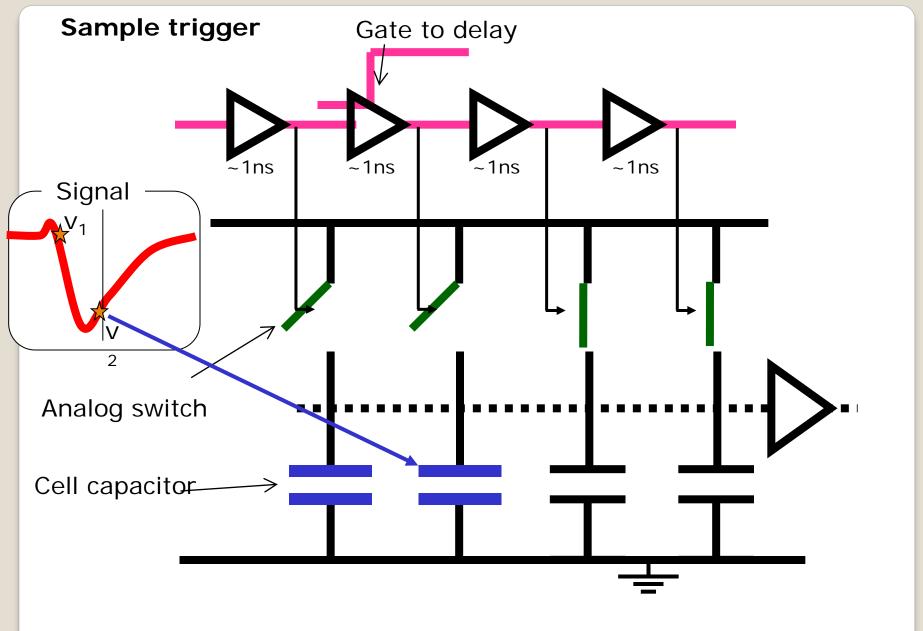

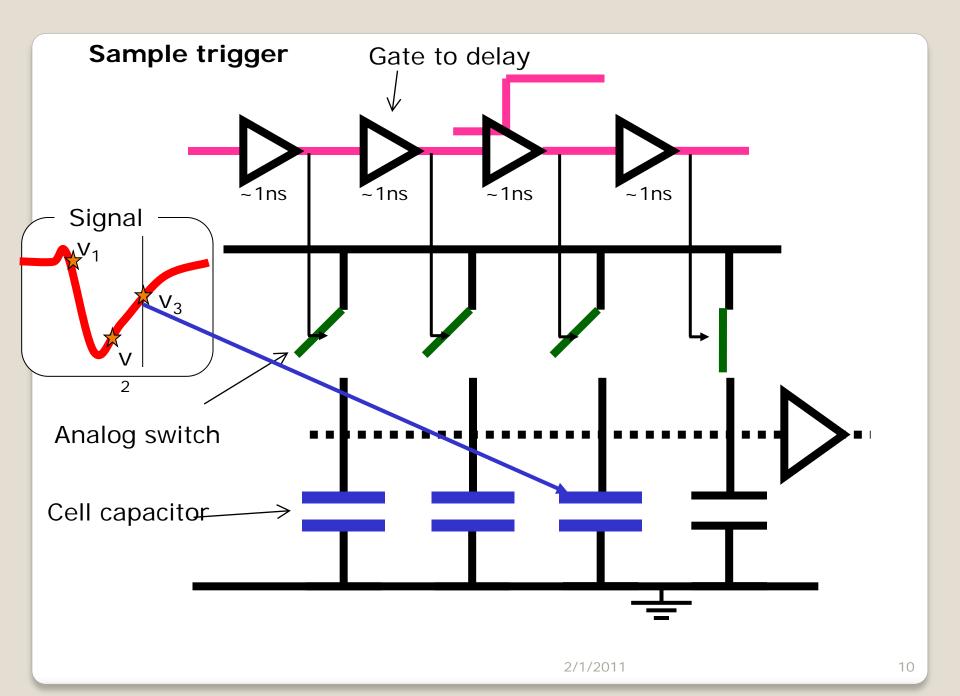

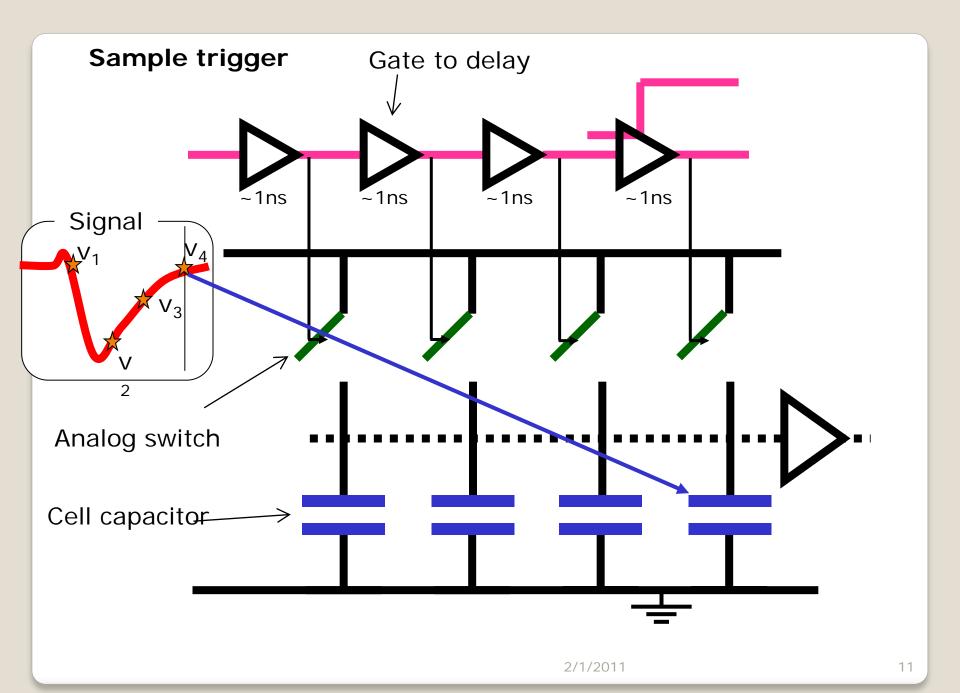

### AMC動作原理

2/1/2011

2/1/2011

۲

2/1/2011

|          | AMC<br>(+slow FADC) | FADC<br>(ADC081000 N.S.) |

|----------|---------------------|--------------------------|

| サンプリング頻度 | ~1GHz               | 1GHz                     |

| 動作電圧     | +5V                 | +1.9V                    |

| 消費電力     | 72mW(*)             | 1.45W                    |

| /チャンネル   | (+160mW FADC)       |                          |

| 分解能      | ≥10bit              | ~8bit                    |

(\*) readout clock=200kHz

### AMC vs. 1GHz FADC

2/1/2011 15

- TSMC0.5umプロセスを用いて開発

- サンプリング周波数~1GHzを確認

- 分解能11bit(≥10bit)を確認

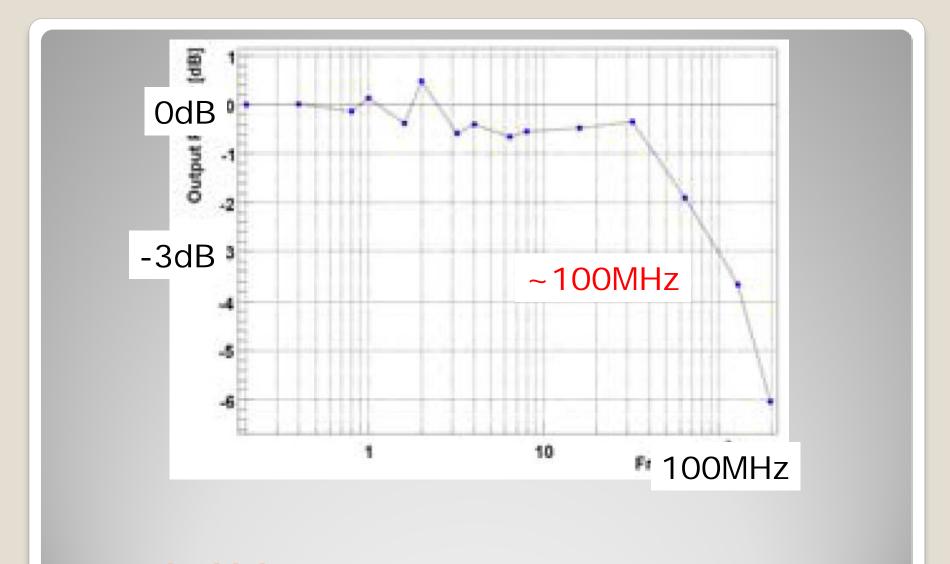

- 周波数帯域(<100MHz)を確認

### 去年までのAMC開発状況まとめ

- AMCのさらなる高性能化

- 1. アナログ帯域~GHzを目指す

- 2. さらなる低消費電力化

- 3. サンプルデータのデジタル化

- UMC0.25umプロセスでの開発

- ・ADCの内蔵化

### 今年度の開発目標

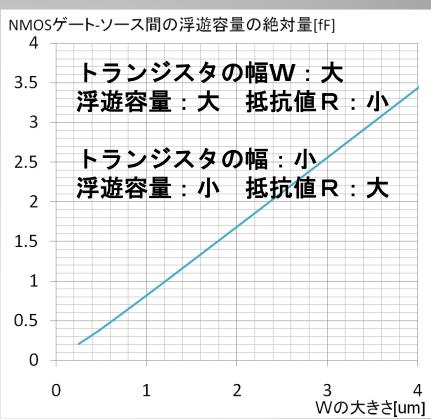

- 寄生容量、浮遊容量が小さくなる

- →動作の高速化、周波数帯域の改善、オフセットの改善 が期待される

- →さらにサンプル時にON状態のコンデンサーの数を少な くすることにより広帯域化を目指す

- 消費電力が1/4と軽減される(電源電圧5V→2.5V)

- →ただし、入力ダイナミックレンジが半分になる(分解能 に影響)

- →現在のノイズはkT/C制限より大きい

- →ノイズをTSMCO.5umより小さくできれば、分解能を 確保

- 遠山、吉越(ICRR)、田中(KEK)で開発

### UMC0.25umを用いる目的

(遠山、吉越、田中)

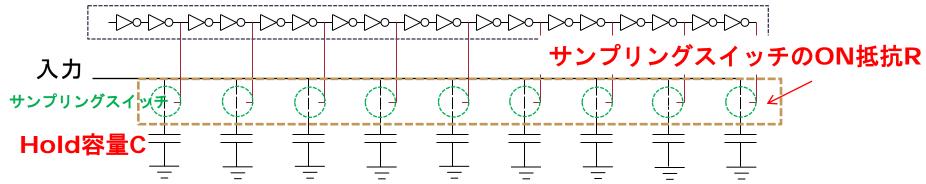

#### **Delay Line**

#### スイッチがONになっている数N

| 性能        | 要因            | 依存する設計パラメータ        |

|-----------|---------------|--------------------|

| サンプルスピード  | Delay素子の遅延量   | Delay素子のトランジスタサイズ等 |

| 周波数帯域     |               | C, R, N            |

| オフセットの大きさ | トランジスタの浮遊容量   | C, R               |

| 精度        | スイッチがON時の過渡現象 | C, R, N            |

|           | 熱雑音           | С                  |

### 設計パラメータ

(遠山、吉越、田中)

#### 設計アナログ帯域: 500MHz

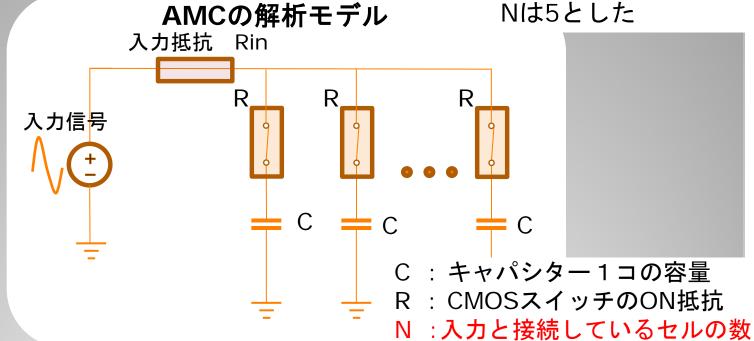

$R_{in}$ =100 $\Omega$ として設計 Nは5とした

$$f = \frac{1}{2\pi (RC + NR_{in}C)}$$

CとRは小さいほうが良い

R<sub>in</sub>: AMCの入力抵抗

## 周波数带域

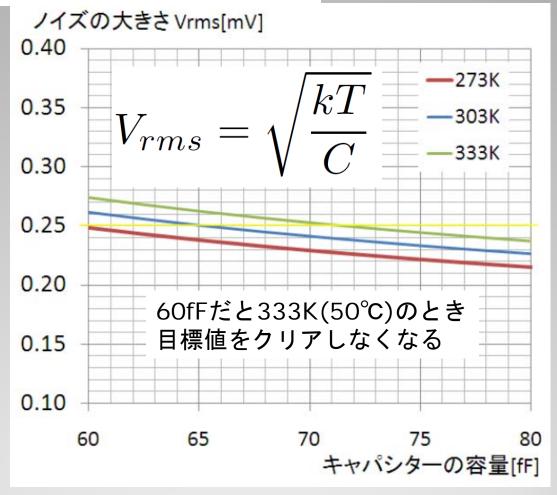

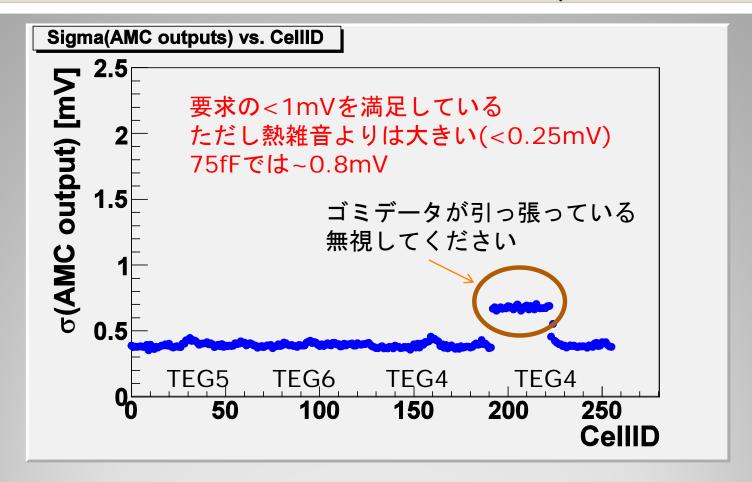

ノイズの大きさVrms: 0.25mV

(遠山、吉越、田中)

※1Vのレンジで12bit(1/4000)を目標にした

## 熟雜音

設計値:電圧値の乱れを0.25mV以下

過度応答特性

(遠山、吉越、田中)

設計:浮遊容量の大きさを Hold容量の1/400にする

### オフセット

(遠山、吉越、田中)

- 1. 入力周波数带域

- 2. 熱雜音

- 3. 過度応答特性

- 4. オフセット

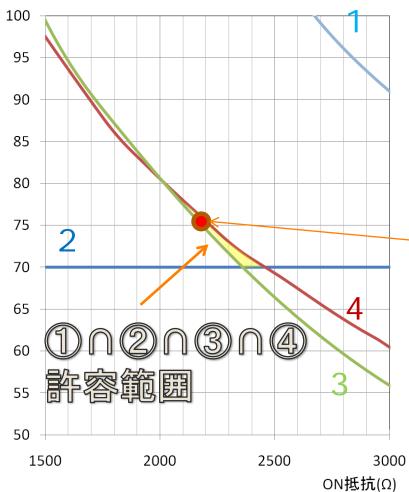

R=2200Ωを

C=75fFで設計

### パラメータの最適化

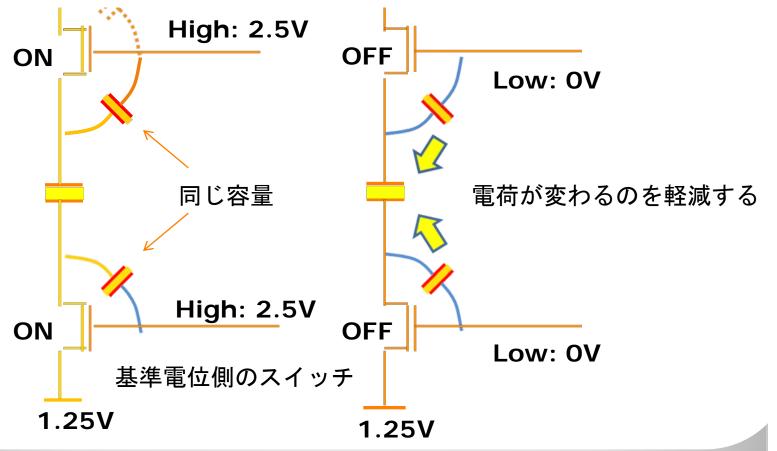

#### 浮遊容量による影響をキャンセルさせるために同じサイズのスイッチを設置

## オフセット対策その2

1. 25V

SETVREF 基準電位に固定

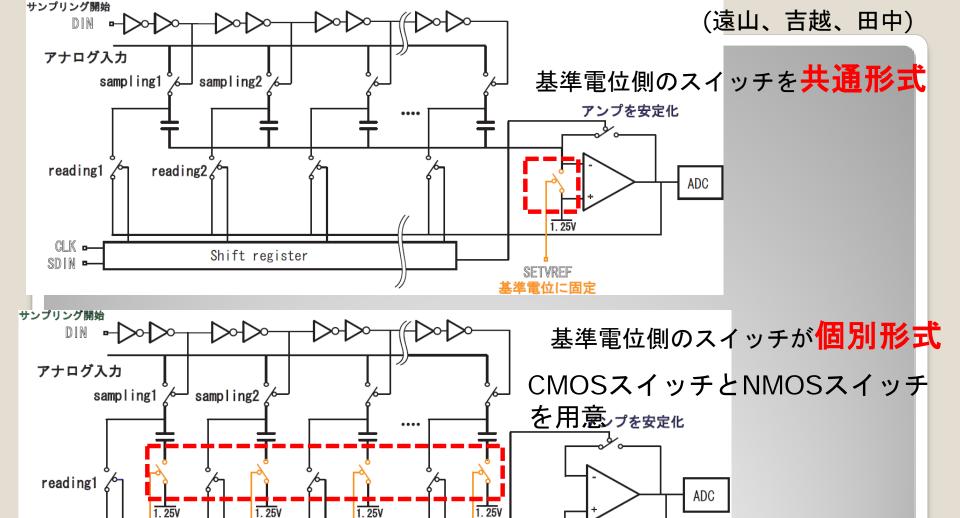

### スイッチの構造の違うTEG

Shift register

CLK

SDIN

# 試作品(Test Group Element)

|        | Hold容量 | 読出し<br>スイッチ | 基準位側の<br>スイッチ構成     | cell数 |

|--------|--------|-------------|---------------------|-------|

| TEG1-1 |        |             | 共通                  |       |

| TEG1-2 | 75fF   | CMOS        | 大坦                  | 128   |

| TEG2   |        |             | 個別                  | 120   |

| TEG3   |        | NMOS        | 101/71              |       |

| TEG4-1 |        | 400fF CMOS  | 共通                  |       |

| TEG4-2 | 400fE  |             | MOS                 | 64    |

| TEG5   | 40017  |             | 個別                  | 04    |

| TEG6   |        | NMOS        | <b>川의 <i>刀</i>リ</b> |       |

※前回のAMCとの比較のために400fFの場合も用意

(遠山、吉越、田中、阿部)

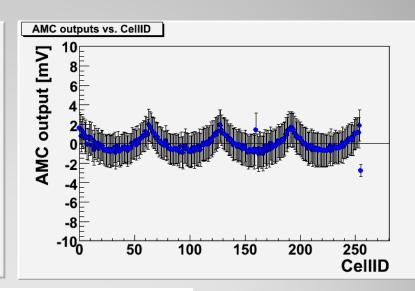

| 評価項目             | TEG4 | TEG5 | TEG6 |

|------------------|------|------|------|

| サンプリング信号幅 > 1us  |      |      |      |

| コモンモードシフト(σ<2mV) | 0    | 0    | 0    |

| ペデスタル(σ<2mV)     | 0    | 0    | 0    |

| 固有ノイズ(σ<1mV)     | 0    | 0    | 0    |

| DC入力レンジ(~1.5V)   | 0    | 0    | 0    |

| AC特性(ゲインのバラつき)   | Δ    | Δ    | Δ    |

| サンプリング信号幅~10ns   |      |      |      |

| コモンモードシフト(σ<2mV) | 0    | 0    | 0    |

| ペデスタル(σ<2mV)     | Δ    | Δ    | 0    |

| 固有ノイズ(σ<1mV)     | 0    | 0    | 0    |

| DC入力レンジ(~1.5V)   | 0    | 0    | 0    |

| AC特性(ゲインのバラつき)   | 0    | 0    | 0    |

|                  |      |      |      |

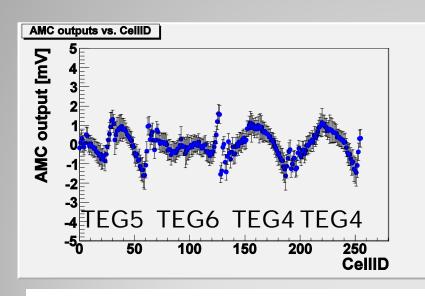

# 評価結果

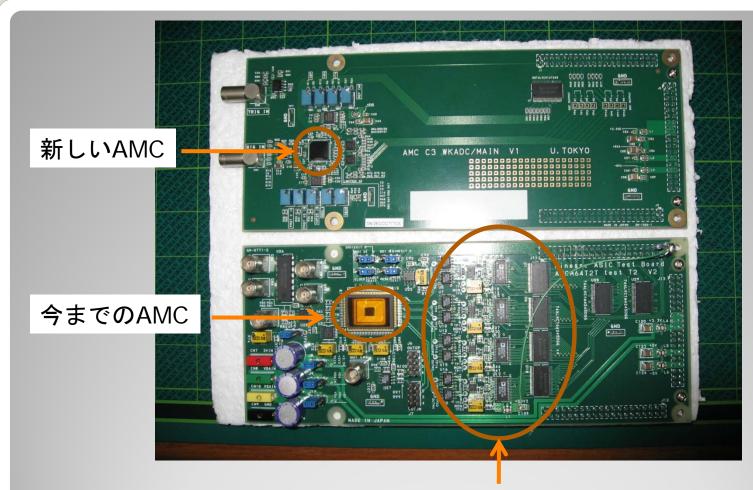

#### New

### 今までのAMC

TEG6(個別NMOSスイッチ)のばらつきが一番小さい

400ffペデスタル分布(DC入力1.85V) 10ns

読み出しスイッチとOpAmp間の浮遊容量~200fF+OpAmpのノイズ~0.25mV

## 400fF固有ノイズ(DC入力1.25V)

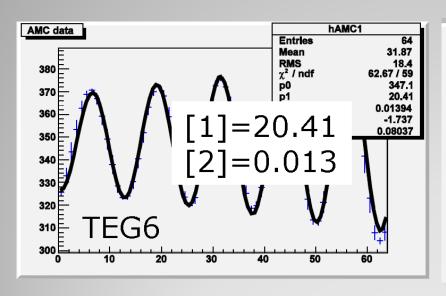

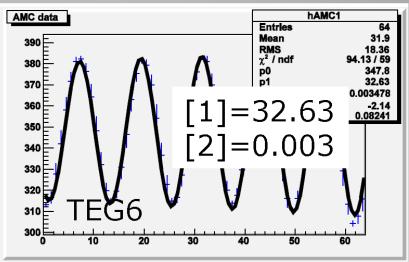

### 今までのサンプリング

### N=10のサンプリング

100MHz 500mVppを入力 N=10は、1.5倍の出力、ゲインの変化は半分以下

### AC出力

(遠山、吉越、田中、阿部)

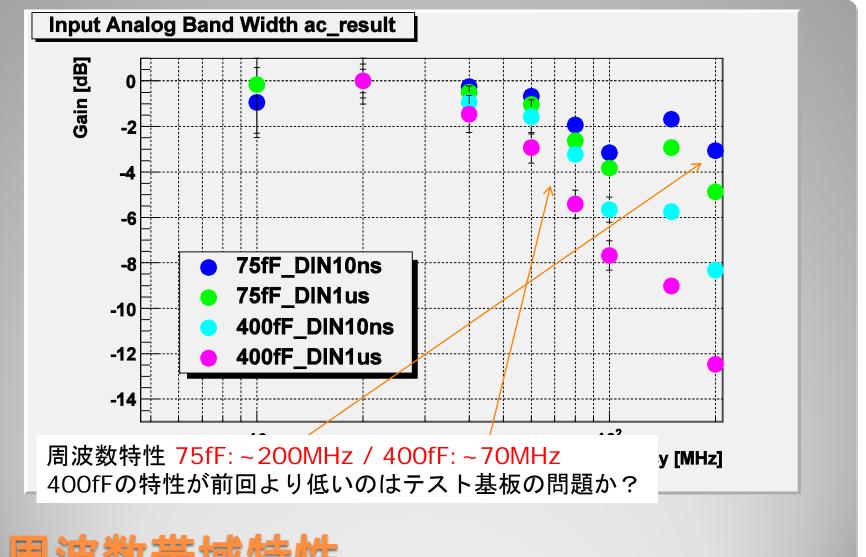

## 周波数帯域特性

| 項目        | 值/      |

|-----------|---------|

| チャンネル数    | 1       |

| 分解能       | 12bit   |

| ダイナミックレンジ | 2Vp-p   |

| サンプル速度    | 100kSPS |

| 消費電力      | <10mW   |

- AMCの特徴

- 1. 高速波形記録

- 2. 高分解能

- 3. 低消費電力

- 4. 比較的ゆっくりした 読み出し時間

- →サンプル速度より高分

KEK ASICトレーニングコースを利用 解TSMC 0.5umプロセス 雷

解能を重視した低消費 電力タイプ

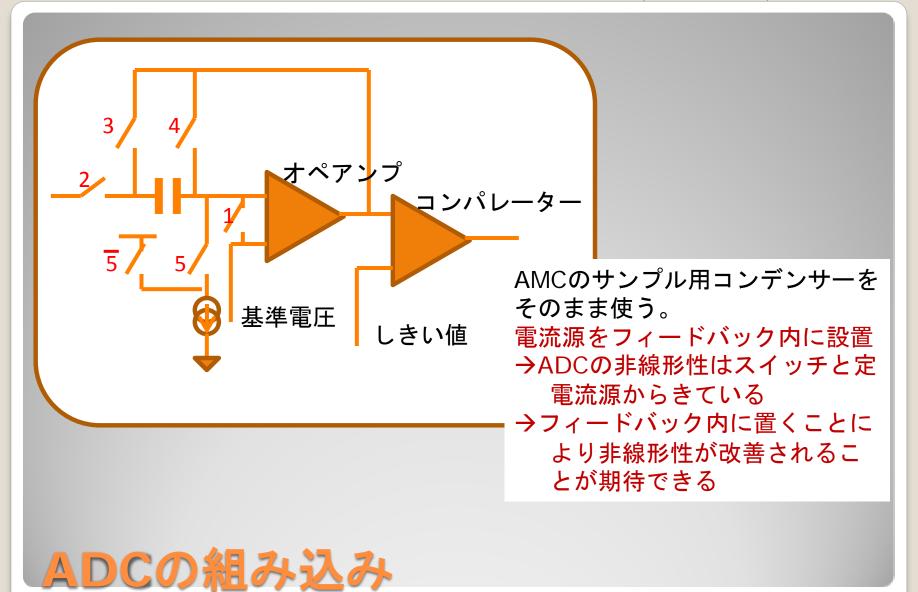

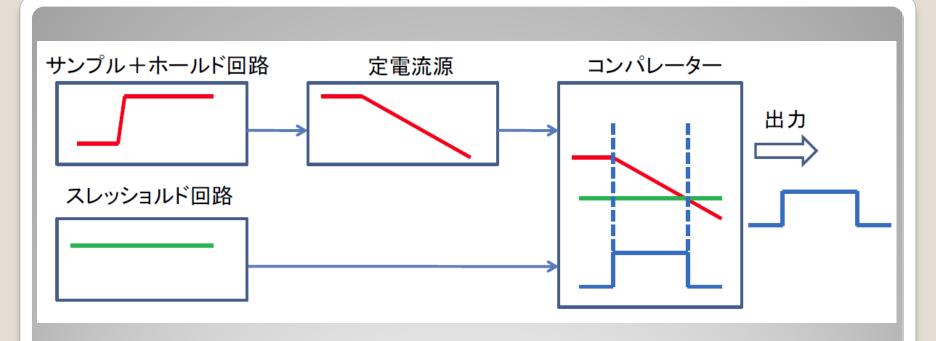

→Wilkinson type ADC

### ADCの仕様要求

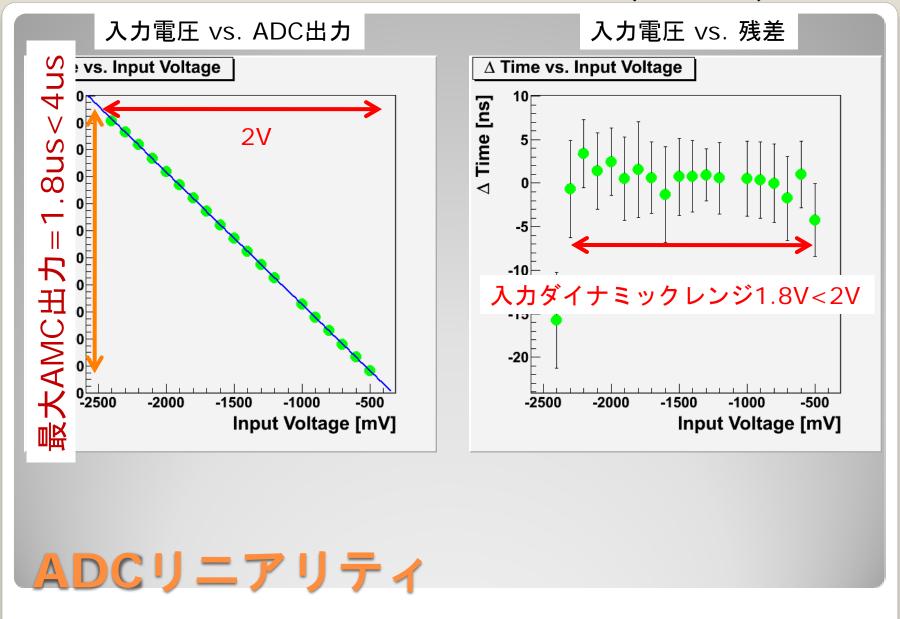

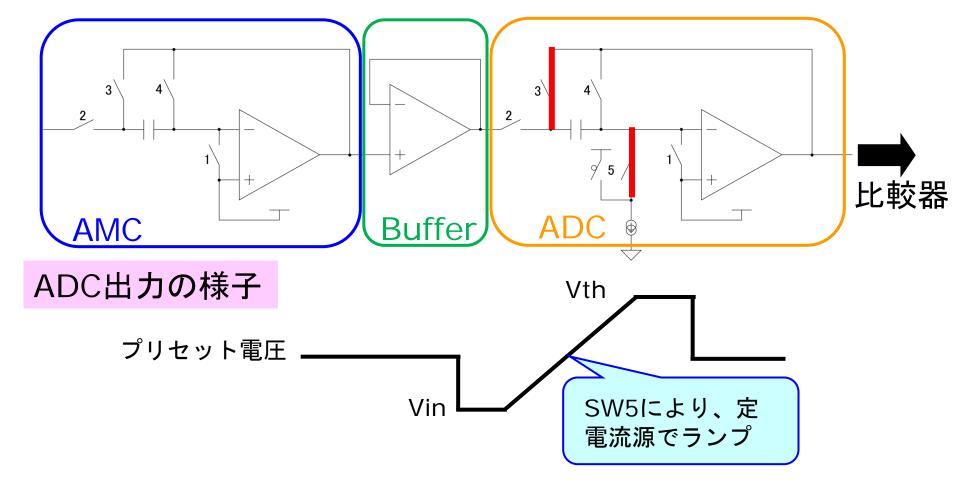

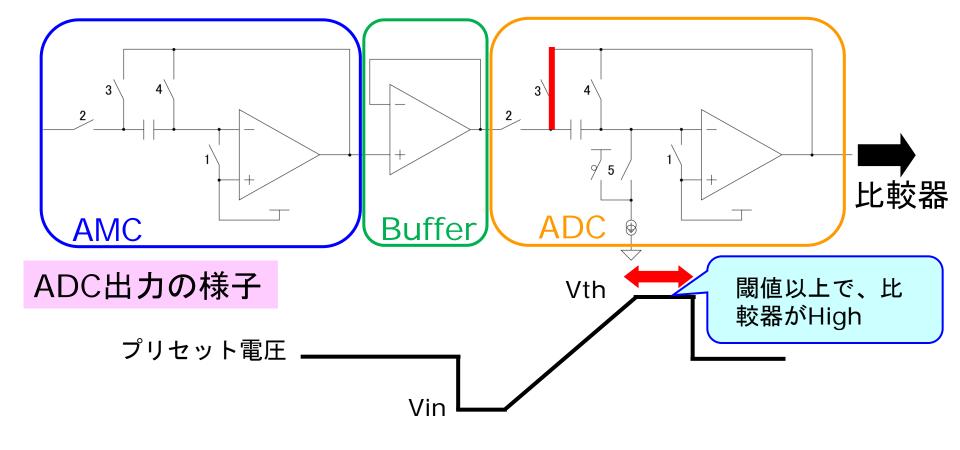

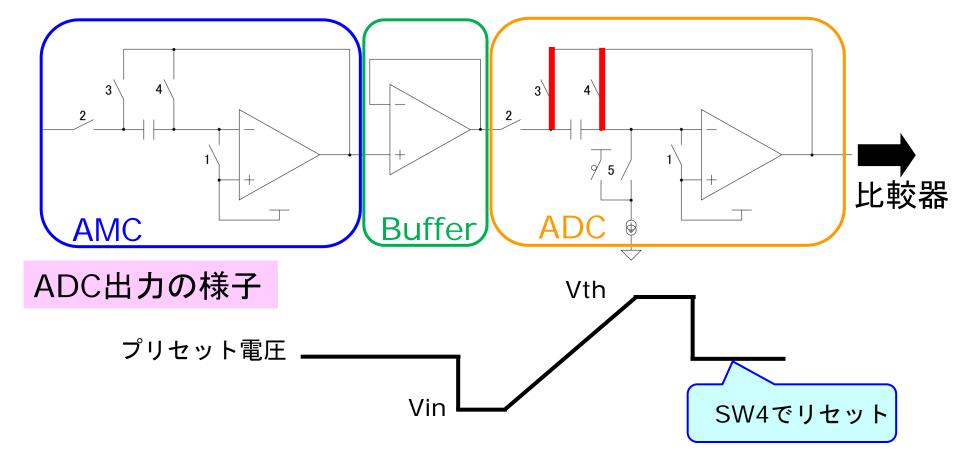

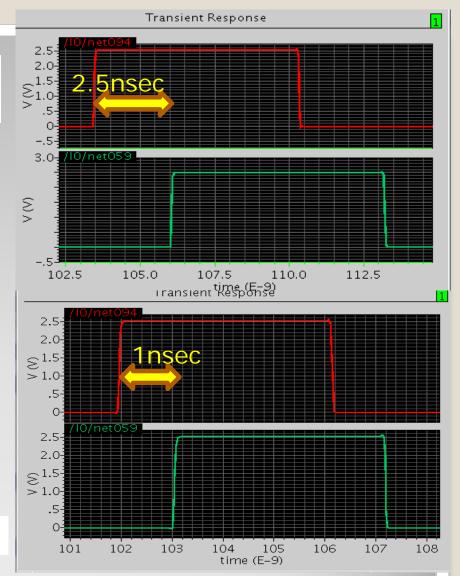

電圧を時間に変換→TDCでデジタル化 今回は、デジタル信号処理用FPGAにTDC(1ns)を搭載 12bit/1ns=4096/1ns~4us

### 電圧時間変換回路

ADCに関連する部品が要らなくなった

ADC付AMCと今までのAMC

(阿部、田中)

(阿部、田中)

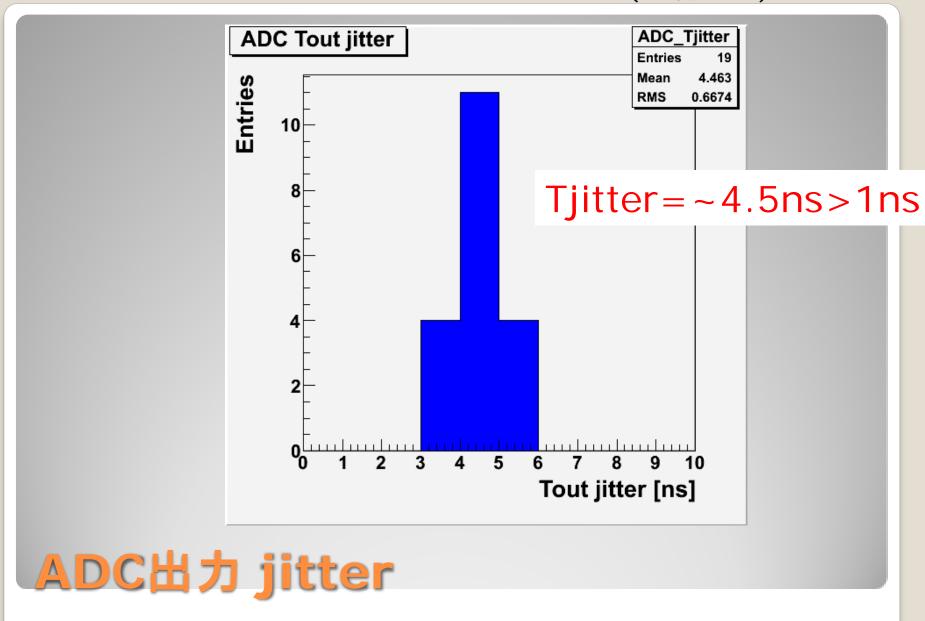

- ADCの動作を確認した

- ただし、ADCの分解能は8bitで、目標としていた12bitは得られなかった。

- →藤森くんが改良版を作成

#### Wilkinson型ADC一回目まとめ

- AMC

- 400fF × 256cell

- 8 output

- ADC

- Wilkinson型

- 。(目標)12bit

- 250 kSPS (4usで読み出し)

- 時間幅で出力し、後段FPGAのTDCで読み出し ⇒4us / 2^12 = 1nsの精度が必要 前回 今回

- ・動作が不安定

- 0.50umプロセス

- ・確実に動作するものを作る!!

- 0.25umプロセス

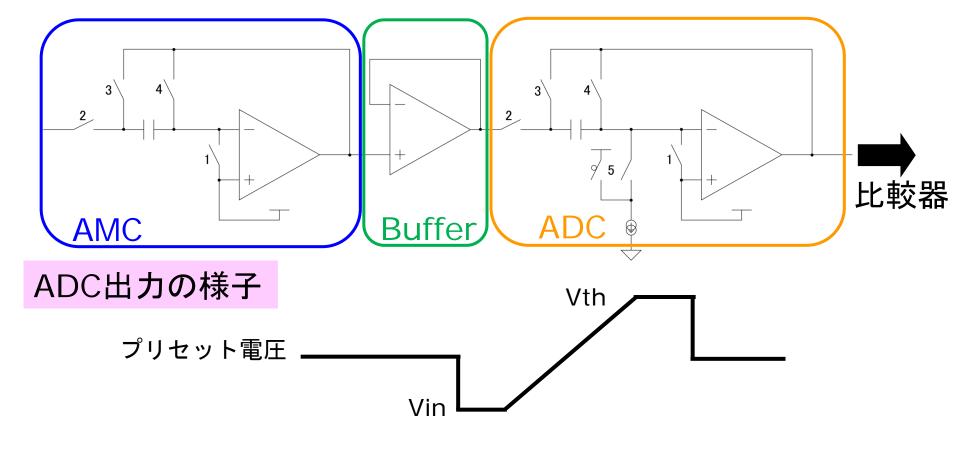

#### 改良型ADC概要

- 定電流源でランプ。比較器出力の時間幅がVinで決まる。

- 定電流源でランプ。比較器出力の時間幅がVinで決まる。

- 定電流源でランプ。比較器出力の時間幅がVinで決まる。

- 定電流源でランプ。比較器出力の時間幅がVinで決まる。

- 定電流源でランプ。比較器出力の時間幅がVinで決まる。

- 定電流源でランプ。比較器出力の時間幅がVinで決まる。

- > 0.25um プロセス

- ⇒ 速いスイッチで漏れ電荷を防ぐ

- ⇒ 低消費電力

- ▶ 高ゲインAMP (後述)

- ⇒ リニアリティの向上

- >スイッチ論理変更 (次ページ)

- ✓定電流源引込み元からの、電荷の流れ込み

- ✓リセット方法の変更

- ⇒ 波形の改善

#### 改良点

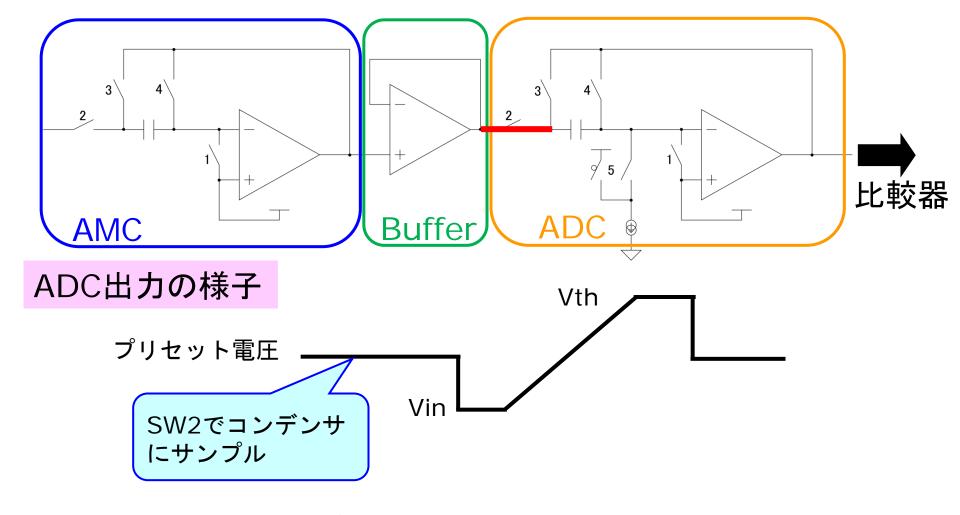

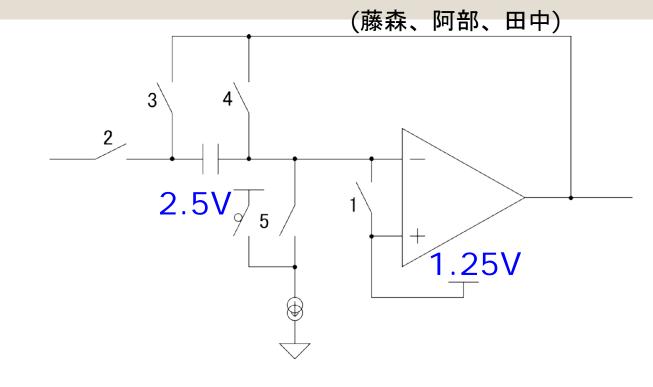

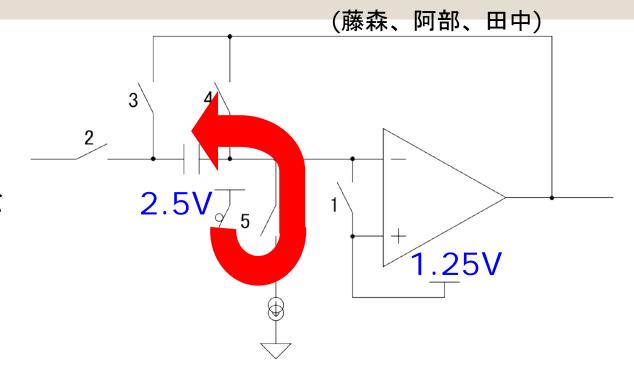

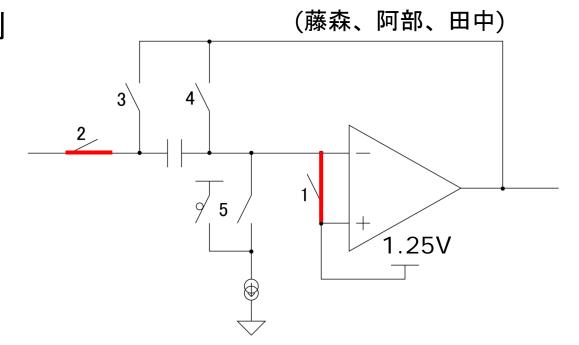

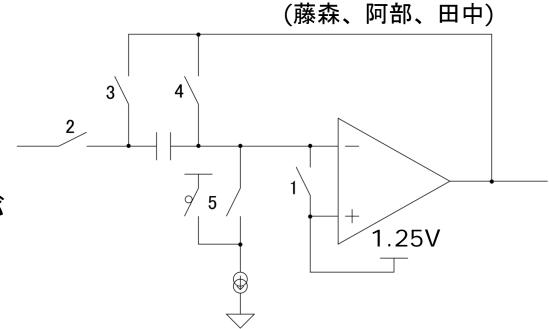

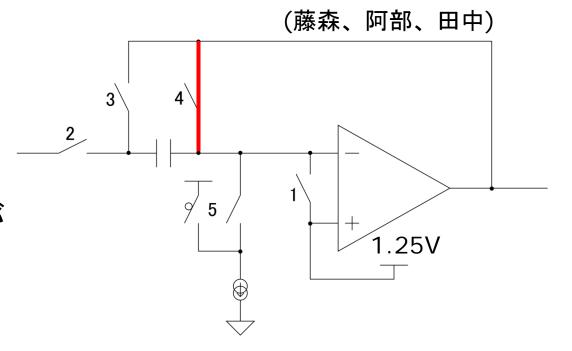

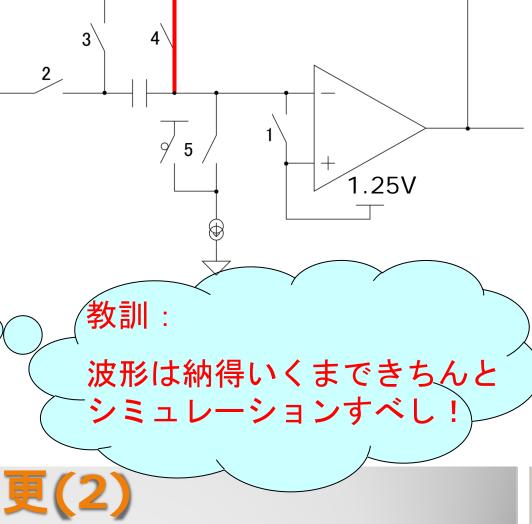

## スイッチ論理変更(1) -定電流源引込み元からの、電荷の流れ込み

- ・ 定電流源の引き 込み元が間違い

- SW5を入れた時 に逆流し、Vinが 保持できない。

#### スイッチ論理変更(1)

- 定電流源引込み元からの、電荷の流れ込み

- ・ 定電流源の引き 込み元が間違い

- SW5を入れた時 に逆流し、Vinが 保持できない。

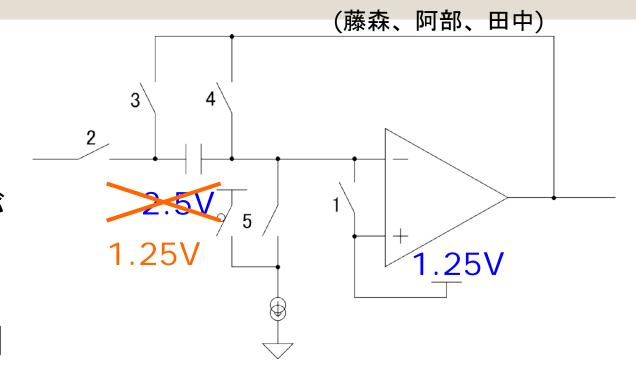

AMP +端子と同じ電圧から引く と解決

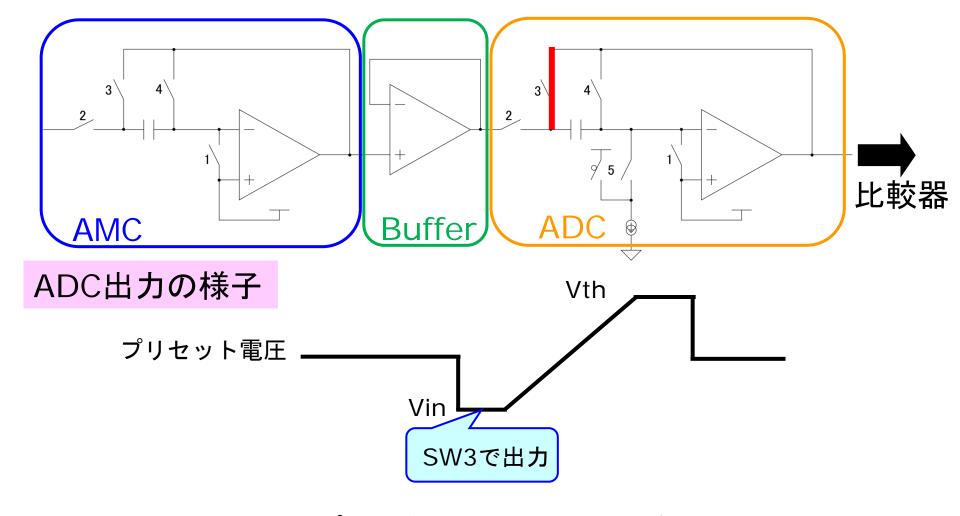

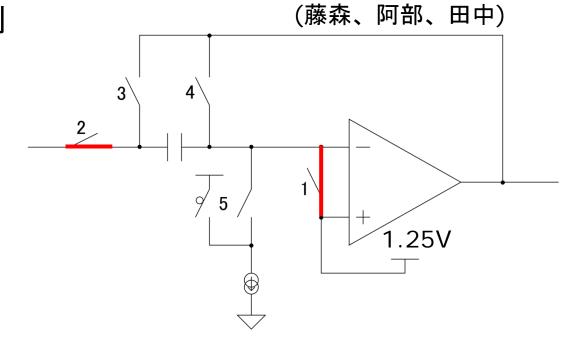

#### スイッチ論理変更(1)

-定電流源引込み元からの、電荷の流れ込み

●SW4を入れなければ、 AMP出力不定

- ●SW4を入れなければ、 AMP出力不定

- ●SW1 off後AMP負入力が 1.25Vからずれる。

- ●SW4を入れなければ、 AMP出力不定

- ●SW1 off後AMP負入力が 1.25Vからずれる。

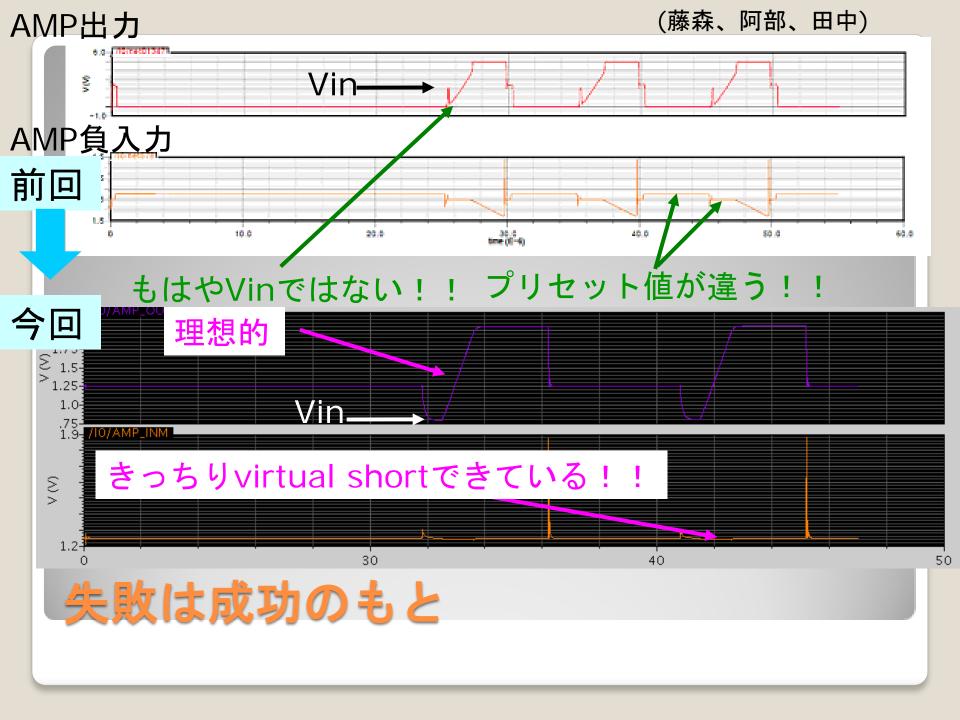

⇒ADC非動作時・サンプル時ともにSW4で入出力を固定したら、波形が非常に綺麗になった。

- ●SW4を入れなければ、 AMP出力不定

- ●SW1 off後AMP負入力が 1.25Vからずれる。

⇒ADC非動作時・サンプ ル時ともにSW4で入出力 を固定したら、波形が非 常に綺麗になった。

(藤森、阿部、田中)

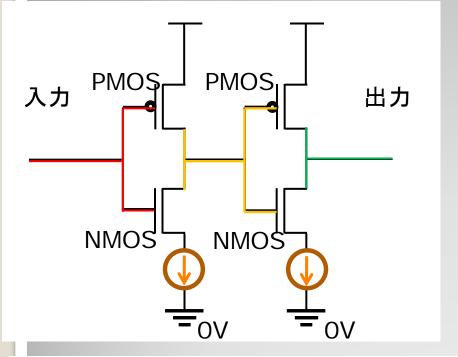

▶高ゲインAMP ⇒ リニアリティの改善

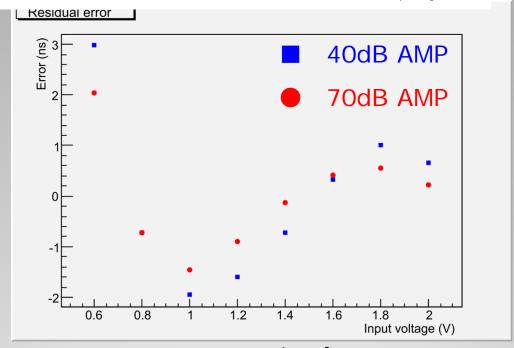

- Resolution: 11~12bit 程度

- Dynamic range: 0.7-2.0 V⇒期待通りの性能が見込まれる。

#### 高ゲインとシミュレーション結果

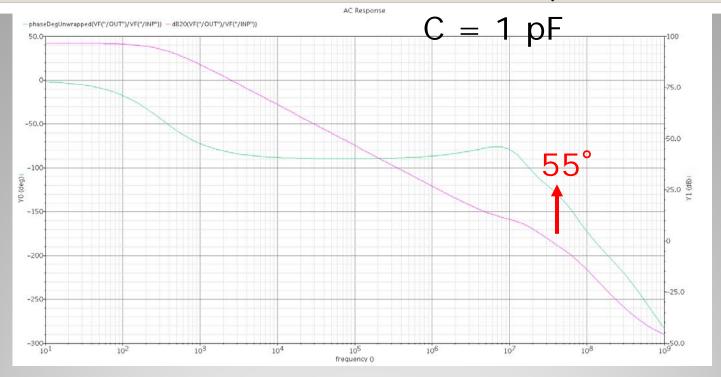

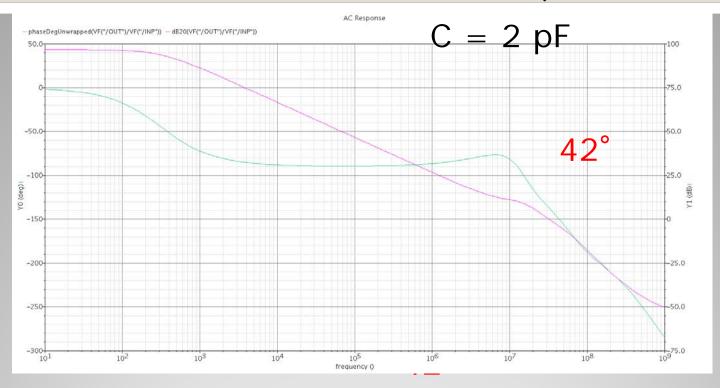

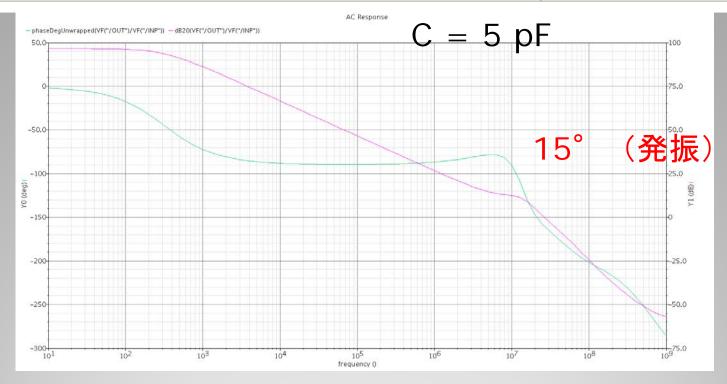

- Phase Margin := phase @ gain = 0 dB

- 高ゲインAMPで、高負荷の時は要注意。

#### 安定性

- Phase Margin := phase @ gain = 0 dB

- 高ゲインAMPで、高負荷の時は要注意。

#### 安定性

- Phase Margin := phase @ gain = 0 dB

- 高ゲインAMPで、高負荷の時は要注意。

- 400fF < 2pF limitより安定を確認。</li>

#### 安定性

- 前回のバージョンの問題点を逐一見つけて丁寧に解決した。

- 乞うご期待!

#### 改良版Wilkinson型ADCまとめ

- ・既知の問題の解決

- 。ノイズが熱雑音より大きい→浮遊容量+Amp雑音?

- ○周波数特性の広帯域化→新しい回路構造

- ・サンプリング時間の安定化→PLLの取り込み

- トリガーレス読み出しへの取り組み

- Wilkinson型より高速(~30MHz)のADCを組み込む

#### 今後の展開

ADCをASIC内に内蔵することにより高速化が可能

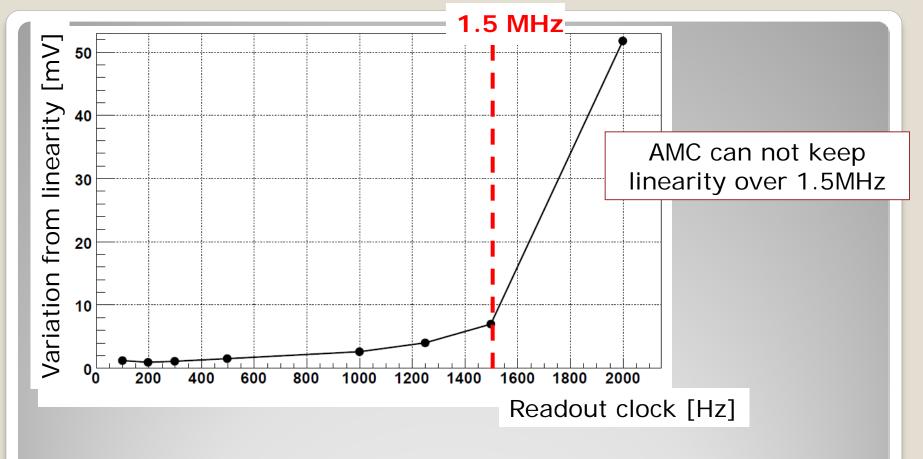

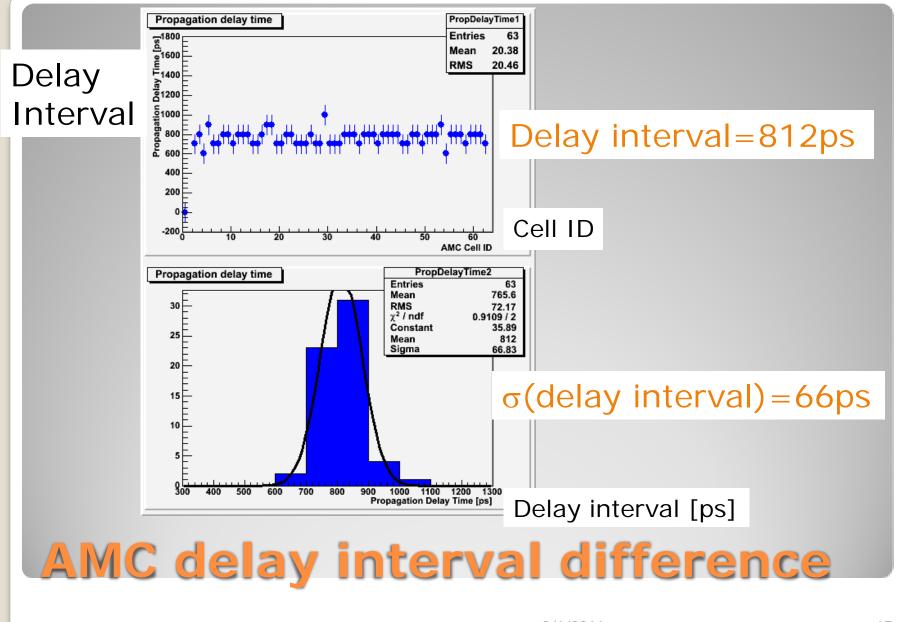

AMCの読み出し速度とリニアリティ

- AMCは、高速波形サンプル+高分解能を目指したICです。

- プロセスを0.5um→0.25umに変更して、性能 が向上した。

- ADCを組み込み、最初の動作確認を行った。改良版の設計はもう済んでいる。

- 今後は、さらなる高性能化、トリガーレス読み 出しへの取り組みを行う。

#### まとめ

バックアップスライド

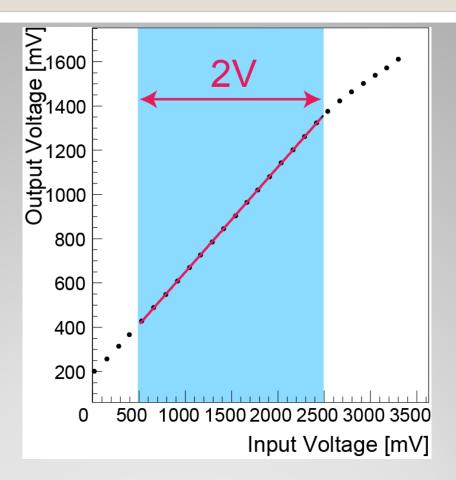

Input range: 2V (preamp= $2V_{p-p}$ )

#### **AMC DC Linearity**

2/1/2011 65

Resolution: 11bit(=2V/0.7mV)

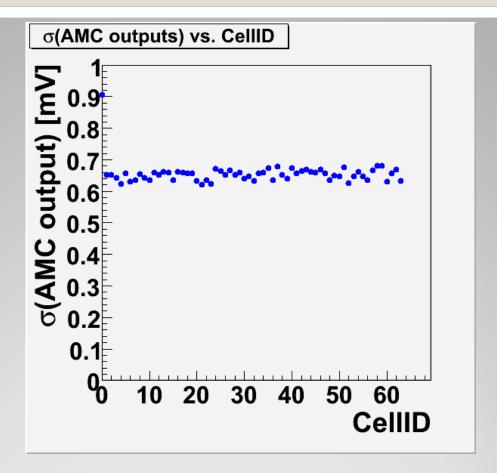

**AMC** noise

2/1/2011 66

2/1/2011 67

### 周波数特性

#### (遠山、吉越、田中)

- •スイッチングスピード: 400MHz~1GHz

- •スイッチがONになっている数Nの制御

電流源で電圧変化を制御パルス幅の維持

#### Delay Lineの設計

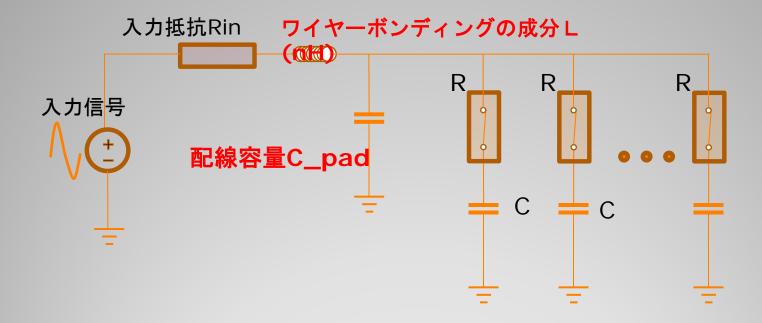

#### 周波数特性のシミュレーションモデル

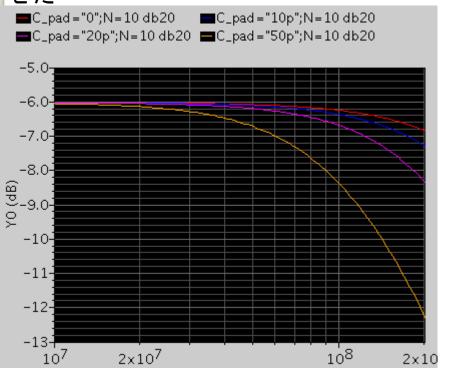

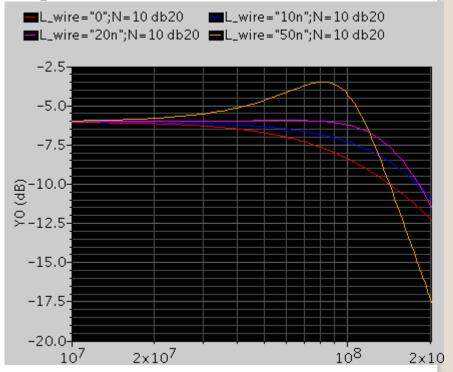

パッド容量とワイヤーボンディングによるインダクタンス成分 を追加して再モデル化した

#### TEG6 N=10 におけるシミュレーション

結果

インダクタンスは0 nHでパッドの浮遊容量を0pFから50pF まで変化させた

パッドの浮遊容量は50pF でインダ クタンスを0nH から50nH まで変化 させた

こぶの構造が見える

帯域が落ち、pad容量が50pF程度で-3db落ちのところが100MHz程度に かる

なる ※シミュレーションの都合上-6dBを基準(0dB)と

71

している

(阿部、田中)