# DRS4チップを用いた QDC開発上での困難

大阪大理, KEK, RCNP, 京大理, 東大理, ソウル大, Open-It

本多良太郎, 五十嵐洋一, 高橋智則, 新山雅之, 冨田夏希, 水谷圭吾, 中井恒, 谷田聖, 池野正弘, 内田智久

# 目次

- 開発動機

- DRS4

- 開発した基板

- FPGAファームウェア

- 困難と得られた教訓

- まとめ

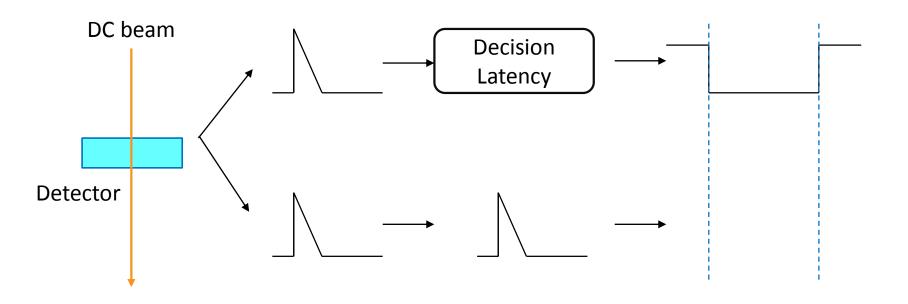

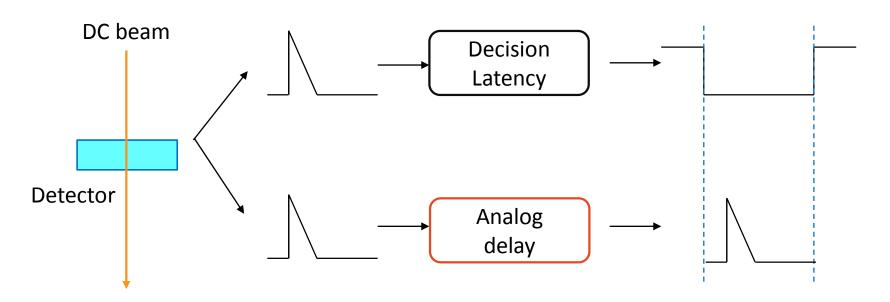

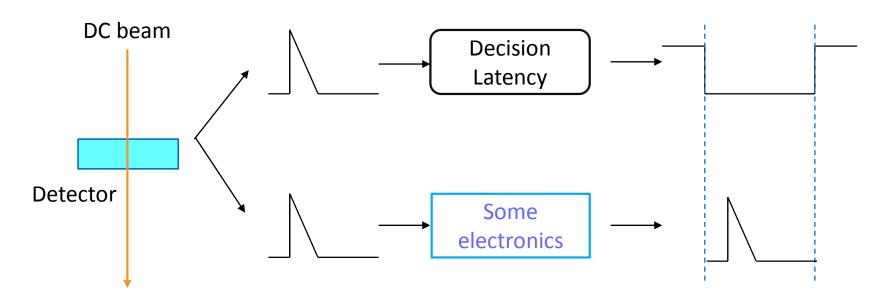

# 非同期トリガーでQDCを使用する際の問題点

## 非同期トリガーでQDCを使用する際の問題点

長い同軸ケーブルは高価 チャンネル数を増やすのが困難

## 非同期トリガーでQDCを使用する際の問題点

読み出し回路で この問題を解決したい

# 開発動機

### 解決策 : 波形サンプリング

目標:汎用読み出し回路

波形の鋭い検出器、特にPMTに対応したい -> 1 GSPS

既製品と同程度の値段でありたい -> 20k JPY/ch程度

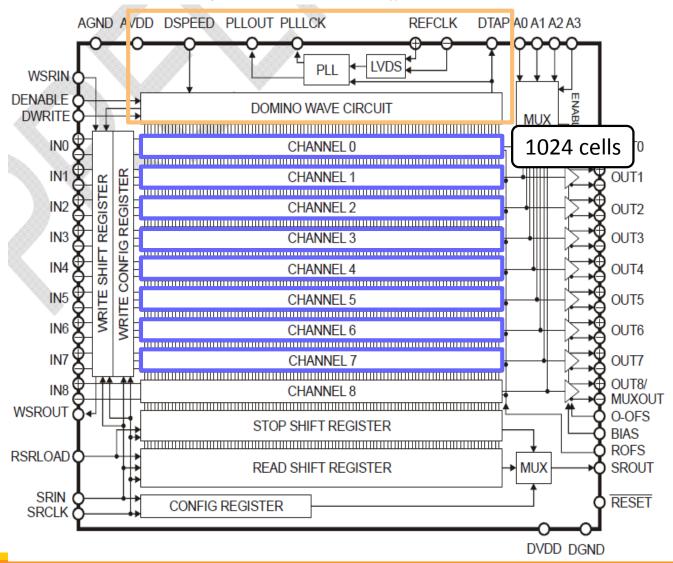

DRS4 (PSI開発) Switched Capacitor Array (SCA) Analog buffer

Sampling rate 0.7 ~ 5.0 GSPS

Input ch 8 (9) ch

Cells/ch 1024

Input range 1 Vp-p

Power

Consumption 110 mW (1 GSPS)

Cost  $1k \sim 2k JPY/ch$

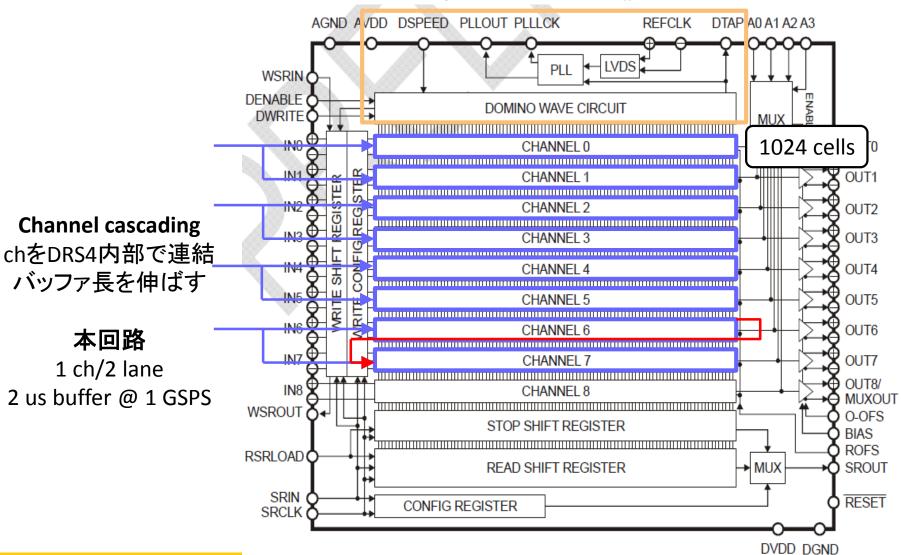

## DOMINO wave 高速サンプリング信号

### DOMINO wave 高速サンプリング信号

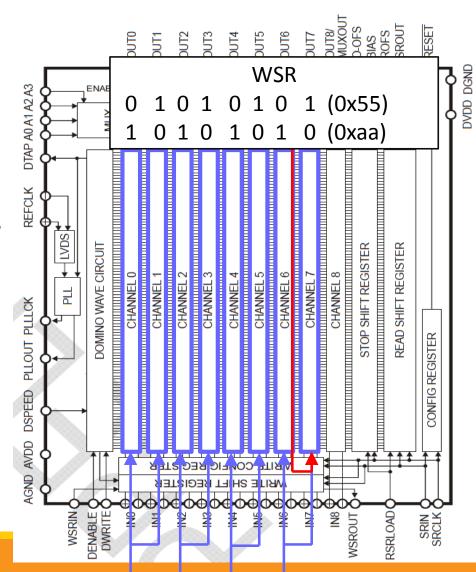

AGND AVDD DSPEED PLLOUT PLLICK REFCLK DTAP A0 A1 A2 A3 **LVDS** WSRIN DENABLE DOMINO WAVE CIRCUIT **DWRITE** 1024 cells IN<sub>0</sub> CHANNEL 0 OUT1 CHANNEL OUT2 IN3 OUT3 CHANNEL 3 OUT4 **ROI** \_\_\_\_\_\_ OUT5 WRITE OUT6 IN7 OUT7 wr ptr Ŭ OUT8/ IN8 CHANNEL 8 MUXOUT WSROUT A 0-OFS STOP SHIFT REGISTER **BIAS** ROFS RSRLOAD C rd ptr READ SHIFT REGISTER → MUX **SROUT** SRIN RESET CONFIG REGISTER SRCLK DVDD DGND

Region Of Interest (ROI)

最小限の読み出しで 必要な波形を得る

## DOMINO wave 高速サンプリング信号

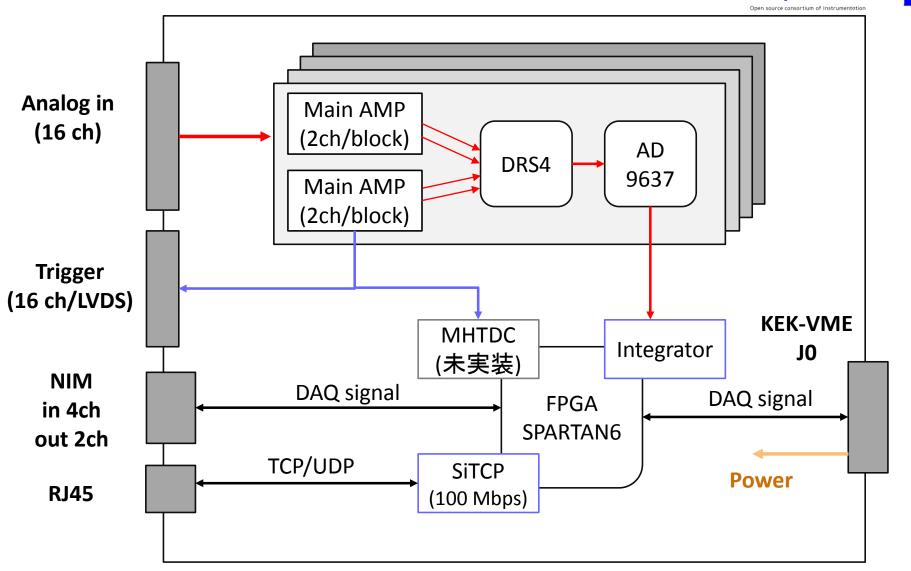

# 開発した基盤 -ブロック図-

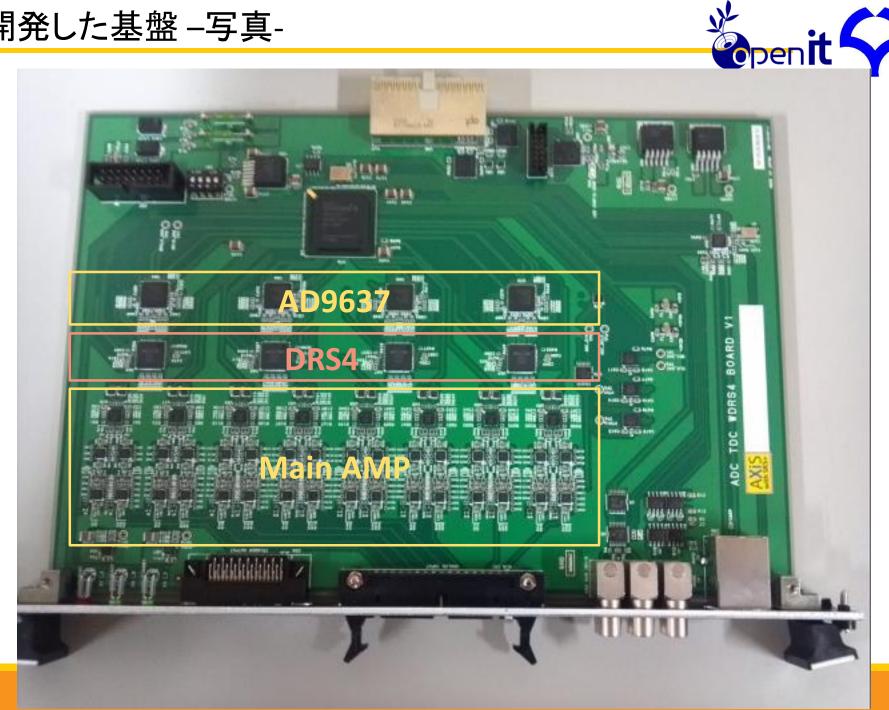

# 開発した基盤 -写真-

## 波形とQDC両方をサポート

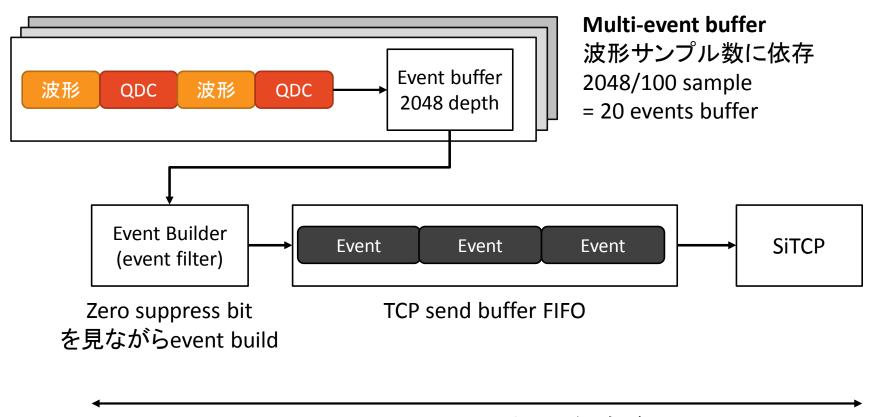

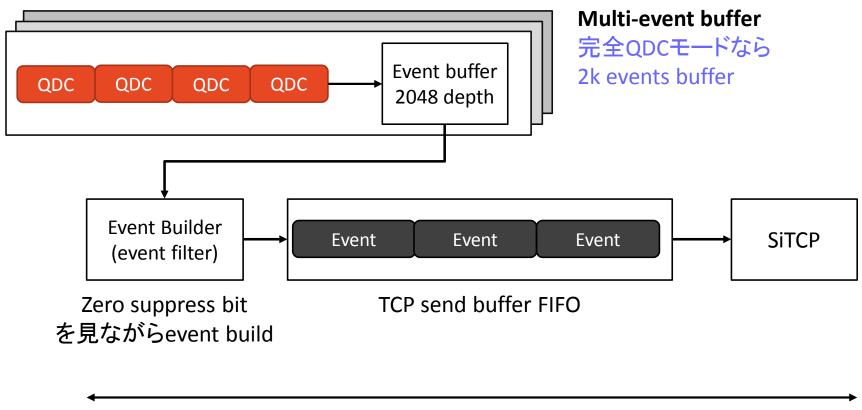

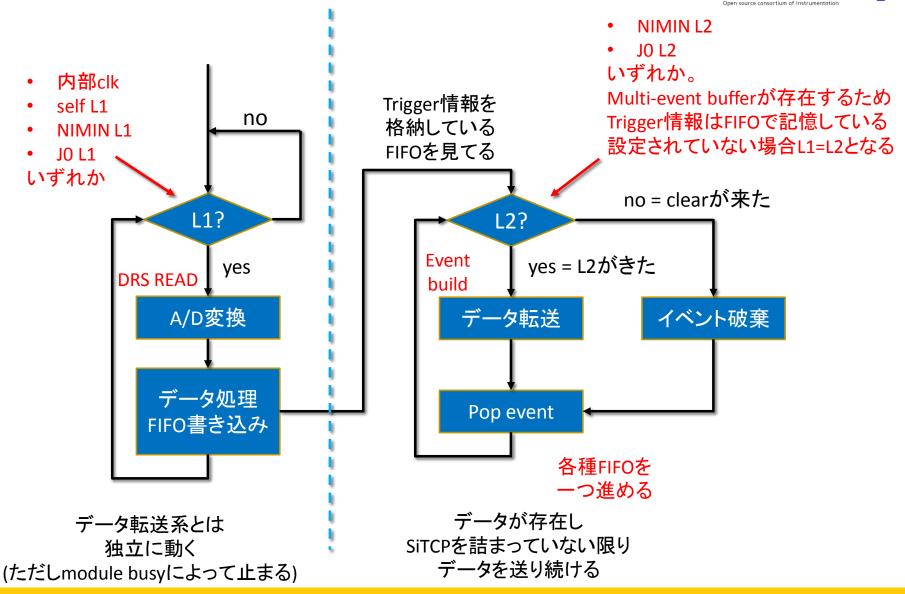

Event buffer - SiTCPまでの経路が 詰まらない限りA/D変換のDead timeのみ

< 10 us @ 100 samples

## 波形とQDC両方をサポート

Event buffer - SiTCPまでの経路が 詰まらない限りA/D変換のDead timeのみ

< 10 us @ 100 samples

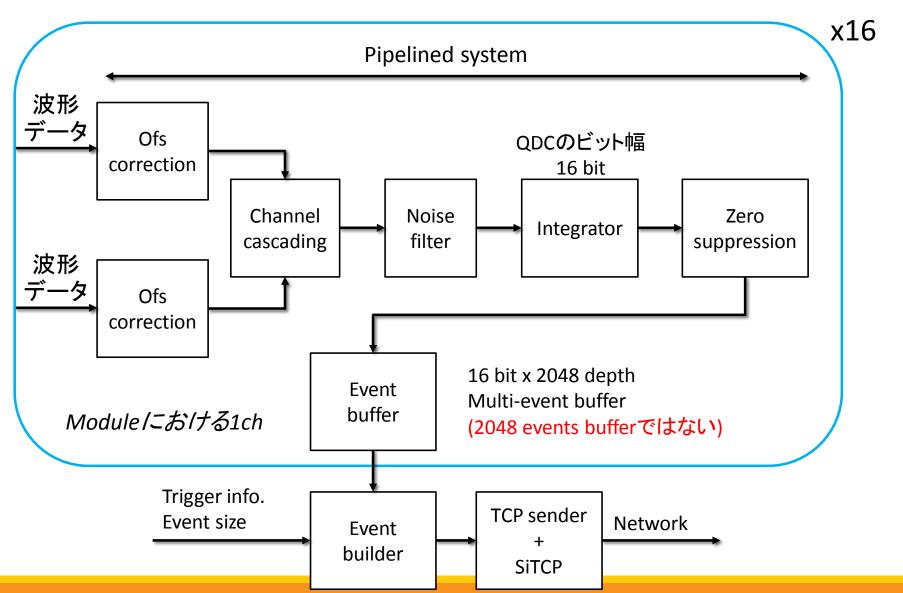

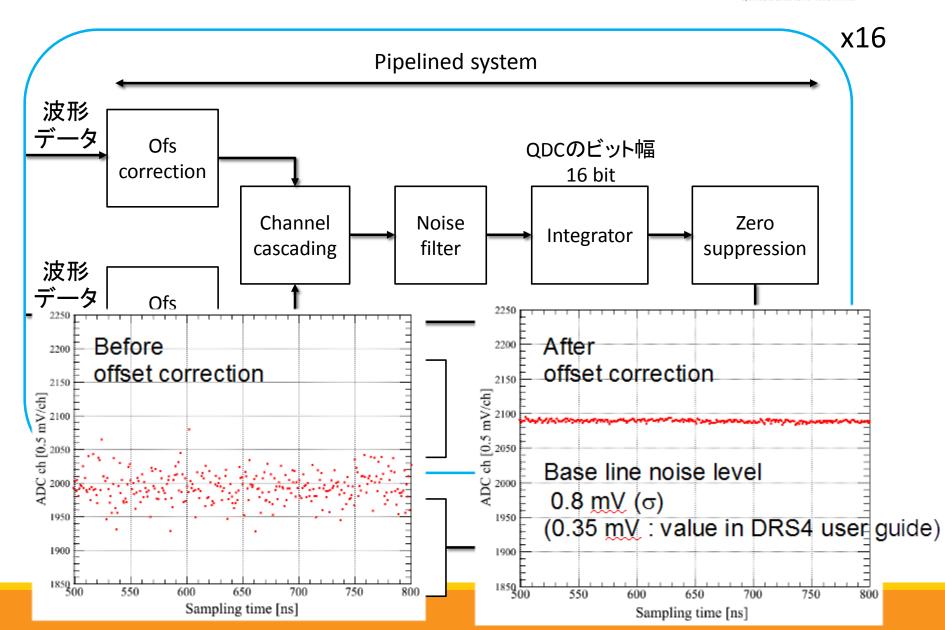

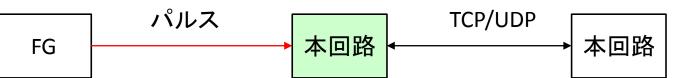

## FPGA firmware

# Specification

## **Analog**

Number of channel

16

Input range 2 Vp-p

Common mode input range 1 V

Absolute input range 2.5 V

Buffer range

2 μs @ 1 GSPS

## Digital I/O

Discriminator outputs (LVDS), 16 ch parallel

NIM level I/O (4 IN/2 OUT)

→ Trigger, BUSY etc...

Receive triggers from the KEK-VME J0 bus

#### **Data transfer & control**

TCP & UDP realized by SiTCP (100 Mbps)

#### **PCB** standard

- VME 6U KEK VME

- · Only J0 is mounted

- 3.3 V from J0

$$\rightarrow$$

+3.3 V ~ 6 A

# ユーザー

## **J-PARC**

- K1.8 beam line (常設)

- K1.1 beam line (常設)

- High-p beam line (E16)

### SP8

• LEPS2

# 性能

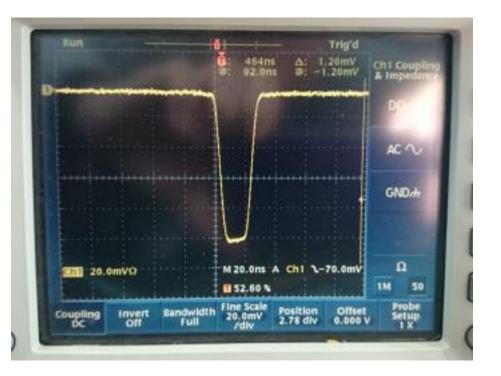

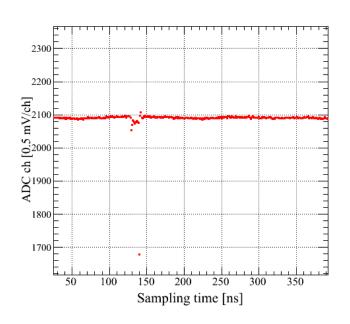

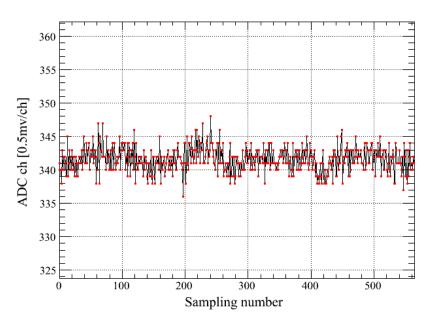

# FPからの波形

# 波形データ

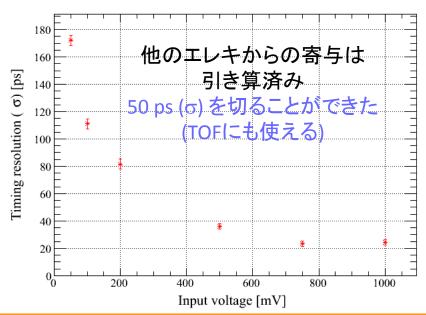

# Main AMP comparatorの時間分解能

# メインアンプの時間分解能

## 入力波形

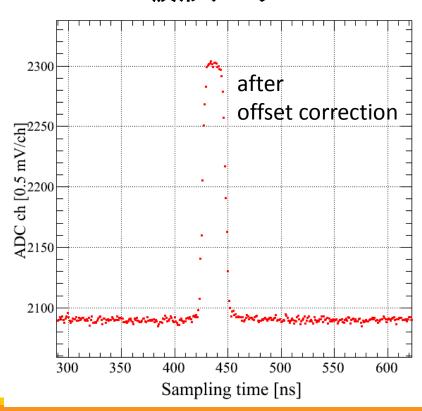

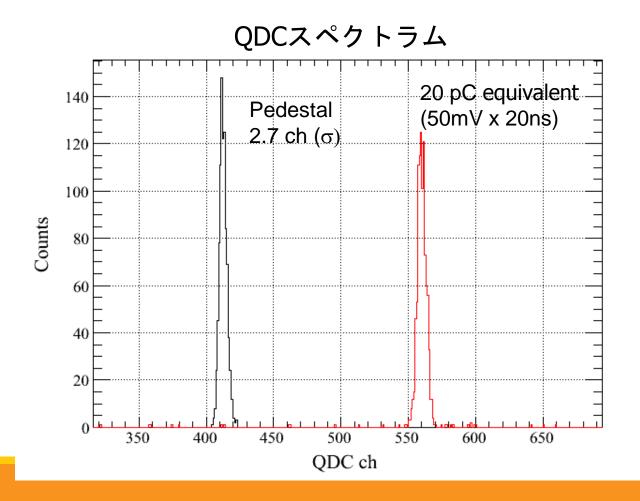

# QDCとしての性能

例として100サンプルの波形データを積分 下位4ビットは有効ビットでないため破棄 LSB精度: 0.135 pC/ch (CAEN v792; 0.1 pC/ch)

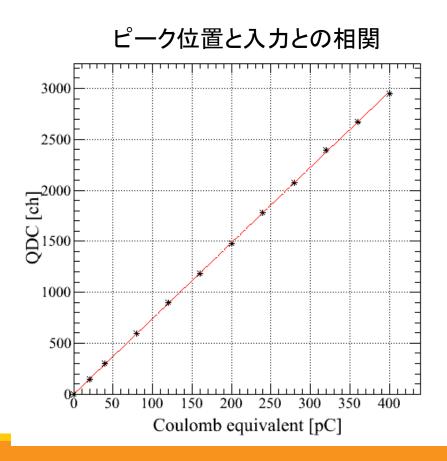

### FGからの入力波高を変えながら線形性の確認

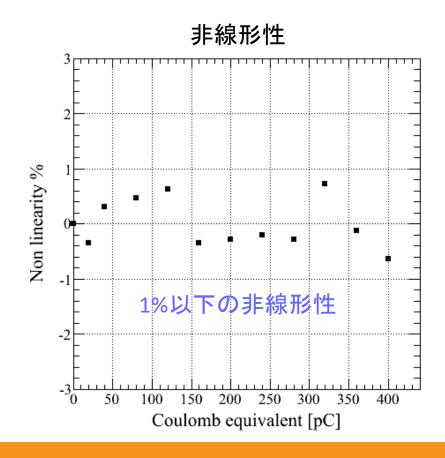

### 非線形性の定義

Non linearity = (QDC mean f(x))/(QDC mean) x 100

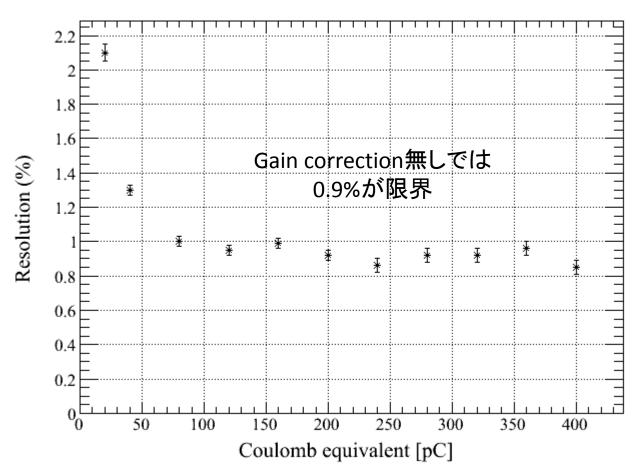

## QDC resolution (%)

*σ*/mean x 100

## QDC分解能の入力電圧依存

# 困難

# DRS4の駆動にかなり手間取った

### Reset入力で内部レジスタが初期化されない。

-> SPIで手でレジスタを設定して解決。(本来はされるはず、使い方が悪い?)

#### 波形が読み出せない。

(DRS4にResetを入れるときはSRINがHighでないと動かない?)

**いくつかのDC offsetをかけないといけなくて、中点電圧を正しくセットしないと動かない。** (しかも分かりにくかった…)

これらの解決で1ヶ月くらい使った

# DRS4のクセに更に悩まされた

# Open source consortium of Instrumentation

#### 波形がジャンプする、うねる

しかも傾向がDC offsetの値やFirmwareによって変わってしまう。

## Register出力が初期化時とDAQ時で1クロックずれてるような…

Write shift registerというレジスタを読まないといけないのだが 設定時にリードバックしたものと DAQ中に読み出したので 1クロック分シフトしてしまう... とりあえずそういう物だと思って使用中

# DRS4のクセに更に悩まされた

#### Write Shift Register (WSR):

どのレーンへ波形の保存を行っているか示す(設定する)レジスタ

WSRを見ていればActiveなレーンがわかるはずだが…そうなっていない。

加えてcell number (read ptrの先頭)の 値を見てどの辺りで波形取得がとまったか を調べないと正しくchannel cascadeできない。

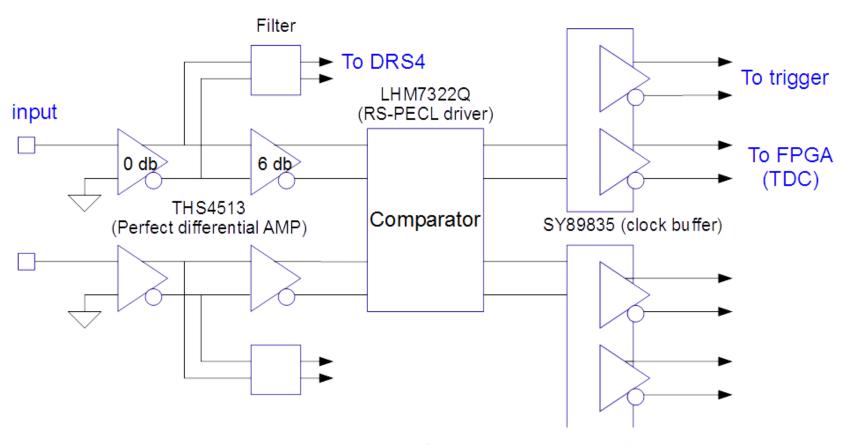

# Main AMPがすごい事になってしまった

## この部分だけで5000円/ch 消費電力も大きい ~400 mW/ch

一切のR&D無しで一年後に実践投入できる物を などという要求に応えたらこうなった (正直作り直したい)

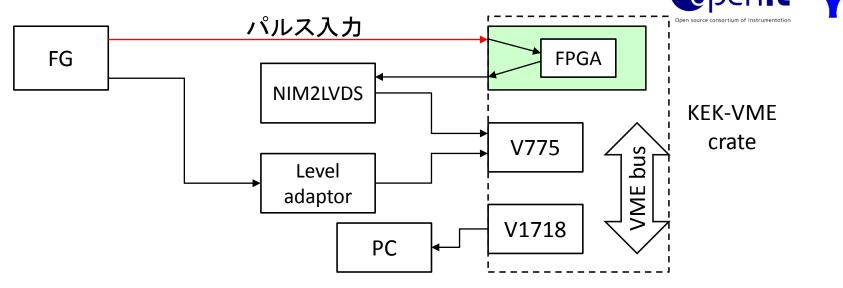

# いきなり本番用基板で開発を始めた

DRS4が初使用だったにも関わらずいきなり本番用基板から開発し始めた。 (DRS4は他のグループでよく動いていたので僕自身高を括っているところもあった。)

#### 結果

- 作動配線の量が多くレイアウトに非常に時間かかった。

- それが祟って気軽にレイアウトや回路図の変更ができなくなった。

- 本気のFPGA Firmwareを実装するまで開発が終了しなくなった。

- メインアンプの問題に気づいてはいたが放置せざるをえなくなった。

#### 本来は

右図のような試験基板から始めるべきであった特に初経験のアナログ技術を使うので、必須だった

Main AMP block (子ボード) DRS4 FPGA

1 GSPS以上の波形サンプリングが可能なSCA ASICであるDRS4を用いて、ケーブルディレイを排除するためのアナログバッファ搭載型QDCを開発した。

開発した基盤VME 6U規格であり、16chの入力を有する。

FPGA内部に2024 wordsのFIFOを実装しており、これをMulti-event bufferとして利用することができる。

#### 性能試験の結果

- Pedestal幅2.7 ch (σ) @ 0.135 pC/ch

- 時間分解能50 ps (σ) @ 300 mV入力

- 1%以下の非線形性

- 0.9%程度のQDC分解能 が得られた。

初めて使用するアナログ技術は必ず試験基板でノウハウを自分で得るべし。