# 高輝度LHC-ATLAS実験に向けた TGCバックエンドエレクトロニクスにおける 大規模ファームウェアの統合と試験運用

#### 三島章熙

東京大学理学系研究科物理学専攻 石野研究室 修士課程2年 ATLAS日本トリガーグループ

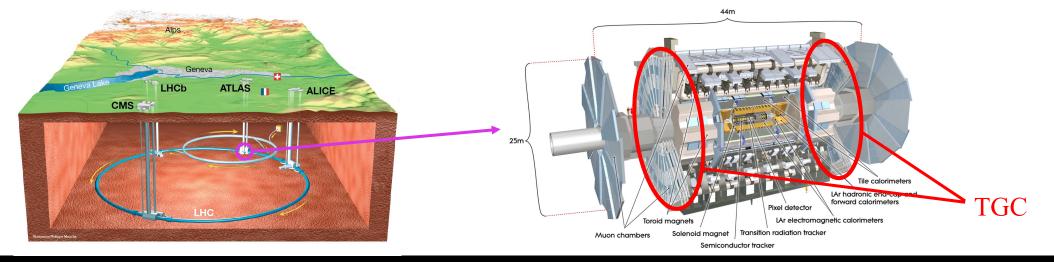

# 高輝度LHC-ATLAS実験

• CERNのLHC加速器は、"高輝度LHC"にアップグレードされ2029年に運転開始予定

|            | 瞬間Luminosity (cm <sup>-2</sup> s <sup>-1</sup> ) | 初段トリガーレート(kHz) | 初段トリガーレイテンシ(μs) |

|------------|--------------------------------------------------|----------------|-----------------|

| LHC (Run3) | $2 \times 10^{34}$                               | 100            | 2.5             |

| 高輝度LHC     | $5-7.5 \times 10^{34}$                           | 1000           | 10              |

- 加速器のアップグレードに伴い、TGC検出器では読み出しおよびトリガーを担うエレクトロニクスが全て刷新される

- TGC (Thin Gap Chamber)検出器は、読み出し32万チャンネルを持つ、MWPCタイプの検出器である

- ワイヤー電極とストリップ電極による2次元読み出しがあり、それぞれでミューオンの飛跡を再構成する

- さらに、磁場内部のミューオン飛跡検出器 (inner muon detector) とのマッチングをとり、飛跡候補をコンファームする

#### TGC検出器 エレクトロニクスの概要

• TGC検出器からの生の電流信号は電圧信号に変換・増幅され、コンパレータにかけられる 閾値電圧を超えた信号はデジタル信号に変換されてエレクトロニクスで処理される

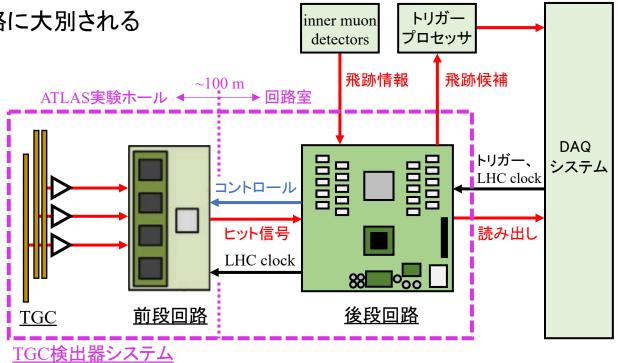

• TGC検出器システムのエレクトロニクスは前段回路と後段回路に大別される

- <u>前段回路</u> (1434 boards)

- ATLAS実験ホール内に設置される

- TGCからのヒット信号を、LHCの陽子バンチ交差 (40 MHz) に同定・同期させる

- 全てのヒット信号を後段回路へ転送する

- <u>後段回路</u> (48 boards)

- 検出器から離れた回路室に設置される

- ミューオンの飛跡再構成および横運動量の概算を行う

- トリガープロセッサへ飛跡候補を転送する

- トリガーアクセプトを受けたイベントのヒット信号をDAQシステムへ読み出す

- 前段回路のコントールパスのマスターとなる

- DAQシステムから配られるLHC clockを、前段回路へ、fixed latencyで (i.e. 位相の不定性なしに) 中継する

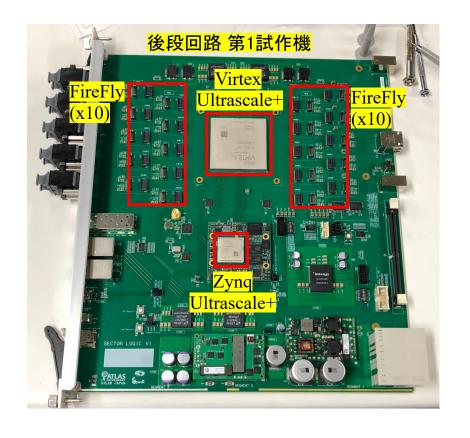

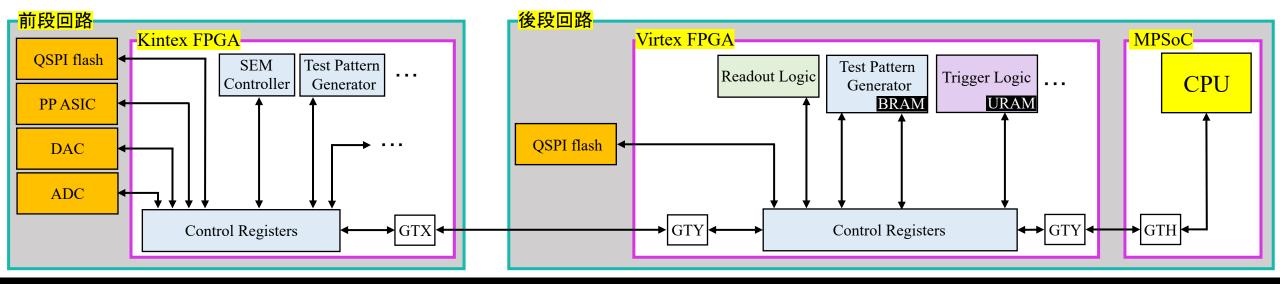

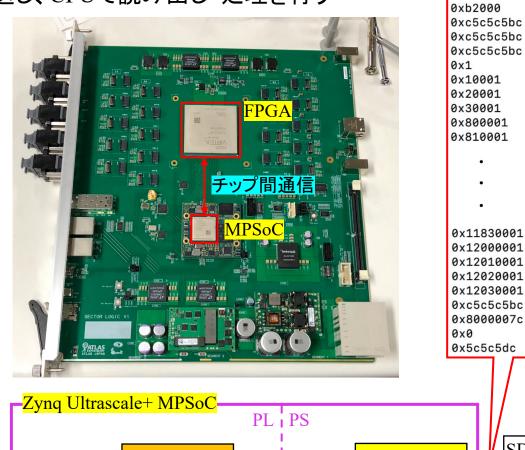

#### 後段回路ハードウェア

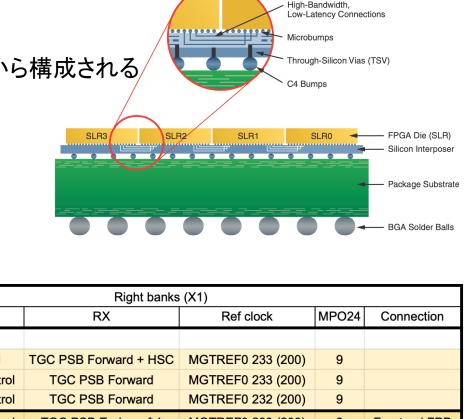

- 後段回路はATCA規格のボードに実装される(右図)

- Virtex Ultrascale+ FPGA

- 4つのシリコンダイ (SLR: Super Logic Region)から構成される、

- ~10 Gbps x 120 channelsのI/Oを持つ大規模SSIデバイス (入力120 channels + 出力120 channels)

- 読み出し回路およびトリガー回路が実装される

- 前段回路とのインターフェイスとして機能する

- Zynq Ultrascale+ MPSoC

- FPGAに対するコントロールパスのマスターとなる

- ATLASのTDAQ serverやDetector Control Systemとのインターフェイスとして機能する

- Single Board commissioningにおける読み出しマスターとなる

- FireFly (x20)

- ~10 Gbps x 12 channelsを持つ光リンクモジュール

- FPGAがもつI/Oと接続されている

- 前段回路やDAQシステム、トリガープロセッサと光ファイバー経由で接続される

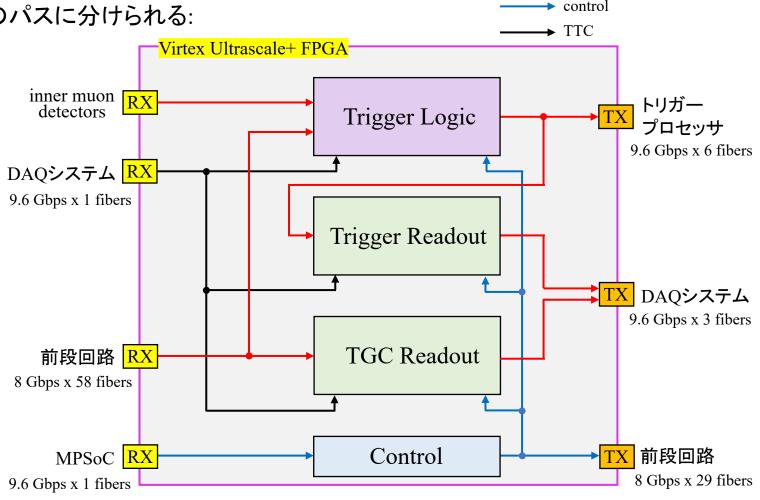

#### FPGAファームウェアの全体像

- FPGAに実装されるファームウェアは、次の3つのパスに分けられる:

- トリガー回路

- 読み出し回路

- コントロールパス

- LHCが配布するclockやトリガープロセッサが 発行するトリガーアクセプト信号は、TTCとして DAQシステムから受信する

- I/OにはXilinxのギガビットトランシーバ (GTY) を用いている

- Virtex Ultrascale+ speedgrade -1において は25.785 Gbpsまでサポートされている

data

• 本研究では、I/Oを含むこれらのモジュールの性質を詳細に理解した上で、SLRレイアウトの工夫やチップ間通信の技術、 timing violation解決のためのアイデアなどをコンバインし、実験本番での運用を見据えた統合・試験を行った

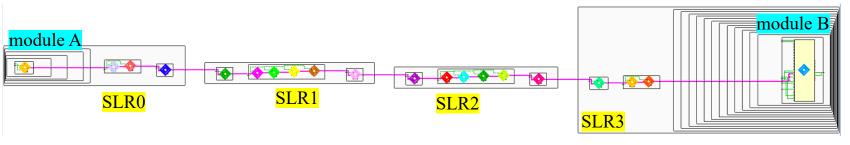

#### SLRフロアプラン

• 後段回路のFPGA (xcvu13p-flga2577-1-e)は4つのSLR (Super Logic Region)から構成される

• SLRレイアウトは次の制約を考慮して最適化している

- SLL (Super Long Line)のリソース量

- SLLを通過する際の信号遅延

- LUT、REG、RAM、GTYなどのリソース量

- I/Oの配置は、SLRレイアウトやreference clockピンの配置、およびMPO24の バンドル具合を考慮して定義している

| `                            | Left banks (X0) |         |               |                         | Right banks (X1) |              |      |                 |                       |                   |       |              |

|------------------------------|-----------------|---------|---------------|-------------------------|------------------|--------------|------|-----------------|-----------------------|-------------------|-------|--------------|

|                              | Bank            | TX      | RX            | Ref clock               | MPO24            | Connection   | Bank | TX              | RX                    | Ref clock         | MPO24 | Connection   |

|                              | 135             | Others  | Others        | MGTREF0 135 (125)       |                  |              | 235  |                 |                       |                   |       |              |

| SLR3                         | 134             |         |               |                         | 4                |              | 234  | HSC Control     | TGC PSB Forward + HSC | MGTREF0 233 (200) | 9     |              |

| SLNS                         | 133             |         |               |                         | 4                |              | 233  | TGC PSB Control | TGC PSB Forward       | MGTREF0 233 (200) | 9     |              |

|                              | 132             | (FELIX) | (FELIX)       | (MGTREF1 132 (160.316)) | 4                |              | 232  | TGC PSB Control | TGC PSB Forward       | MGTREF0 232 (200) | 9     |              |

|                              | 131             |         | TGC Endcap Φ1 | MGTREF0 131 (240)       | 3                | Frontend FPP | 231  | TGC PSB Control | TGC PSB Endcap Φ1     | MGTREF0 230 (200) | 8     | Frontend FPP |

| SLR2                         | 130             |         | TGC Endcap Φ1 | MGTREF0 131 (240)       | 3                | Frontend FPP | 230  | TGC PSB Control | TGC PSB Endcap Φ1     | MGTREF0 230 (200) | 8     | Frontend FPP |

| JLNZ                         | 129             |         | TGC Endcap Φ1 | MGTREF0 129 (240)       | 3                | Frontend FPP | 229  | TGC PSB Control | TGC PSB Endcap Φ1     | MGTREF0 230 (200) | 8     | Frontend FPP |

|                              | 128             |         |               | MGTREF0 129 (240)       | 2                | MDTTP FPP    | 228  |                 | TGC EIL4              |                   | 7     | Frontend FPP |

|                              | 127             | MDTTP   | MDTTP         | MGTREF0 125 (240)       | 2                | MDTTP FPP    | 227  |                 | NSW                   | MGTREF0 226 (200) | 7     | Frontend FPP |

| SLR1                         | 126             | MDTTP   | MDTTP         | MGTREF0 125 (240)       | 2                | MDTTP FPP    | 226  |                 | NSW                   | MGTREF0 226 (200) | 7     | Frontend FPP |

| (master)                     | 125             | MUCTPI  | RPC BIS78     | MGTREF0 125 (240)       | 1                | FELIX FPP    | 225  |                 |                       |                   | 6     |              |

|                              | 124             | MUCTPI  | Tiles         | MGTREF0 125 (240)       | 1                | FELIX FPP    | 224  |                 |                       |                   | 6     |              |

|                              | 123             | FELIX   | FELIX         | MGTREF1 123 (160.316)   | 1                | FELIX FPP    | 223  |                 |                       |                   | 6     |              |

| SLR0                         | 122             |         | TGC Endcap Φ0 | MGTREF0 122 (240)       | 0                | Frontend FPP | 222  | TGC PSB Control | TGC PSB Endcap Φ0     | MGTREF0 221 (200) | 5     | Frontend FPP |

| SLRU                         | 121             |         | TGC Endcap Φ0 | MGTREF0 122 (240)       | 0                | Frontend FPP | 221  | TGC PSB Control | TGC PSB Endcap Φ0     | MGTREF0 221 (200) | 5     | Frontend FPP |

|                              | 120             |         | TGC Endcap Φ0 | MGTREF0 122 (240)       | 0                | Frontend FPP | 220  | TGC PSB Control | TGC PSB Endcap Φ0     | MGTREF0 221 (200) | 5     | Frontend FPP |

| 2022/11/10 = 120 フェル理体へ 2022 |                 |         |               |                         |                  |              |      |                 |                       |                   |       |              |

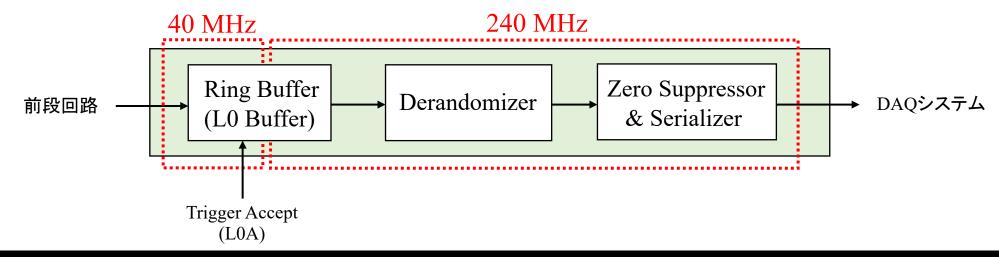

# 読み出し回路の基本設計

- Ring Buffer (L0 Buffer)

- 前段回路から送られてくる7936 bit幅のbitmap@40 MHzを格納しておき、トリガーされたイベントを含む前後4イベント分を、240 MHzのclock tick毎に、fixed latencyで読み出す

- Derandomizer

- 圧縮・シリアル化の処理待ちバッファーである

- これ以降は、latency-sensitiveでなく、queueingの概念が発生する

- Zero Suppressor & Serializer

- bitmapを16 bit幅のセルに区切り、ヒットがあったセルのbitmapのみ、240 MHzのclock tick毎に読み出す

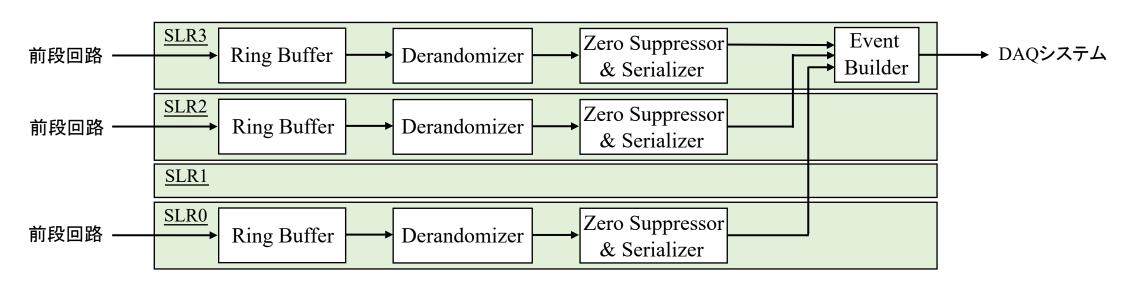

# 読み出し回路の実装

- I/Oやクロックピンの配置を考慮して、SLRレイアウトを最適化している

- 前段回路とのリンクはSLR0/2/3に配置される

- DAQシステムとのリンクはSLR3に配置される

- → SLRを跨ぐ信号線幅を最小化するため、各SLRであらかじめシリアル化して、SLR3へ転送している SLR3において、各SLRからのデータをイベント毎にパックし、DAQシステムが定めるフォーマットに従って読み出す

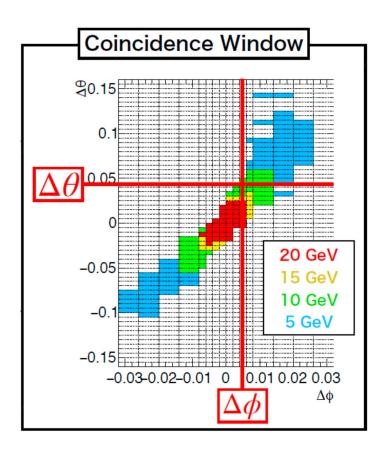

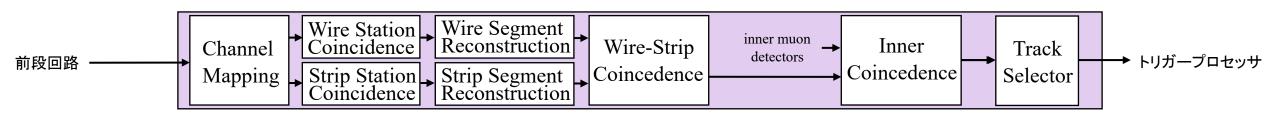

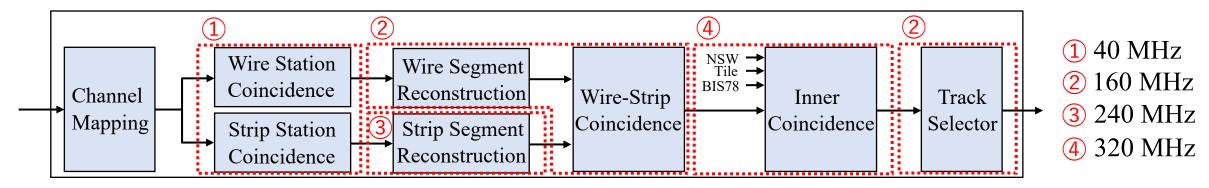

#### トリガーロジックの概要

- TGCは7層のチェンバーから構成され、各層でwireとstripによる2次元読み出しが行われる

- 最初に、wireとstripのそれぞれで、7層間のコインシデンスがとられる (Station CoincidenceおよびSegment Reconstruction)

- 次に、wireとstripのコインシデンスをとり、ミューオンの飛跡を再構成する (Wire-Strip Coincidence)

- さらに、inner muon detectorsとのマッチングをとり、飛跡情報の精度を向上させる (Inner Coincidence)

- 最後に、トリガープロセッサへ転送する飛跡候補を選別する (Track Selector)

• コインシデンスや飛跡再構成では、ヒット情報と、LUTに格納されたパターンとのマッチングをとって行う(右上図)

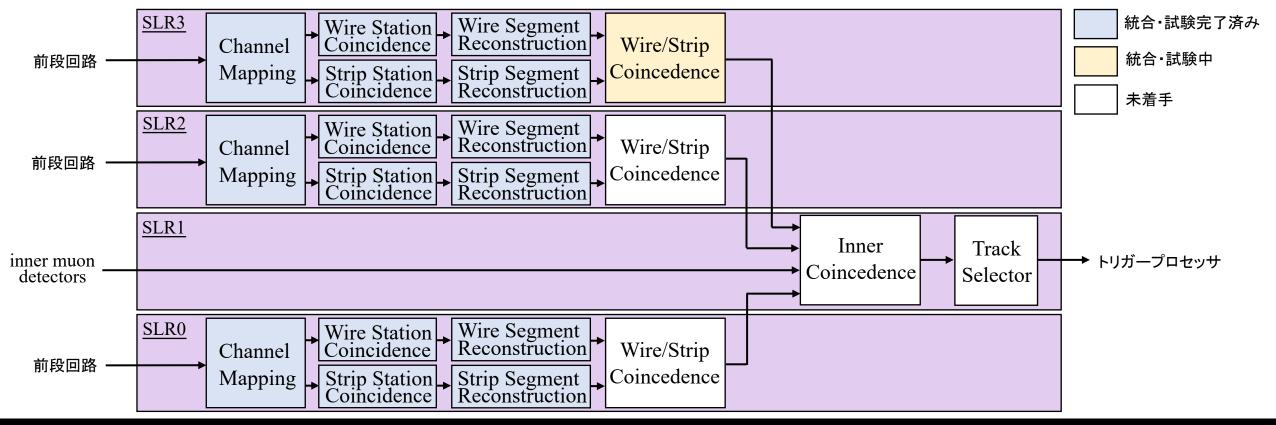

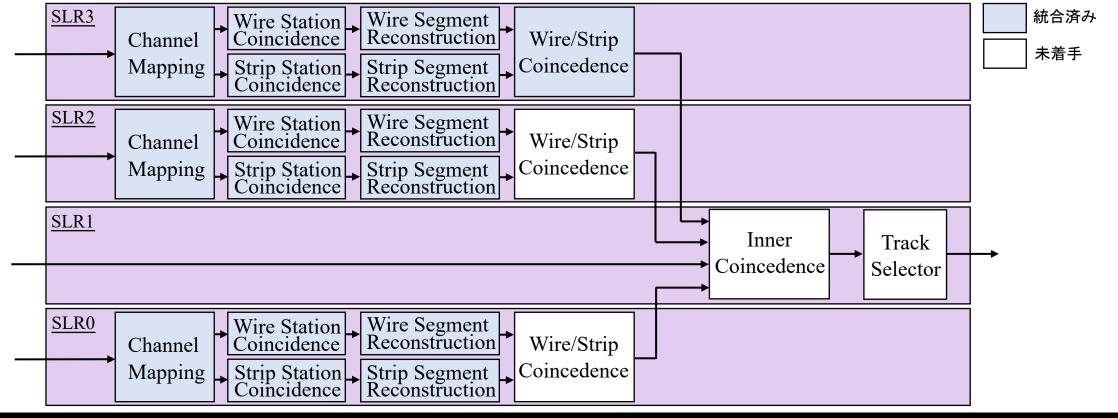

# トリガー回路の統合

- 読み出し回路・I/Oをベースに、Trigger Logicの各モジュールの統合・試験を、前段回路側から段階的に進めている

- 各モジュールの出力を読み出し回路を用いてモニターし、正しさを確認しながら1段ずつ足していく

- 読み出し回路と同様、I/Oの配置を考慮して、SLRレイアウトを最適化している

- SLR0/2/3のそれぞれでTGCのヒットデータを用いたコインシデンスをとる

- SLR1でinner muon detectorsからのデータを用いたコインシデンスと、最終的な飛跡選別を行う

#### コントロールパスの統合

- LHC clockとは非同期なスローなコントロールを行う

- 回路状態のモニター、回路のソフトリセット、Trigger Logic内のRAMへの書き込み、など

- RAMには、飛跡再構成のためのLUTパターン (1 MB程度)を書き込んでいる (およそ0.5秒程度かかる)

- MPSoCからチップ間通信を使い、FPGA内のレジスタを読み書きすることで実現している

- 前段回路へのコントロール信号も中継している

- SEUのモニター、コンパレータにおける閾値電圧の制御、陽子バンチ交差IDにおける遅延パラメータの制御、など

- 現在、必要な機能を全て実装し、実機における動作検証に活用している

# リソース使用量

- 読み出し回路、コントロールパス、および下図における統合済 み(青色ブロック)のトリガー回路を実装した結果、リソース使 用量は右表のようになる

- 未着手のブロックについても、統合前のリソース使用量を考慮 すると十分な余裕を持って実装可能であると見込んでいる

|       | LUT       | REG       | BRAM   | URAM   |  |

|-------|-----------|-----------|--------|--------|--|

|       | (1728000) | (3456000) | (2688) | (1280) |  |

| SLR0  | 9.66      | 3.78      | 9.78   | 12.76  |  |

| SLR1  | 0.06      | 0.15      | 0.00   | 0.00   |  |

| SLR2  | 10.04     | 4.23      | 11.38  | 12.76  |  |

| SLR3  | 5.23      | 2.25      | 10.05  | 5.16   |  |

| Total | 25.00     | 10.42     | 31.21  | 30.68  |  |

(%)

# timing closureの改善(1)

- SLRをまたぐ信号線のtiming closureを緩和するために数段のレジスタを挟んでいる (右図および下図)

- 特に、読み出し回路は、latency-sensitiveなパスではないので、十分に緩めておいて、latency-sensitiveなトリガー回路のtiming closureにリソースを回せるようにしている

# timing closureの改善(2)

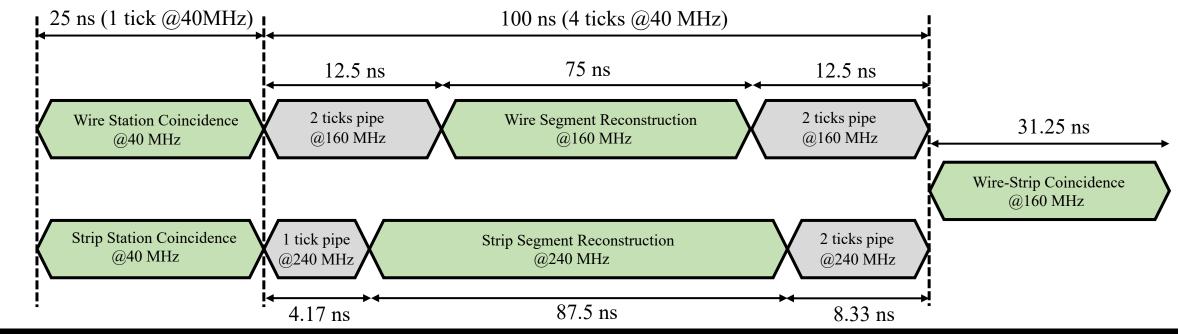

• トリガー回路では次の図に示すようなクロックドメインが敷かれている

• timing closureを改善するため、クロックドメインをまたぐ箇所には数段のパイプラインレジスタを挟んでいる(下図)

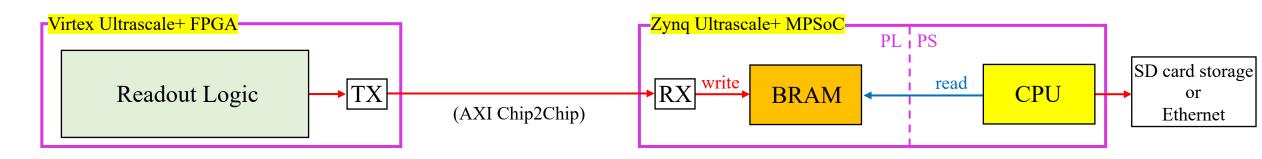

#### Single Board DAQ

- 実装した回路のデモンストレーションを行うため、後段回路上での試験フレームワークを構築した

- FPGAの出力を、チップ間通信を用いてMPSoCのRAMへ転送し、CPUで読み出し・処理を行う

• 読み出したデータは、SDカードのストレージや、Ethernetを介して外部に転送され、保存される

read

**CPU**

Readout Logic TX

Virtex Ultrascale+ FPGA

(AXI Chip2Chip)

write

**BRAM**

SD card storage

or

Ethernet

dumped data

0x900dba5e

0x10ff1ce 0xba110005

0x0 0x0

0x43

SOP

header

hit data

trailer

**EOP**

# 実機における動作検証

- Single Board DAQを活用した動作検証を行なっている

- 前段回路の出力を模したテストパターンをFPGA内から打ち込んでいる

- テストパターンのパターン指定やトリガーはコントロールパスから行う

- 回路の出力は、トリガーロジックをソフトウェアでシミュレートした結果とマッチングをとり、その正しさを検証している - トリガーレート 1 kHzで20時間程度動かし続けても、マッチングエラーが発生しないことを確認している

<mark>テストパターン</mark> 001011010...

> Logic Simulator

<mark>シミュレーション結果</mark> 010000001...

比較検証

# まとめと今後の発展

- 実験本番を見据えた読み出し回路・トリガー回路の統合と動作検証

- I/O・読み出し回路・コントロールパスを実装した

- 大規模SSIデバイスにおける全SLRワイドなファームウェアを実現している

- I/Oやクロックピンの配置をもとにして最適なSLRレイアウトをデザインしている

- 現在はトリガー回路の統合を行っている

- 回路の大規模化に伴い、timing violationのケアが必要になる

- 特に、クロックドメインを跨ぐ箇所でtiming violationが発生しやすいことが分かっている

- → これらの筒所では、パイプラインレジスタを配置し、解決している

- 現在までに統合が完了している回路については、テストパタ―ンを用いた実機試験により動作検証を行った

- → 実装済みの回路は全て正しくワークしている

#### ・ 今後の発展

- 全てのトリガー回路の統合および動作検証を完了させ、後段回路ファームウェア全体の完成を目指す

- 前段回路との統合試験を行い、TGC検出器エレクトロニクス全体でのコミッショニングを進める

- MPSoCからコントロールパスを経由して前段回路へアクセスし、テストパルスなどの制御を行う

- 前段回路から生成されたテストデータがMPSoCのRAMへ正しく読み出されることを確認する

# Back up

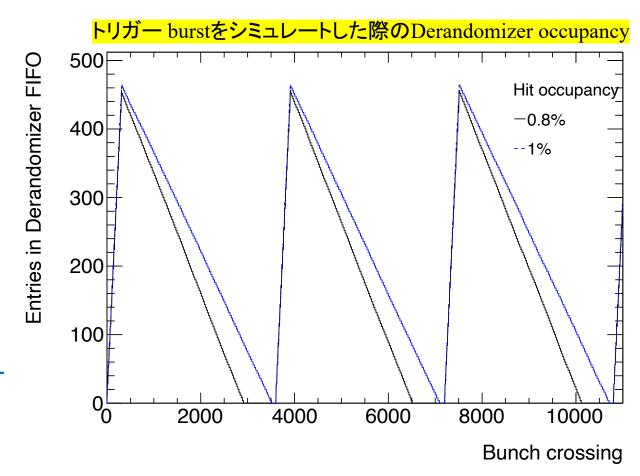

#### Derandomizer occupancyのシミュレーション

- トリガーが短時間に集中してburstされてくるような場合を想定したシミュレーションを行った

- ATLASでは、ある期間の中のトリガー数を制限している:

- 5 連続バンチ交差中にMax.4

- 20 連続バンチ交差中にMax.8

- 3600 連続バンチ交差中にMax.128

- → 最も厳しいケースをシミュレートした

- 瞬間Luminosity 7.5x10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>において、TGCにおける ヒット数は、過去の実験結果の外挿から、およそ 64 hit (ヒットoccupancy: 0.8%) である

- → Derandomizerの深さを512としておけば、オーバーフロー を起こすことなく稼働し続けることが可能

(さらに、Derandomizerがalmost fullになった場合には、Derandomizerから読み出したデータを切り捨て、最速で読み出しを 行っていくことで、occpancyを効率的に下げていく機構も用意しており、トリガーburstに対してロバストな設計になっている)

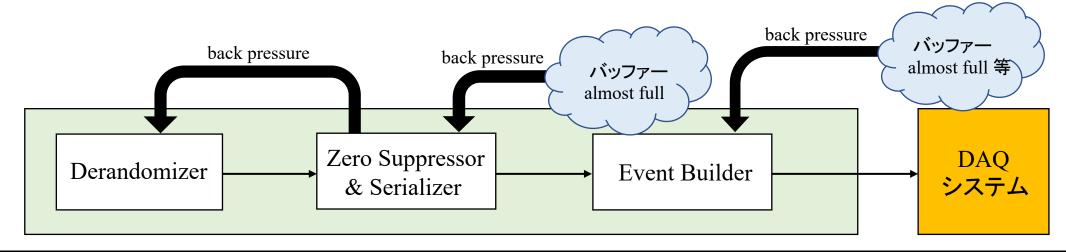

# DAQシステムからのback pressure

- DAQシステムはバッファーオーバーフローを防ぐために、読み出し回路側のデータ転送を停止させることがある

- Event BuilderはZero Suppressorから受信したデータを格納しておくバッファーを用意している

- → DAQシステムへの出力を停止していても、このバッファーの容量内であれば転送データを保持できる

- Event Builder内のバッファーがalmost fullになった場合、Zero Suppressorのデータ転送を停止させる

- → Derandomizerからの読み出しが停止し、occupancyが増大していく

- → DAQシステムバッファーのoccupancyが改善しなければ、TGC検出器システムはbusyを発行することになる (読み出し回路側では対処する余地のない結果であり、TGC+DAQシステムのバッファー能力の限界である)

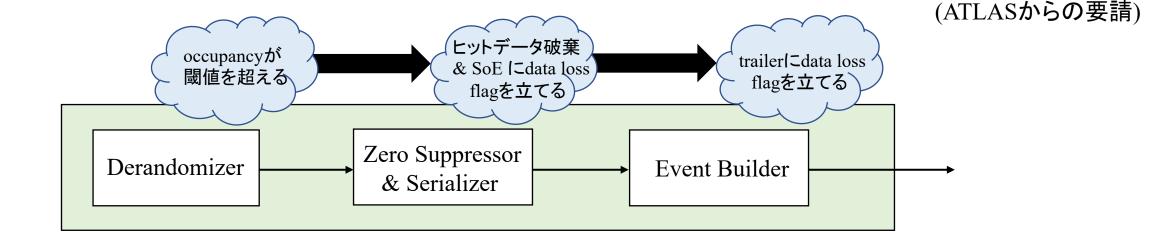

# Derandomizerにおけるbusyとdata loss

- Derandomizerのoccupancyがとある閾値 (e.g. 95%)を超えたら、DAQシステムへbusy信号を送る (ATLASからの要請)

- しかし、busyを立てるとATLAS全体のデータ取得が中断されてしまう

- → より低い閾値 (e.g. 90%)を設定し、それを超えたらZero Suppressorを"truncation mode"に切り替え、 Derandomizerに格納されているデータを最速で読み出し・処理をしていく

- "truncation mode"のZero Suppressorは、Derandomizerから読み出したヒットデータはそのまま破棄し、SoE/EoEのみ転送する

- → Zero Suppressorにおける処理時間を最小にすることで、Derandomizerのoccupancyを効率的に下げていく (このとき、Event Builderに"truncation mode" に切り替わったことを知らせるため、SoE/EoEにdata loss flagを立てる)

- Event Builderは、data lossが起こっているイベントを受信したら、DAQシステムへ送信するtrailerにdata loss flagを立てる

# モジュール毎のリソース使用量

- 統合前の単体の値を右表に示す

- 全ての統合が完了した場合の予想値を下表に示す

|       | LUT       | REG       | BRAM   | URAM   |

|-------|-----------|-----------|--------|--------|

|       | (1728000) | (3456000) | (2688) | (1280) |

| SLR0  | 11.37     | 4.55      | 15.29  | 12.76  |

| SLR1  | 9.75      | 1.15      | 9.00   | 10.63  |

| SLR2  | 11.77     | 5.00      | 16.86  | 12.76  |

| SLR3  | 5.23      | 2.45      | 10.03  | 10.00  |

| Total | 38.12     | 13.15     | 51.18  | 46.15  |

|                              |       | LUT       | REG       | CLB      | BRAM   | URAM   |

|------------------------------|-------|-----------|-----------|----------|--------|--------|

|                              |       | (1728000) | (3456000) | (216000) | (2688) | (1280) |

|                              | SLR0  | 1.27      | 1.14      | 2.82     | 6.81   | 0.00   |

| TGC Readout                  | SLR2  | 1.49      | 1.33      | 3.42     | 7.89   | 0.00   |

| 1GC Readout                  | SLR3  | 0.62      | 0.49      | 1.40     | 3.27   | 0.00   |

|                              | Total | 3.38      | 2.96      | 7.64     | 17.97  | 0.00   |

|                              | SLR0  | 0.42      | 0.12      | 1.06     | 0.00   | 0.00   |

| Wire Station Coincidence     | SLR2  | 0.42      | 0.12      | 1.06     | 0.00   | 0.00   |

| wire Station Coincidence     | SLR3  | 0.19      | 0.05      | 0.48     | 0.00   | 0.00   |

|                              | Total | 1.03      | 0.29      | 2.60     | 0.00   | 0.00   |

|                              | SLR0  | 0.00      | 0.05      | 0.21     | 0.00   | 0.00   |

| Strin Station Coincidence    | SLR2  | 0.00      | 0.05      | 0.19     | 0.00   | 0.00   |

| Strip Station Coincidence    | SLR3  | < 0.01    | 0.01      | 0.03     | 0.00   | 0.00   |

|                              | Total | < 0.01    | 0.11      | 0.43     | 0.00   | 0.00   |

|                              | SLR0  | 6.15      | 1.20      | 9.31     | 0.00   | 11.20  |

| Wire Segment Reconstruction  | SLR2  | 6.15      | 1.20      | 9.31     | 0.00   | 11.20  |

| wire segment Reconstruction  | SLR3  | 2.66      | 0.52      | 4.03     | 0.00   | 4.84   |

|                              | Total | 14.96     | 2.92      | 22.65    | 0.00   | 27.24  |

|                              | SLR0  | 1.59      | 0.77      | 2.67     | 0.00   | 1.56   |

| Strip Segment Reconstruction | SLR2  | 1.59      | 0.77      | 2.74     | 0.00   | 1.56   |

| Strip Segment Reconstruction | SLR3  | 0.32      | 0.15      | 0.55     | 0.00   | 0.31   |

|                              | Total | 3.50      | 1.69      | 5.96     | 0.00   | 3.43   |

|                              | SLR0  | 1.29      | 0.65      | 2.36     | 5.51   | 0.00   |

| Wine /Chris Coinsiders       | SLR2  | 1.29      | 0.65      | 2.36     | 5.51   | 0.00   |

| Wire/Strip Coincidence       | SLR3  | 0.60      | 0.35      | 1.12     | 2.38   | 0.00   |

|                              | Total | 3.18      | 1.65      | 5.84     | 13.40  | 0.00   |

| Inner Coincidence            | SLR1  | 7.69      | 0.74      | 12.93    | 9.00   | 10.63  |

| Track Selector               | SLR1  | 2.00      | 0.26      | 2.61     | 0.00   | 0.00   |

#### Single Board DAQ performance

- データ取得レートは、CPUからRAMのデータを読んで、SDカードのストレージに保存する速度で律速される

- PLのBRAMからSDカードストレージへのデータ転送速度は、O(1) Mbps程度である

- 1イベントのデータサイズは100 words程度である (1 wordは32 bit幅)

- ただし、TGCのhit occupancyに依存する

- $\rightarrow$  RAMのオーバーフローを起こさずに走らせ続けるには、トリガーレートをO(1) kHz程度にする必要がある

- DMAを用いて、PS RAMへ直接書き込むパスを用いれば、SDカードストレージへのデータ転送速度は向上するので、トリガーレートをO(1) MHz程度まで引き上げることができる可能性がある

#### FPGAの自動コンフィギュレーションシステム

- FPGAに書き込むファームウェアやコンフィギュレーションに必要なパラメータは、後段回路上の不揮発性メモリ(QSPI flash) に格納しておき、ボードの電源がオンになると同時に、自動でコンフィギュレーションが開始される

- これにより、48枚ある後段回路の全てに対し、Runが始まる度にアクセスして、各ボードに固有なパラメータを参照しながら、 手動でコンフィギュレーションを行う必要がなくなる

- また、MPSoCから、手動で再コンフィギュレーションを指示することもできる

- このシステムは、前段回路における自立型制御機構をもとにしたものである:

- 青木匠, Full-system commissioning of TGC frontend electronics for Phase-2 LHC-ATLAS, 計測システム研究会2021