# 数値シミュレーションを用いた Slope ADC の到達性能の研究

大阪大学 核物理研究センター 小林 信之

### コンテンツ

- \* Slope ADC?

- \*背景、動機

- \* Slope ADC の開発

- \*数値シミュレーションプログラム

- \*検討項目

- \*議論

### Slope ADC?

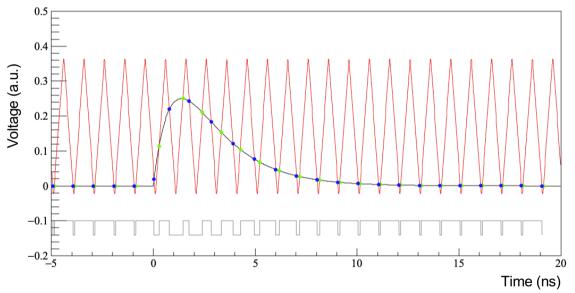

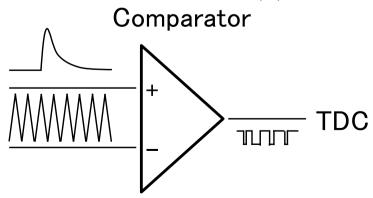

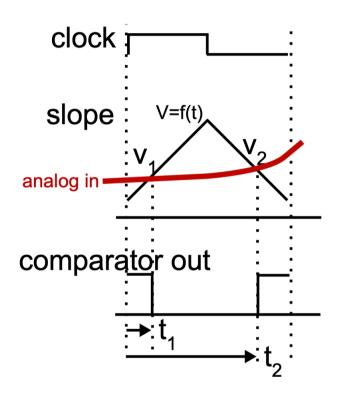

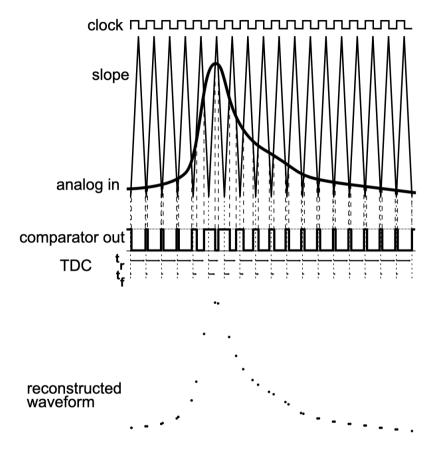

振動する Slope を用いて信号をスキャン Slope を跨いだ時間を記録 (TDC)

→ 波形の再構成、電荷と時刻情報を得る

赤: Slope

黒:信号

青、緑点: Slopeを跨いだ時間

黒: ロジック出力

必要なもの

- \* Slope 信号

- \* Comparator

- \* TDC

振動するスレッショルド電圧をかけてTDC情報を得る

### Slope ADC?

#### 長所

- コストが下がる可能性がある

- ・開発コストの面でも有利、TDCとして本多さんのAMANEQなど使える

- ・ストリーミングTDCで読み出せばストリーミングDAQへの対応も可能

- ゲートを使った電荷積分型のQDCのような遅延ケーブル要らず

#### 短所

- 非等間隔でサンプリングされたデータ→ 処理がFADCより複雑

- (等間隔のデータに変換、そのまま非等間隔で扱う)

- ADCの分解能は良くない

### 背景、動機

- ・需要調査から大まかに2つの需要がありそれぞれ異なる実装が必要であることが分かった。

- 需要1 遅いFADCを使って通常の読出し(波形をなまらせる)

- BGO、GAGGなどの無機シンチレーター(表の水色)

- 需要2 速いサンプリングでTOT、Slope ADC

- RPC、プラスチックシンチレーター(表の緑色)

- HRTDCが単価(昔5k/ch)低下するならTOTでなんとかした方がよいだろう。マルチthreshold化等の検証が必要。スロープADCも要検証

Slope ADC の評価・検討をRCNPデータ収集基盤室で行う

- → まずは原理検証、シミュレーションからスタート

- \* Comparator 評価ボードと RFSoC を用いた原理検証 (高橋さん、味村さん)

- \* 数値シミュレーション (その他の人、SPADI-A WG1 TF)

### 需要調査

#### 想定される需要

各参加者が想定している**信号についての調査**をおこなった。調査内容としては想定される入力信号の時定数、波高及びQDCとしての要求性能について調べた。要求性能については主に時間分解能、エネルギー分解能について調査した。それぞれの調査結果を以下にまとめる。

| 検出器            | 時定数        | 波高             | 時間分解能               | エネルギー分解能           | 備考                  |

|----------------|------------|----------------|---------------------|--------------------|---------------------|

| BGO            | ~ 300ns    | ~ 100mV        | ~ 300ps             | < 1%               | カロリメーター用            |

| PWO            | ~ 30ns     | ~ 1V           | ~ 300ps             | < 1%               | カロリメーター用            |

| 鉛+シンチ          | ~ 10s      | ~ 100mV        | ~ 300ps             | ~ few %            | サンプリングカロリ<br>メーター   |

| CsI(Tl)        | ~ 1us      | ~ 100mV        | ~ 10ns              | ~ 1%               | 時間分解能は余り気<br>にしない   |

| CsI(pure)      | ~ 100ns    | ~ 100mV        | ~ 10ns              | ~ 1%               | 時間分解能は余り気<br>にしない   |

| GAGG           | ~ few 10ns | ~ 100mV        | no request          | no request         |                     |

| LySO           | ~ 50ns     | unknown        | no request          | no request         |                     |

| NaI            | long       | unknown        | no request          | no request         |                     |

| プラスチックシンチ レーター | ~ 10ns     | ~ 1V           | < 100ps             | QTCで代用可能           |                     |

| PPAC           | 30 ~ 40ns  | $40\sim 50 mV$ | no request          | ~ few %            | *1                  |

| 鉛ガラス           | < few 10ns | ~ 1V           | no request          | no request         | *2                  |

| RPC            | ~ 10ns     | ~ mV order     | important < 100 ps? | slewing correction |                     |

| 中性子検出器(LEPS)   | ~ 10ns     | ~ 100mV        |                     |                    | シンチレーター<br>(L=2m)   |

| 中性子検出器(E80)    | ~ 10ns     | ~ 100mV        |                     |                    | LEPSとほぼ同じ<br>(L=3m) |

### 開発項目

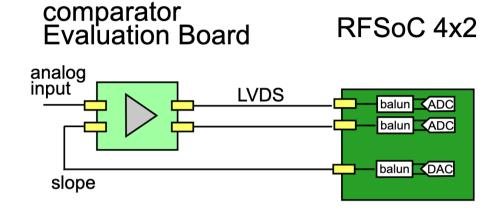

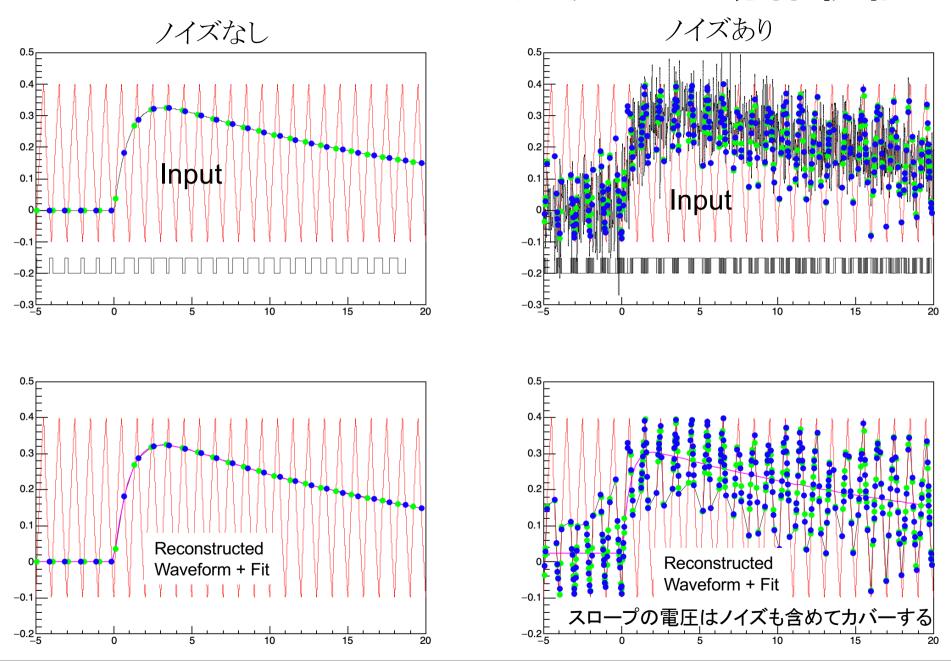

Comparator 評価ボード & RFSoC を用いた原理検証 (高橋さん、味村さん)

- RFSoC 4x2があるので<del>遊んでみる</del>試してみる

- DAC: slope作成

- ADC: comparator outのLVDS(デジタル信号)を入力

- LVDS信号波形を解析してTDCの代わりにする

- お手軽(?)な高分解能の時間計測

- FPGA-TDCの性能(実装)とは独立なstudyが可能

- コンパレータの種類, slopeの周波数, slopeの形, single-ended/differential などを変えて測定

高橋さんスライドより借用

数値シミュレーション (その他の人、SPADI-A WG1 TF)

性能見積もり (C++ で作成、ROOTで表示)

→ 実機作成、性能評価 (SPADI-A WG1 TF?)

### 性能の見積り

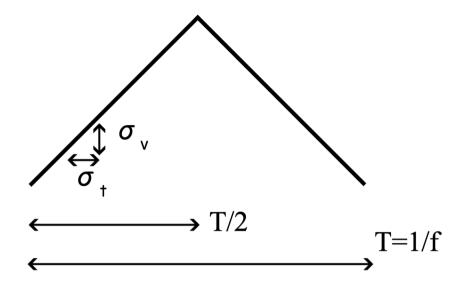

- TDCの時間分解能 =  $\sigma_t$

- slopeの周波数 = *f*

- $\circ$  周期 =  $T = \frac{1}{f}$

- (理想的な場合の)ADC分解能 = N bits

$$\circ$$

$rac{T}{2}=rac{1}{2f}=2^N\cdot\sigma_t$

$$\circ \frac{\sigma_V}{\sigma_t} \sim \frac{dV}{dt}$$

例:

$$\sigma_t$$

= 10 ps,  $f$  = 500 MHz (= 1 Gsps)  $\Rightarrow rac{T}{2\sigma_t}$  = 100  $\Rightarrow N$  = 6.6

実際にはもっと悪くなる

- コンパレータの性能 (ジッタ、ノイズ、...)

- slopeの形, 安定性, ...

高橋さんSPADI-A Monthly meeting スライドより

なにが性能に効くのかよくわからない 波形処理のアルゴリズムも検討が必要 → シミュレーション

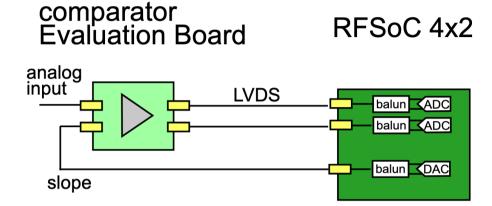

## 数値シミュレーションによる Slope ADCの性能評価

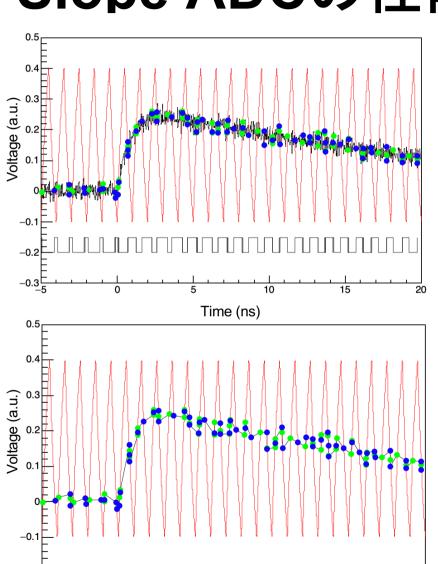

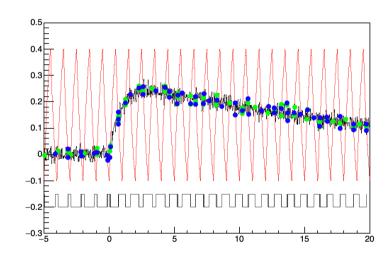

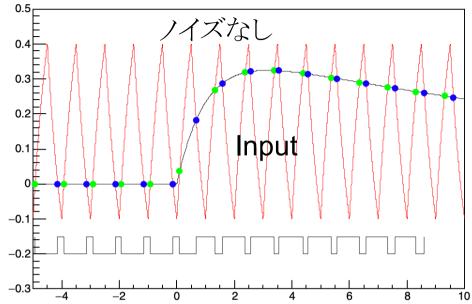

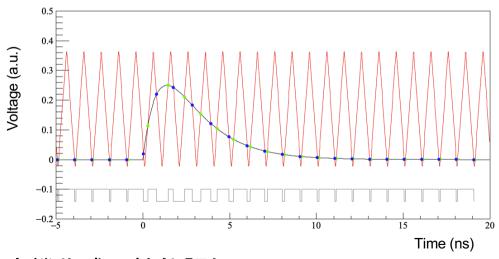

Time (ns)

- \* 信号+ノイズ生成 (ΔV)

- \* Slope 生成

- \* 比較器で比較

- \* 比較器出力を 時間分解能、ジッターで鈍らせる  $(\sigma_t)$

- → TDC 情報出力

#### TDC情報から

- \* 仮定するSlopeを生成

- \*波形を再構成

- \* なんらかのアルゴリズムで時刻、電荷情報を計算

### 評価したい項目

- \*ノイズの大きさ、TDCの分解能 vs. 電荷分解能

- \* 電荷の線形性(vs. ノイズの大きさ)

- \* 実際のSlope と想定する Slope の違い vs. 電荷分解能

- \* 遅い波形 vs. 電荷分解能

- \* 時刻、電荷情報決定のアルゴリズム (台形フィルター etc.)

- \*スルー補正の方法

- \* 適用範囲 (遅い波形にも適用可能か?)

- \* 周波数とSlopeの最適化

- -- 周波数が大きいと、ADC分解能が悪くなる。

- 一方、サンプリング数は増える。

- → いいところはある?

- -- 三角波の代わりに指数関数、Sinカーブ?

10

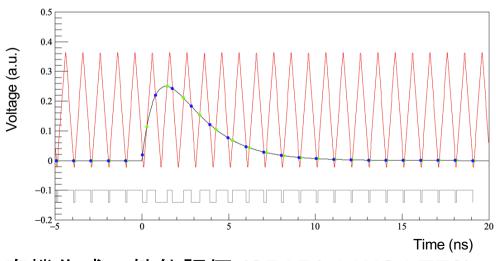

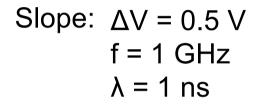

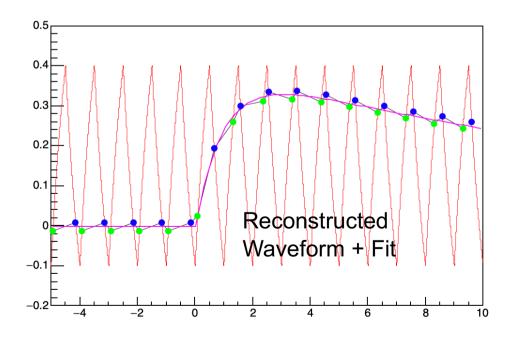

### シミュレーションプログラムの動作検証

Signal:

$$A(-e^{-t/\tau_1} + e^{-t/\tau_2})$$

$\tau_1 = 1 \text{ ns}, \tau_2 = 20 \text{ ns}, A = 0.4$

仮定するSlope を 10 ps シフト

→ ジグザグパターン

Fit すると電荷で 1 % の違い

### シミュレーションプログラムの動作検証

### 今後

- \* ノイズの与え方改善 --- ホワイトノイズ、周期的ノイズ (sinカーブ)

- \* 時刻、電荷決定アルゴリズムの実装 非等間隔のサンプリングでちょっと面倒

- \*スル一補正

- \*他の人も使えるように

### まとめ

Comparator 評価ボード & RFSoC を用いた原理検証 (高橋さん、味村さん)

- RFSoC 4x2があるので<del>遊んでみる</del>試してみる

- DAC: slope作成

- ADC: comparator outのLVDS(デジタル信号)を入力

- LVDS信号波形を解析してTDCの代わりにする

- お手軽(?)な高分解能の時間計測

- FPGA-TDCの性能(実装)とは独立なstudyが可能

- コンパレータの種類, slopeの周波数, slopeの形, single-ended/differential などを変えて測定

高橋さんスライドより借用

数値シミュレーション (その他の人、SPADI-A WG1 TF)

→ 実機作成、性能評価 (SPADI-A WG1 TF?)

性能見積もり (C++ で作成、ROOTで表示) ベースはできた

SPADI-A WG1: 数値シミュレーションによる Slope ADC の性能評価TF 申し込みフォーム

https://forms.gle/Bwb4adCQ2qGFjqTY7

### コラボレータ

大阪大学 核物理研究センター

高橋智則、味村周平、柳善永、大田晋輔

**KEK IPNS**

本多良太郎、五十嵐洋一

### **Backup**

### Slope ADC (2):時間測定 ▶ 波形再構成

thresholdのslope信号は周期的

▶ 各サイクルでthresholdと交差した時刻 (= 位相)を測れば波高がわかる

4/10

高橋さんSPADI-A Monthly meeting スライドより

### 参考文献

\* J. Wu et al., "Improving single slope ADC and an example implemented in FPGA with 16.7 GHz equivalent counter clock frequency" <a href="https://doi.org/10.1109/NSSMIC.2011.6154442">https://doi.org/10.1109/NSSMIC.2011.6154442</a>

\* H. Homulle et al.,"A Cryogenic 1 GSa/s, Soft-Core FPGA ADC for Quantum Computing Applications,"

https://doi.org/10.1109/TCSI.2016.2599927

\* A. Nishimura et al., "Observational demonstration of a low-cost fast Fourier transform spectrometer with a delay-line-based ramp-compare ADC implemented on FPGA,"

https://doi.org/10.1093/pasj/psab030

\* L. Leuenberger et al., "An FPGA-based -ENOB MSample/s ADC without any External Components,"

https://doi.org/10.1145/3431920.3439287

高橋さんスライドより