# 計測システム研究会2025@J-PARC

## 汎用的な素粒子原子核実験用ASIC開発の現状

2025/11/17

高エネルギー加速器研究機構

素粒子原子核研究所, ITDC E-sys

量子場計測システム国際拠点(QUP)

宮原 正也

- ・ 近年測定器開発センター(ITDC)エレクトロニクスシステムグループ(E-sys)を中心に開発が進んでいる素粒子原子核実験用ASICの状況について、開発経緯も交えて報告する。

- ASICおよび読出し基板の仕様決め・開発はSPADI-Aを中心に議論が進められている。

- ・ 開発、使用に興味のある方はSPADI-Aにご参加ください。

- ・ <https://www.rcnp.osaka-u.ac.jp/~spadi/>

# 素粒子原子核実験用ASICの開発と応用先

2

※応用先が把握しきれていないかも

| ASIC名    | 機能                                                      | 主な用途                     | 応用実験・分野                                             |

|----------|---------------------------------------------------------|--------------------------|-----------------------------------------------------|

| PP-ASIC  | 32ch, Sub-ns timing control with 40ns dynamic range     | TGC用タイミング補正・タグ付け         | 高輝度LHC(HL-LHC)ATLAS実験のトリガーシステムアップグレード               |

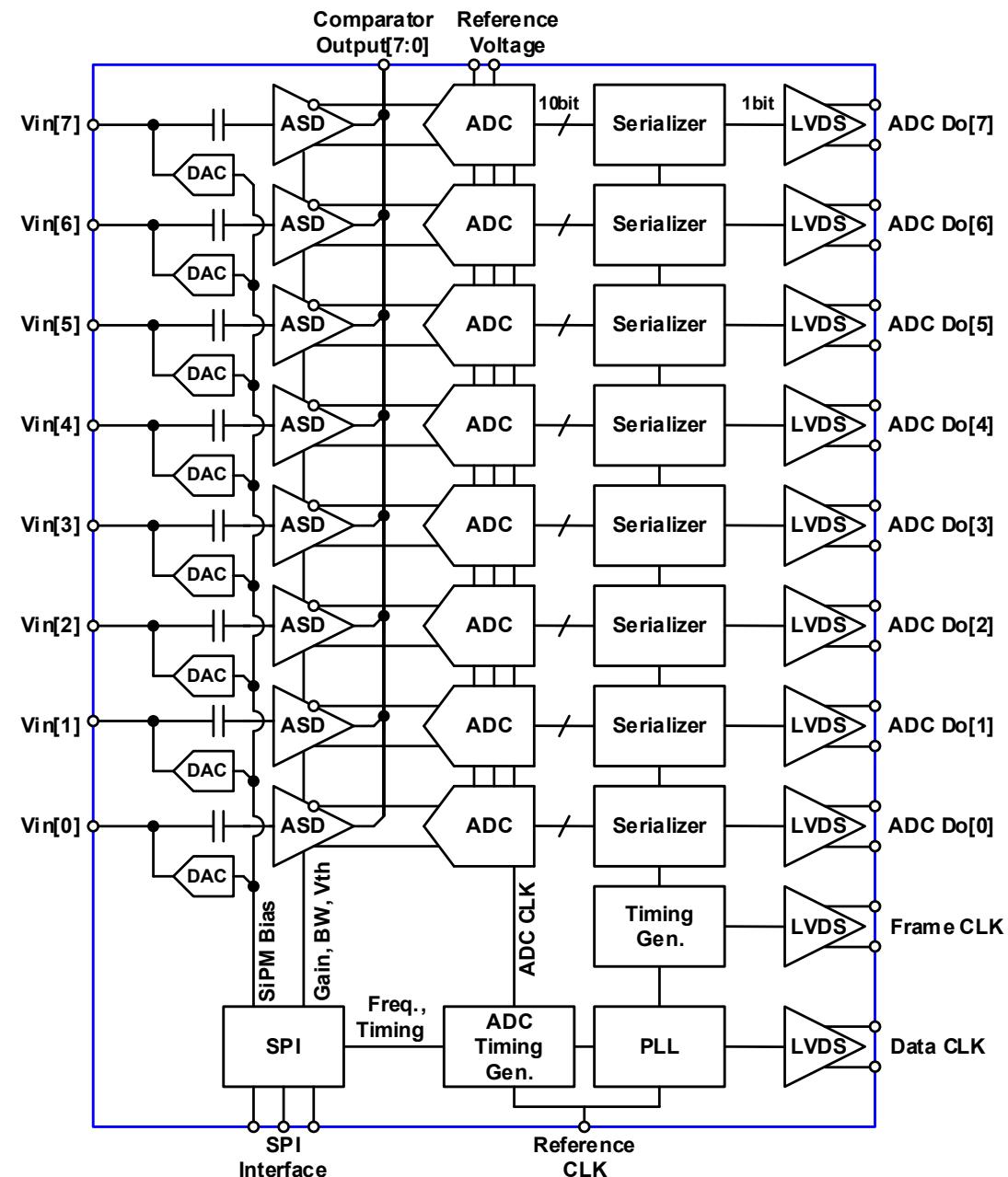

| RAPID    | 8ch, Reconfigurable Amp-shaper-Discriminator+ADC        | ドリフトチェンバー用<br>高速波形読出し    | Belle II(CDC)、AR テストビームライン、新奇半導体検出器(CIGS, GaN)読出しなど |

| YAENAMI  | 8ch, Variable Gain Amplifier +ADC with bias control DAC | SiPM, MPPC汎用<br>高速波形読み出し | T2K、J-PARC NINJA実験、 $\Lambda p$ 散乱実験など              |

| FGATI    | 16ch, BW>1GHz Trans-Impedance Amplifier                 | SiPM, APD用<br>高速信号処理     | TRIUMFのμSI分光実験、山形大学IMONYシステムによる天体観測                 |

| AGASA    | 32/16ch, Reconfigurable ASD                             | ガス検出器用ASD                | J-PARC E50実験、RCNP、理研など                              |

| QPIX_NEO | 64ch, Full-Pixel Continuous ADC Readout                 | ピクセル型検出器用<br>連続波形読出し     | ガス検出器(TPC)、コンプトンカメラ、SMILEプロジェクト、CIGS直接成膜など          |

| SCIBER   | 16ch, ADC with Mid-Range Data Transmission              | SiC読出し用<br>ASD+ADC       | COMET実験用ミューオンビームモニター                                |

# RAPID開発動機

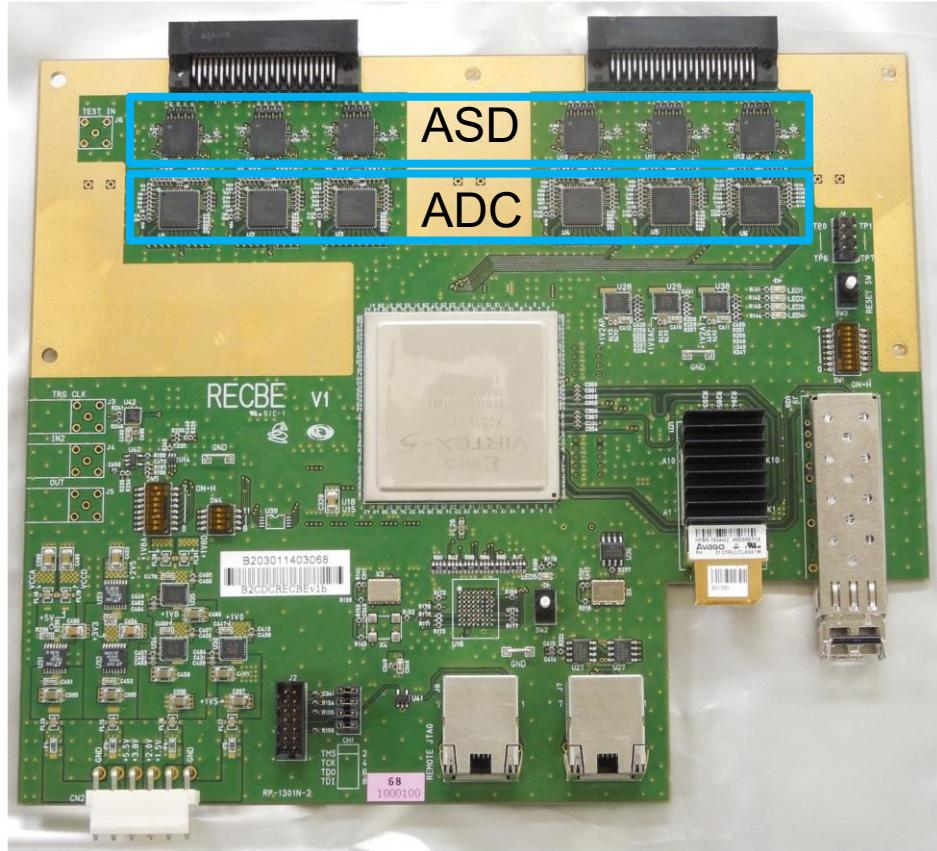

Belle II CDC読み出し用ボード"RECBE"の後継機(-MkII)を開発中

RECBE(現行)

Trigger用光モジュールのTID損傷により

将来取り換えが必要

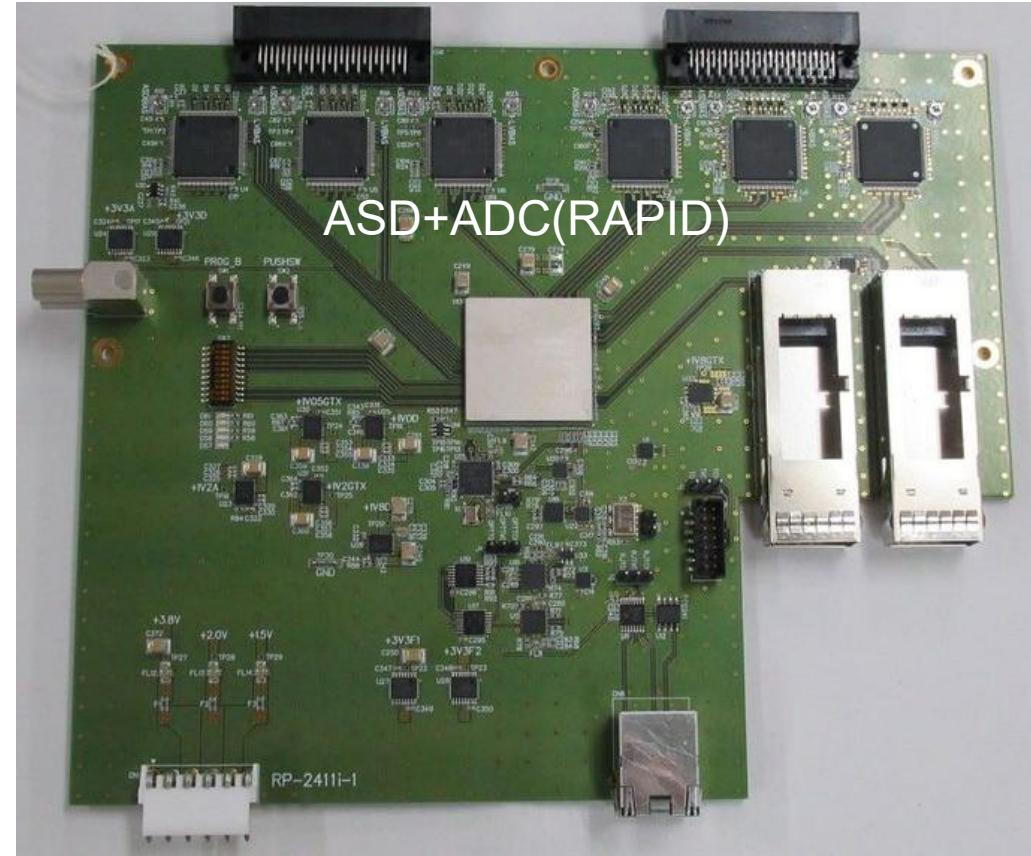

RECBE -MkII

ASD, ADCを1ASICに統合

FPGA高性能化, 光モジュールの再選定

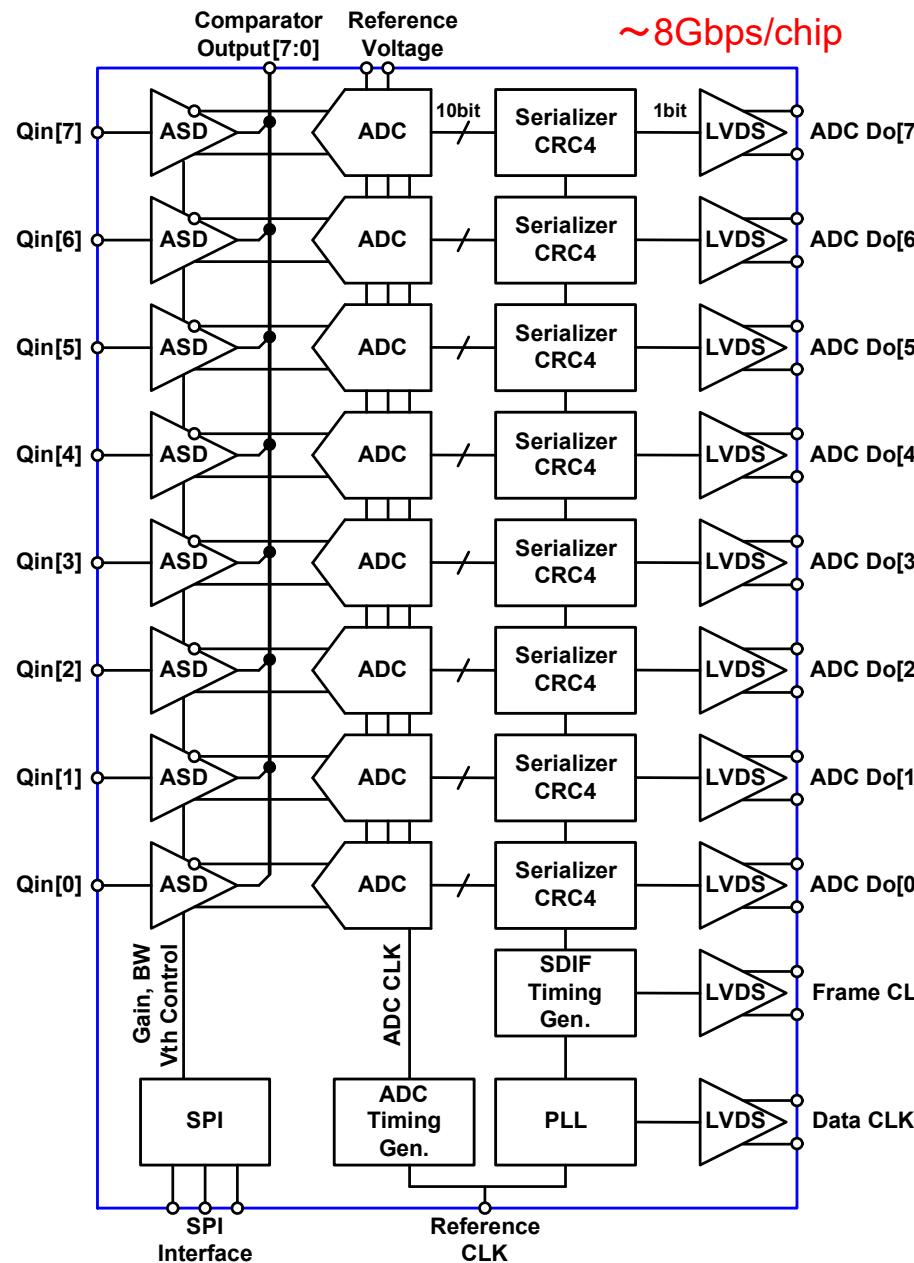

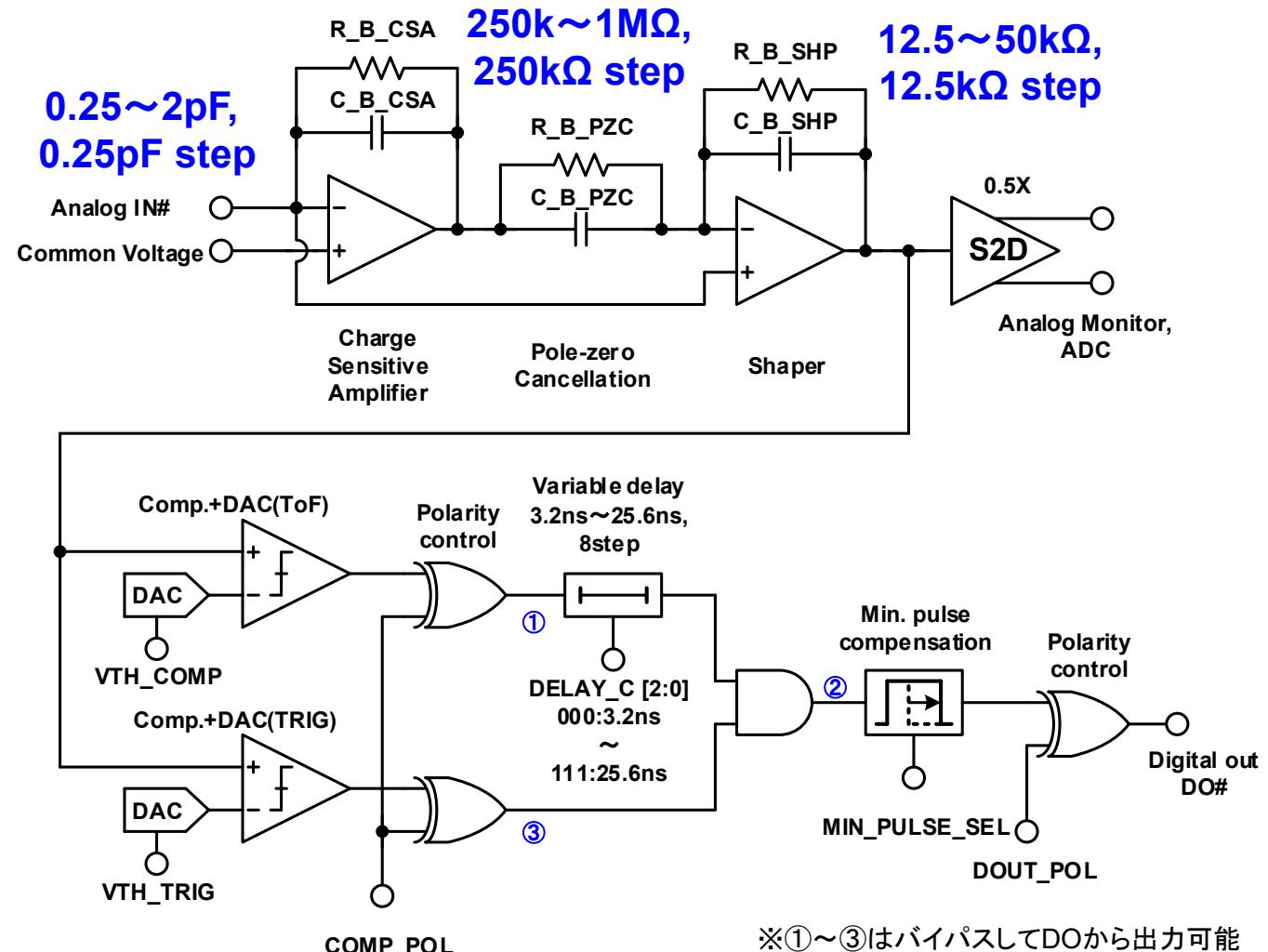

# Reconfigurable ASD-ADC for Particle Detector (RAPID)

4

容量、抵抗値は可変とし、利得及び時定数を

検出器に合わせて最適化することができる。

※①～③はバイパスしてDOから出力可能

# RAPIDの特長

- ASD : クロストークの影響低減

- チャネル毎のしきい値制御 (10bit DAC 2個/ch)

- ダブルスレッシュルド化 (比較器2個/ch)

- アナログクロストーク低減 (1/10以下)

- ADC : サンプリングレート向上

- 現行: 31.75MS/s → 63.5MS/s **2倍向上**

- 消費電力の低減

- 現行 ASD:34mW/ch, ADC:100mW/ch

- ASD+ADC ASIC : 39mW/ch

- **消費電力 1/3.5, 性能約2倍 → 電力効率 7倍**

- 浮いた電力をFPGAのリソースに割り当てられる

- Reconfigurability

- Gain, Peaking time, Dynamic range, Noise

- SPI control

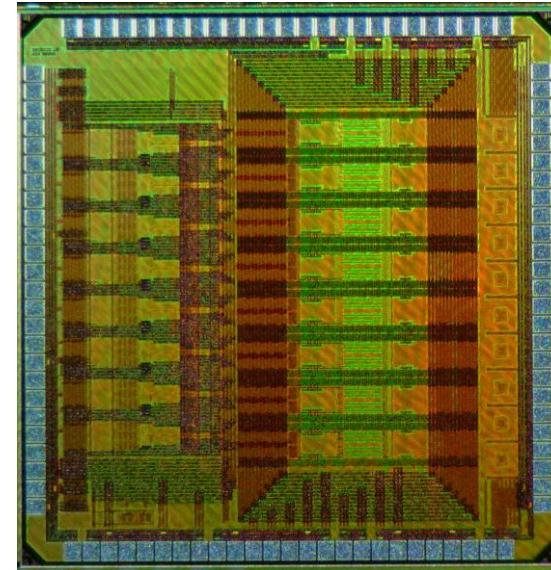

65nm CMOS process, 4mm<sup>2</sup>

Belle II CDC, センスワイヤ 14,336本

# RAPIDの開発状況

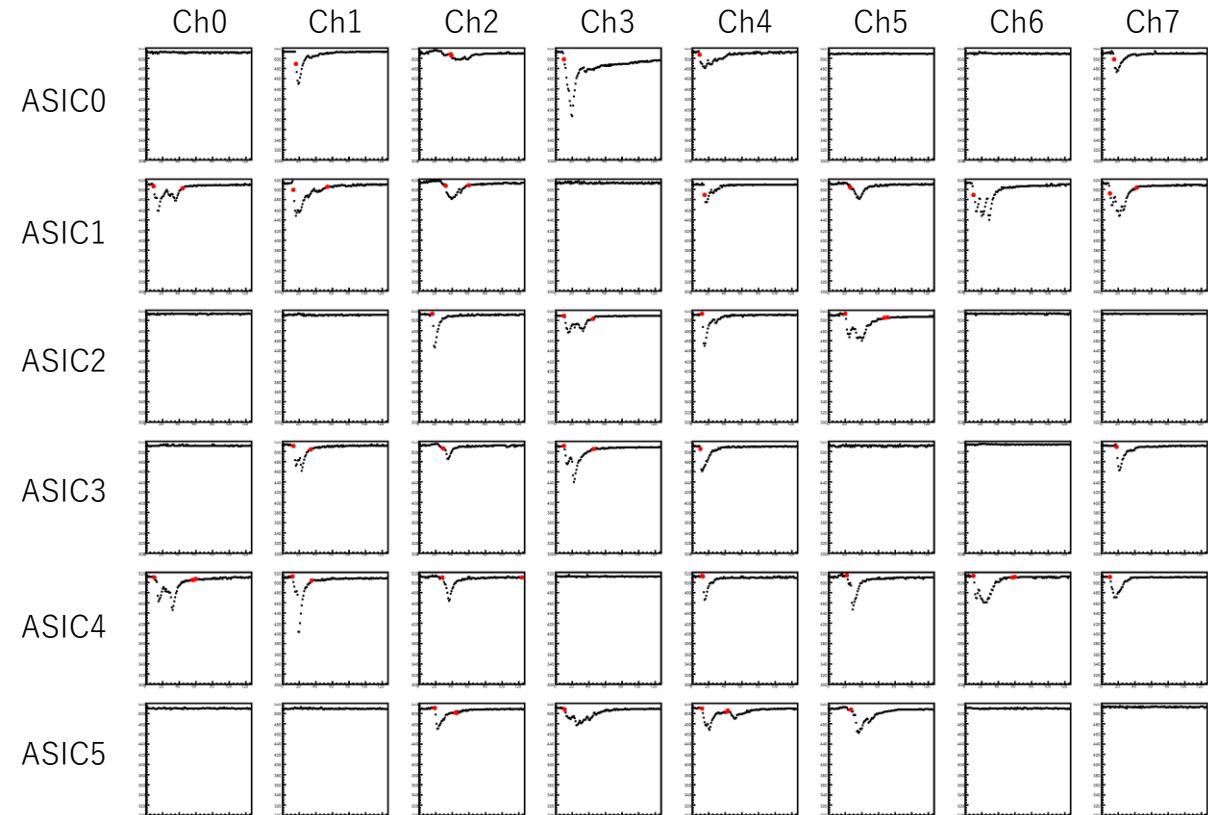

- ASIC単体動作、RECBE-MkIIの評価を完了 仕様を概ね満たすことを確認

- 2023年度末に3,000チップ(24,000チャネル相当)を量産

- Belle II CDCグループと協力しASICの品質チェック環境を構築中

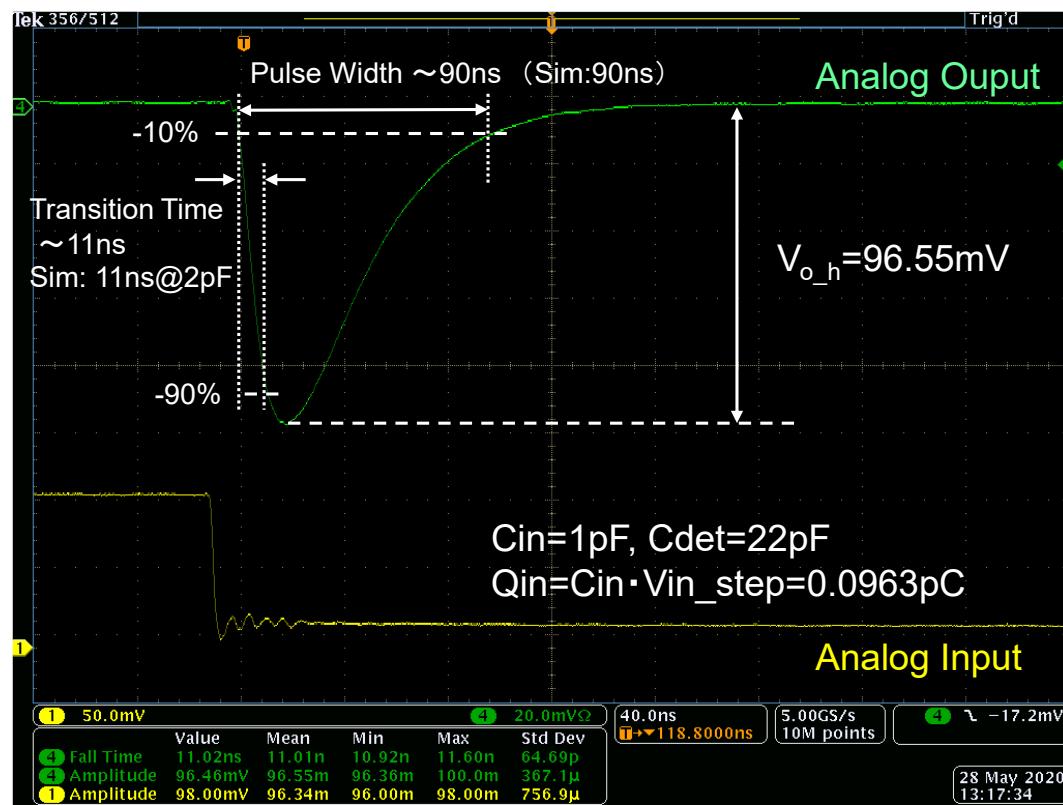

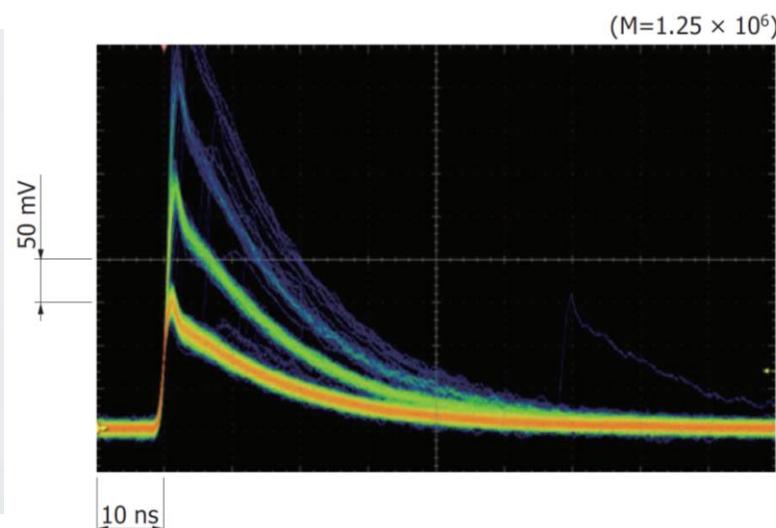

ASIC単体評価におけるアナログ波形

RECBE MkIIによるADC波形読出し(48ch)

# RAPIDの技術・応用展開

J-PARCハドロン実験その他数多くの実験に使用(予定)

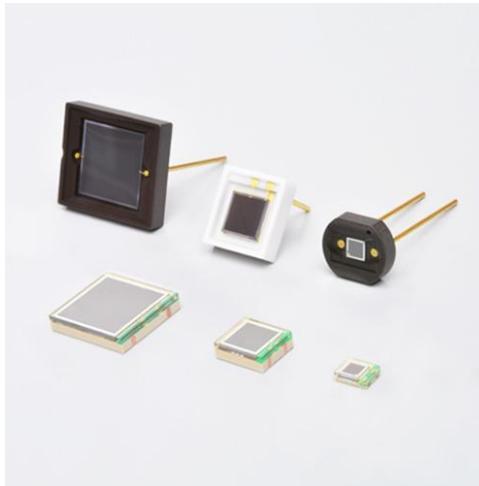

SiPM(光検出器)

汎用読み出し

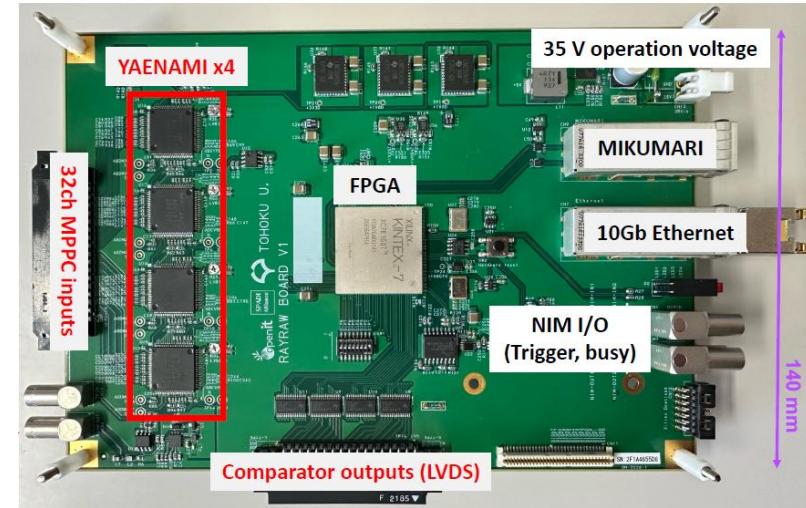

YAENAMI

RAPID

8ch VGA+ADC,

SiPM(MPPC)利得調整用DAC付き

32ch Amp-Shaper-Discriminator

ゲイン、時定数調整可

ガス検出器

汎用読み出し

SPADI-Aによる読み出し基板

YAENAMIを利用したRAYRAWボード

AGASAを利用したASAGIカード

# 残されている課題

- **YAENAMI**

- 大電荷入力時に大きなアンダーシュートが生じる

- デジタルの出力が狭パルスで出力されノイズをまき散らす

- これまでの開発経緯は

<https://openit.kek.jp/workshop/2024/dsys/presentation/miyahara.pdf>

- **AGASA**

- デジタル出力がアナログ回路に回り込み、高利得設定時に発振

- 偶数、奇数チャネルでデジタル出力の極性を反転させてしのいでいる

これらの課題への対応状況について報告する

# YAENAMIの概略

- RAPIDを改造しMPPC読出しに特化

- MPPC利得調整用DAC追加

- CSA→VGA化(大電荷対応、利得、BW可変)

- RAPIDとピンコンパチ

- (ほぼ)同じ回路基板、ファームウェア利用可能

- 詳細はRAYRAW user guide参照のこと

- [RAYRAW User Guide](#)

- [YAENAMI.pdf](#)

[MPPC \(Multi-Pixel Photon Counter\) S13360シリーズ](#)

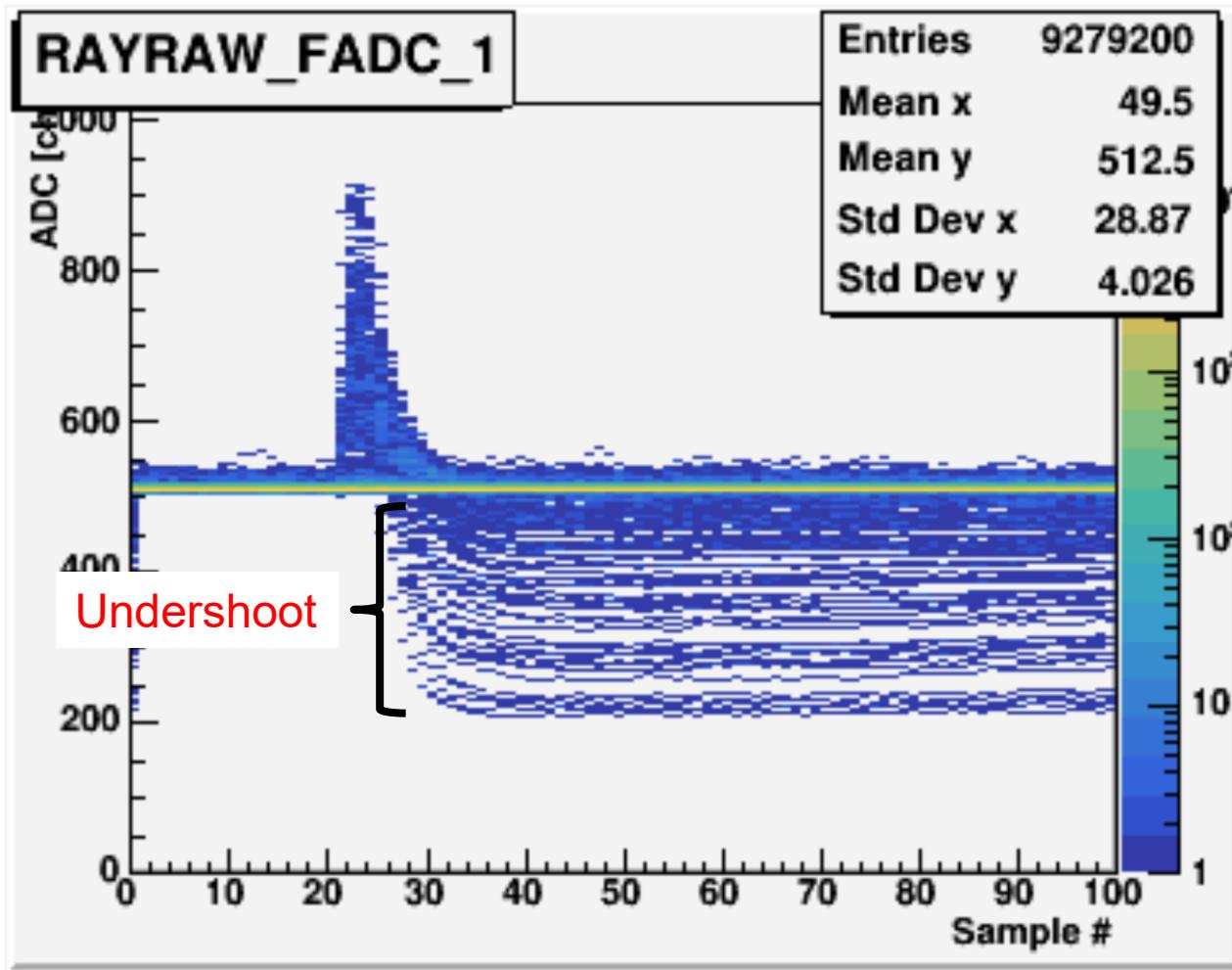

# アンダーシュート問題

10

出典: 倉田, YAENAMI-RAYRAW TFミーティング資料

最大利得設定かつ大電荷入力時に

数～数十μsに渡りアンダーシュートが発生

→高入力レートアプリケーションには不向き

ファイバー検出器の宇宙線によるテスト

1sample = 13.3ns

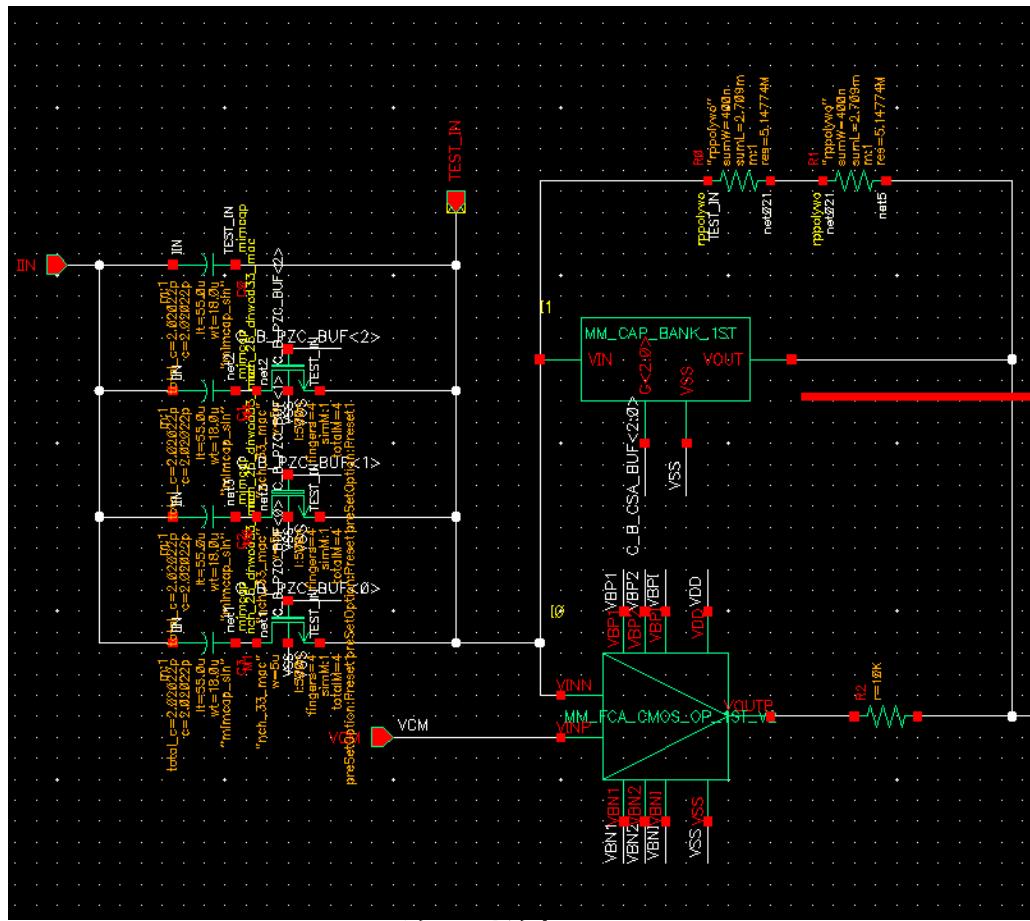

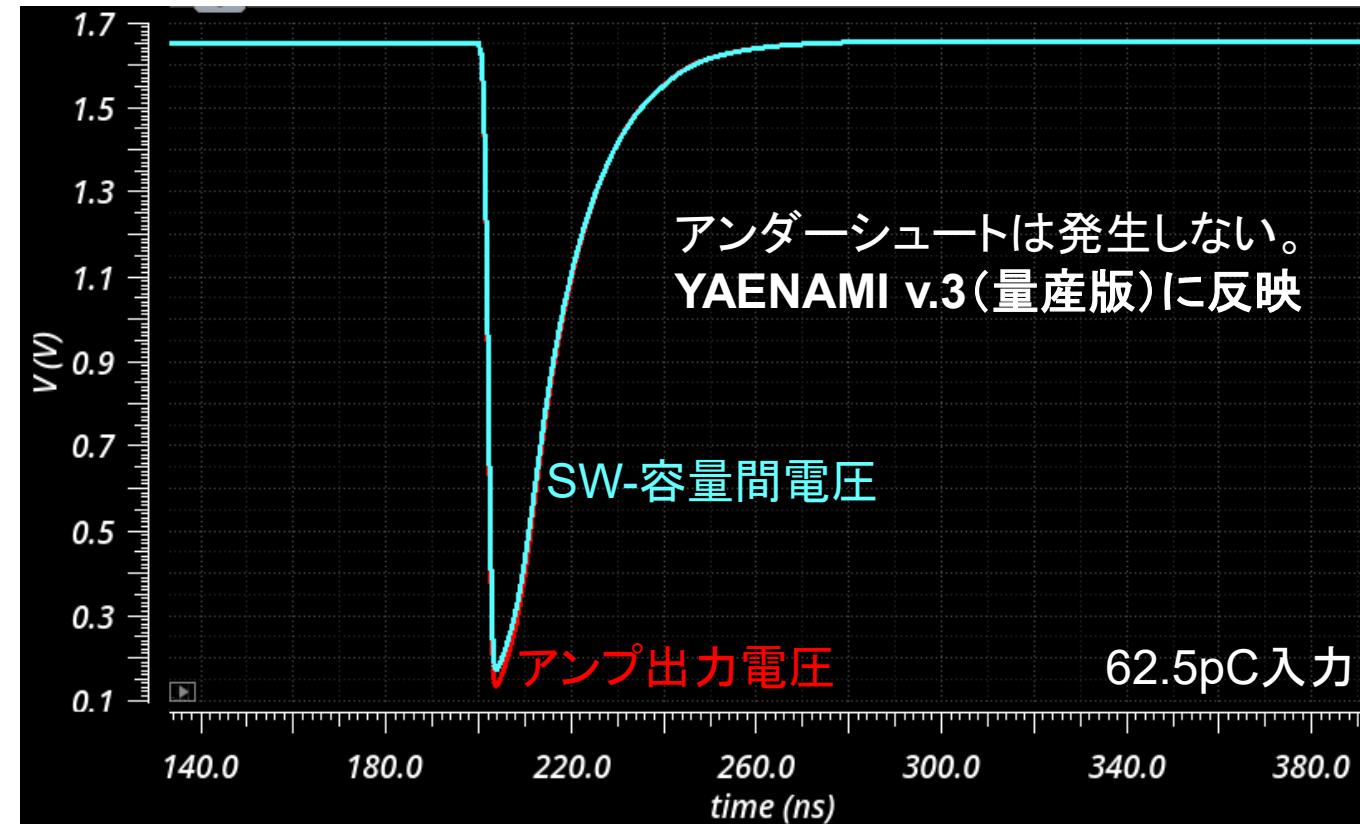

# アンダーシュートの発生原因

11

- 利得切り替え用のスイッチ+容量回路でフローティングノードが発生

- 大電荷入力時にフローティングノードが負電圧まで振れ、OFF状態のスイッチがON状態に反転→VGAのフィードバックループ内で電荷が注入されアンダーシュート発生

前置増幅器

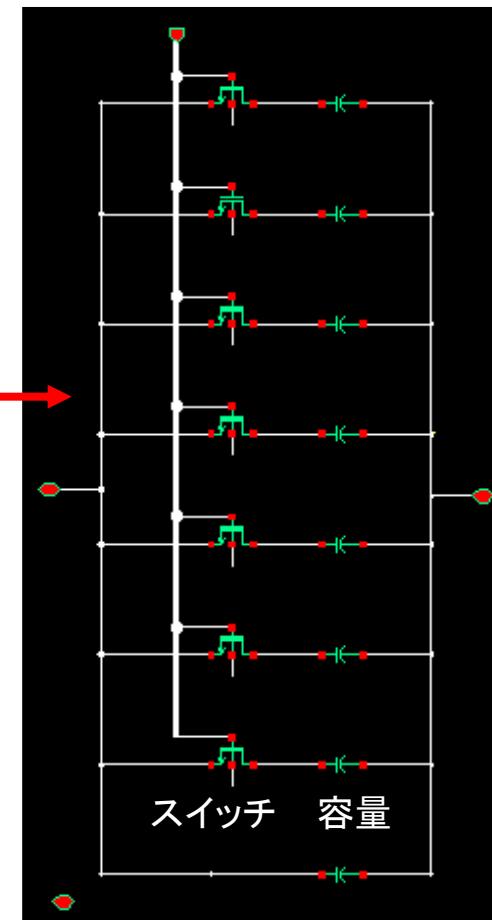

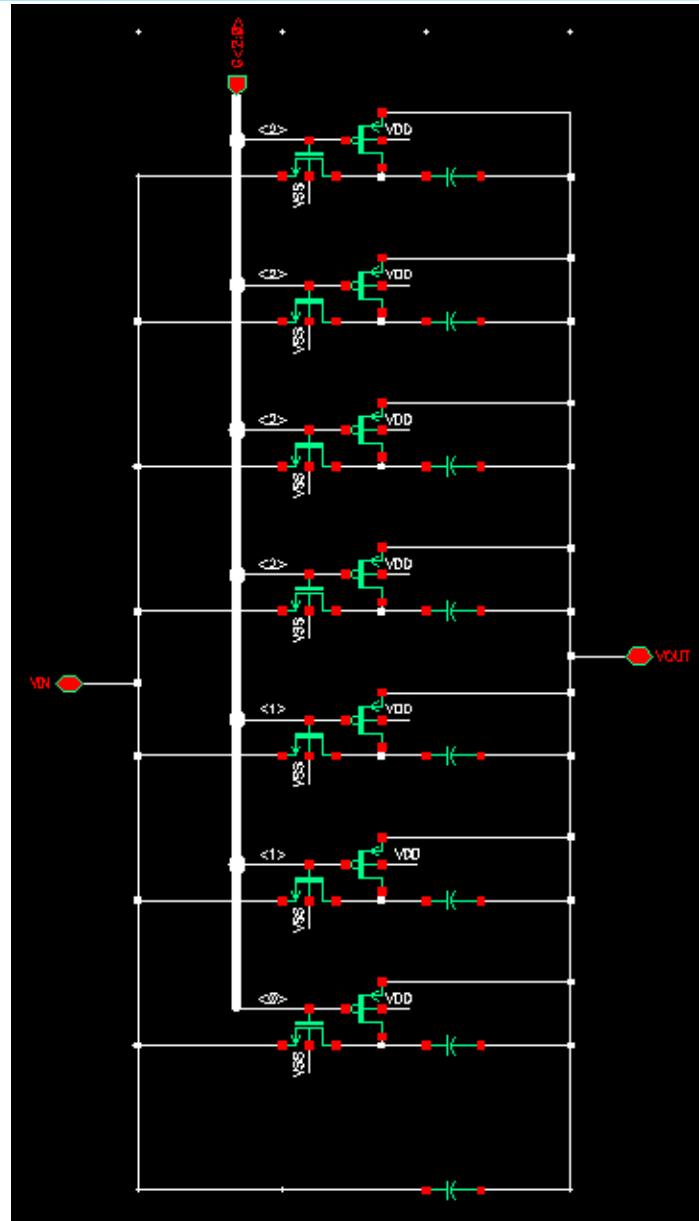

# アンダーシュート修正案

可変容量バンクの修正案

- PMOSスイッチを追加して容量OFF時に容量ノード間をショートする

- NMOSスイッチ-容量間にフローティングを作らない

- OFFになっている容量にチャージを蓄えない

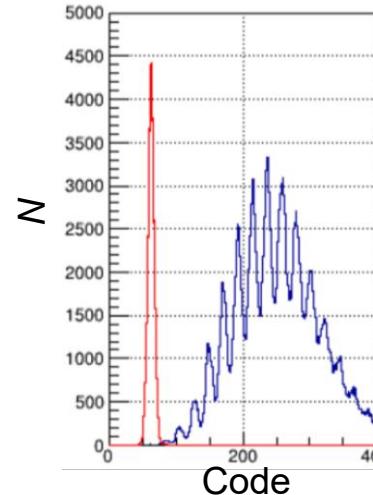

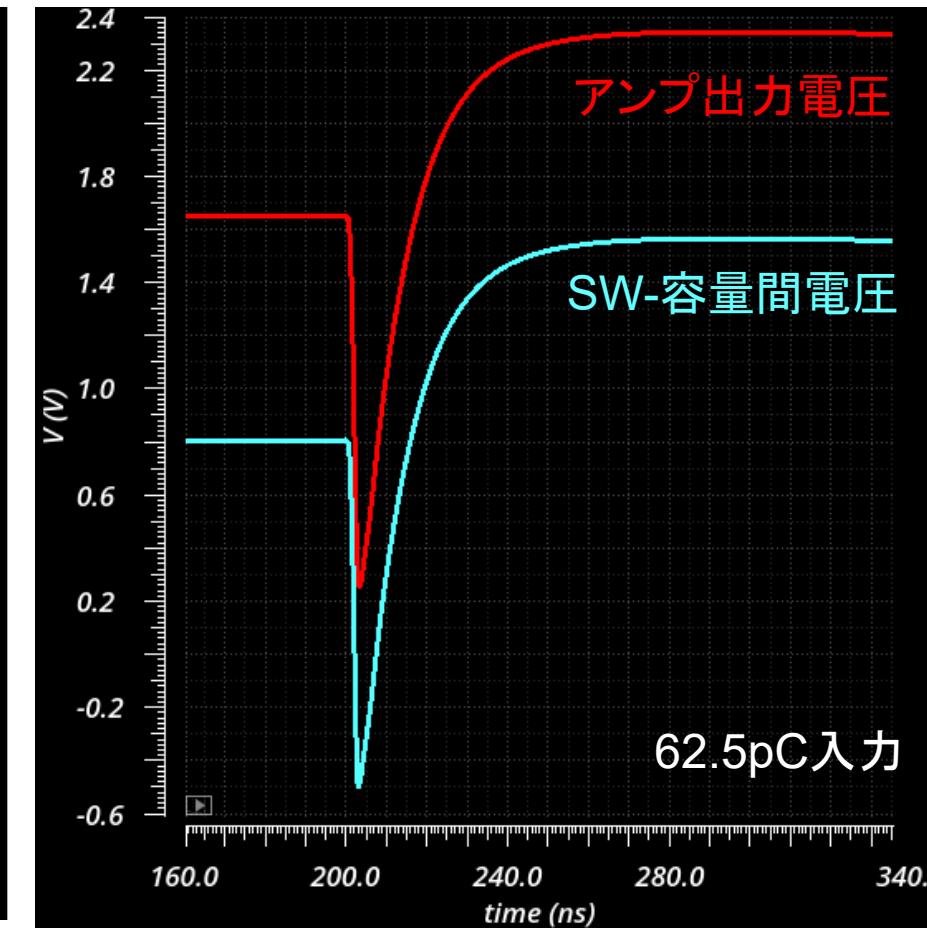

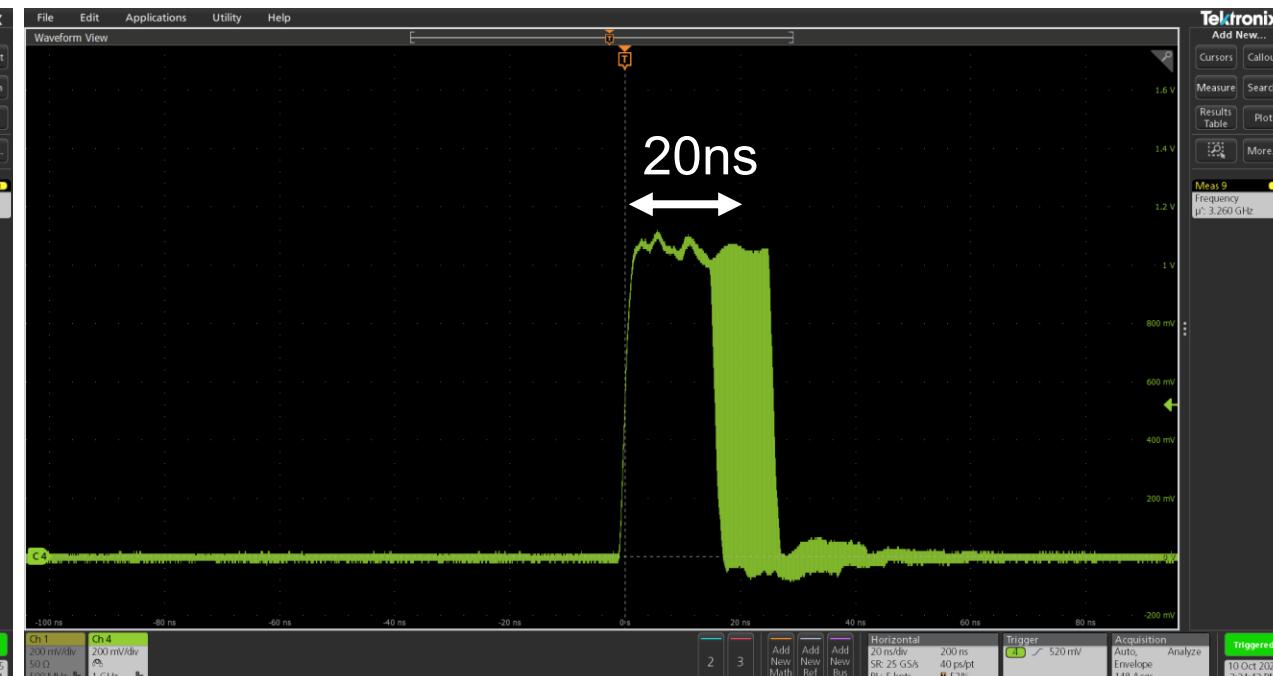

# YAENAMI v.3の評価結果

- YAENAMI v.2(修正前), v.3(修正後)に50pCの電荷を入力

- v.2, v.3共に電圧利得は最大設定にしてアナログ出力(+)を観測

- YAENAMI v.3ではアンダーシュートを大幅に抑制可能

- 軽微なアンダーシュートはアンプの飽和動作によるもので避けられない

YAENAMI v.2のアナログ応答波形

YAENAMI v.3のアナログ応答波形

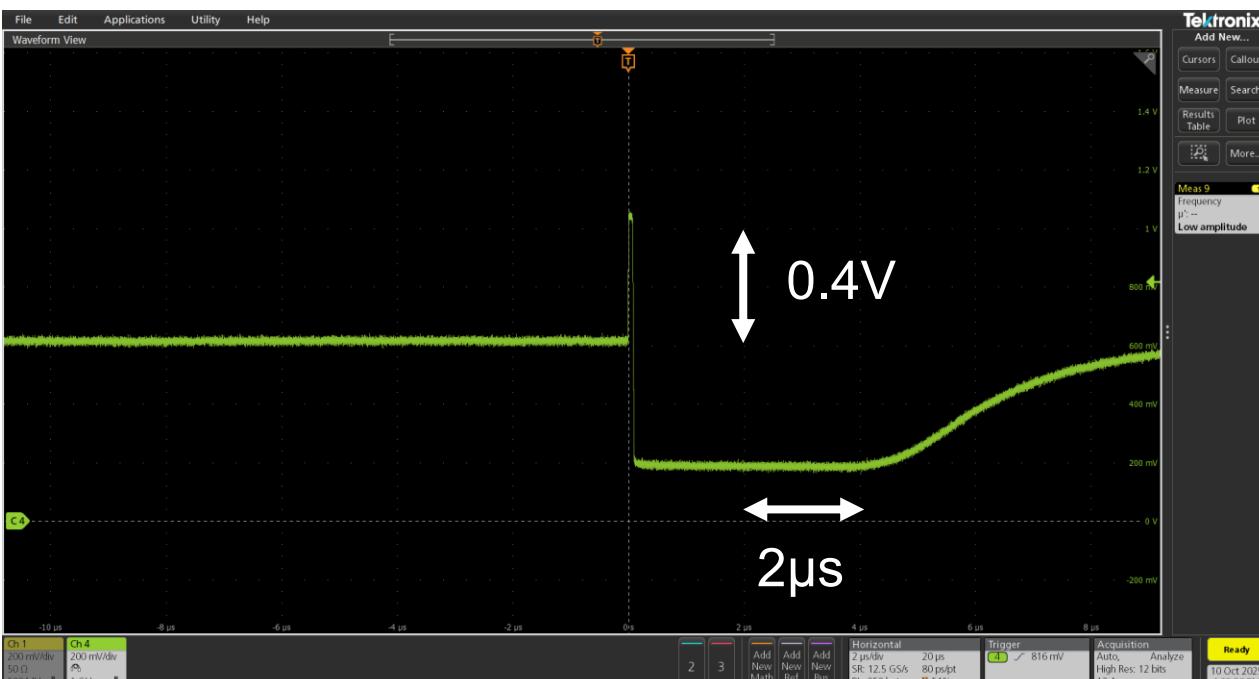

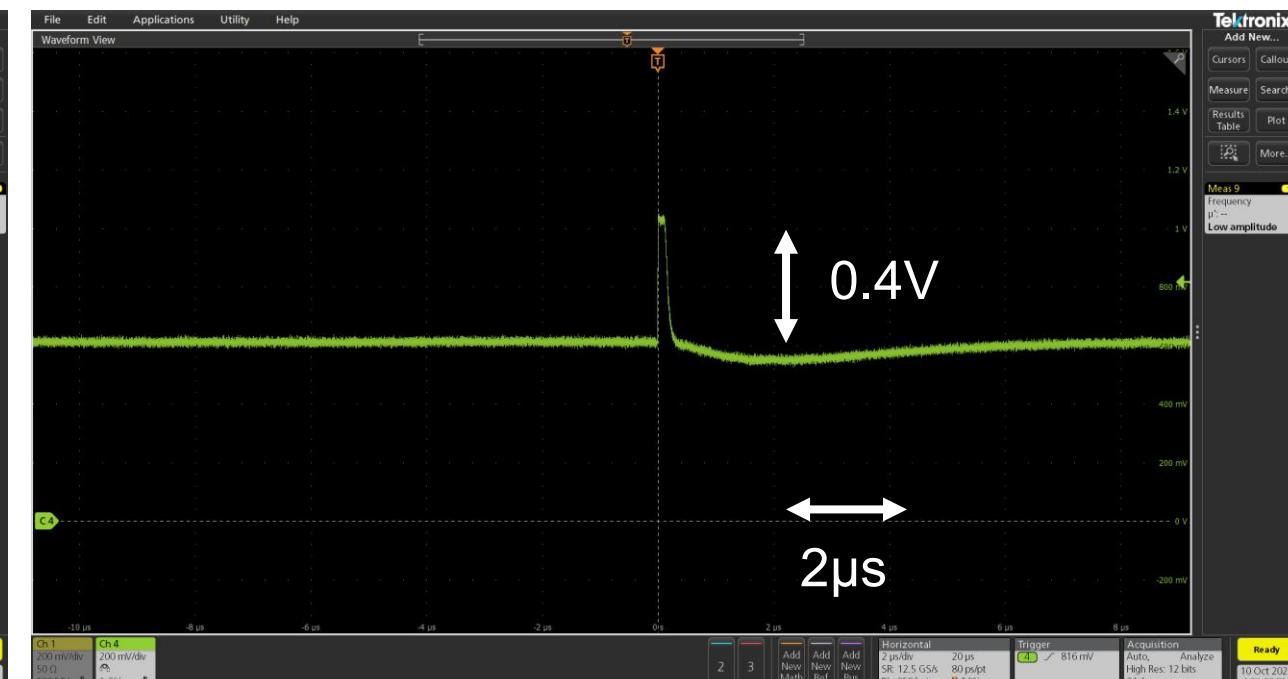

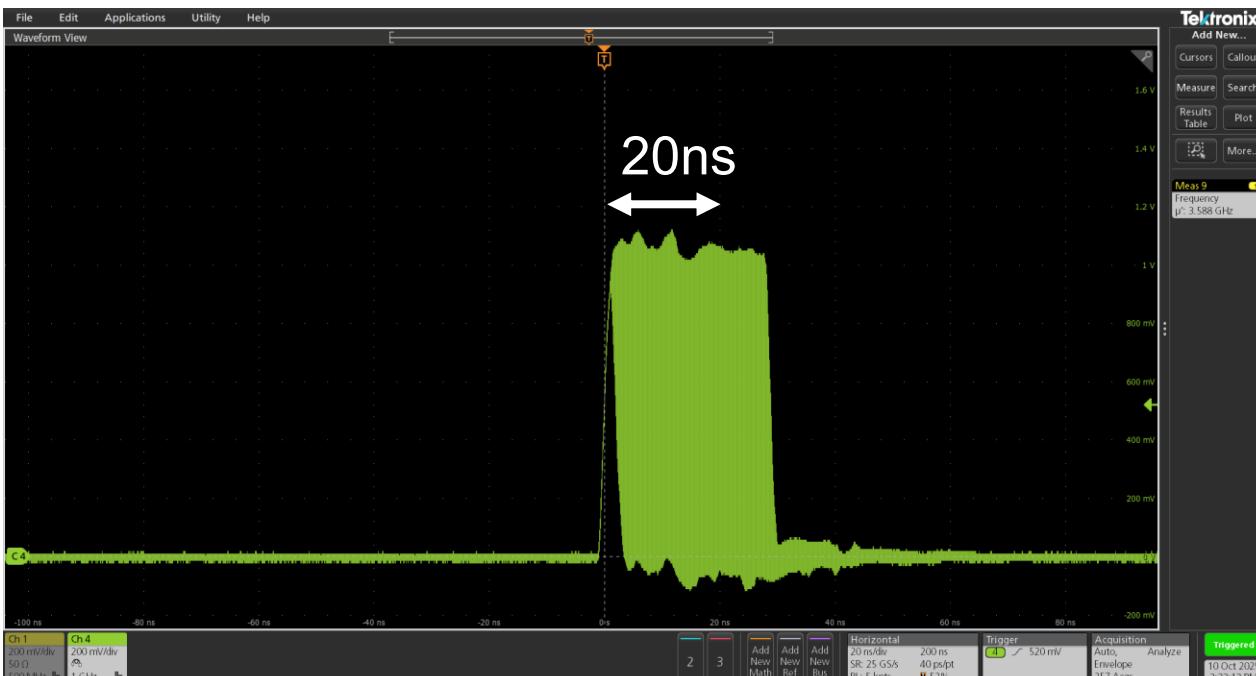

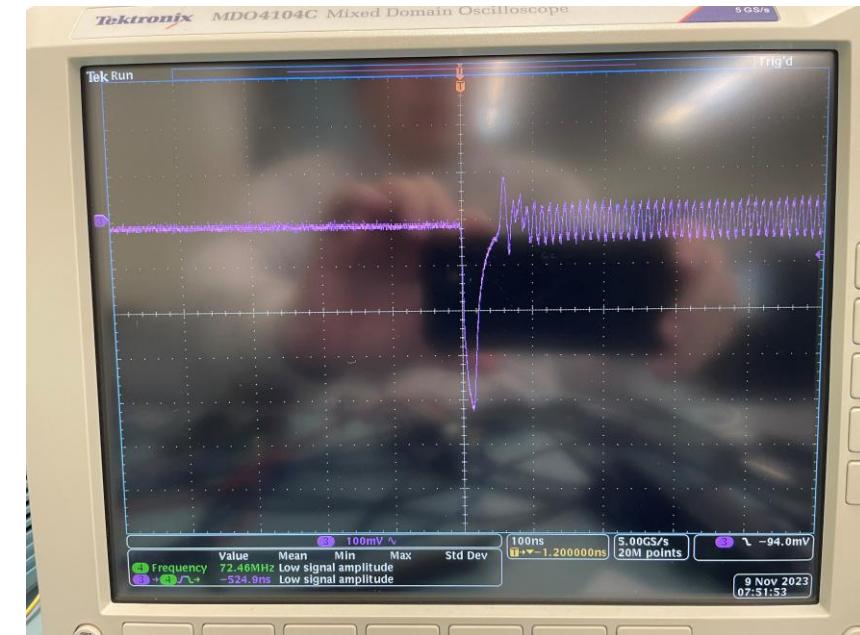

# 最小パルス幅補償

- VGAを最大利得に設定し、比較器のしきい値をVGAの最大波高値近辺に設定

- 狭パルス(<2ns)のデジタル出力が生じ、高周波数ノイズを出す

- アナログ回路が影響を受けノイズ特性が悪化

- 最小パルス幅補償を用いることで一定以下のパルス幅とならないようにできる

最小パルス幅補償OFF時のデジタル出力

最小パルス幅補償ON時のデジタル出力

# YAENAMI v.3の修正点と測定結果

| 問題点                         | 修正内容                              | 測定結果                     | 判定   |

|-----------------------------|-----------------------------------|--------------------------|------|

| 大電荷入力時にアンダーシュートが生じる         | 容量バンクにてフローティングノードが生じないようにスイッチを修正  | 50pC入力に対してアンダーシュート抑制を確認  | ✗→○  |

| ADCの非線形性に起因した疑似ピークが見える      | PRBSを用いたエラー拡散技術を取り入れた(DEM)        | 疑似ピークの消失を確認              | ○    |

| ADCのデータレートが低い (~75MS/s)     | シリアルライザをカスタム設計に切り替え高速化した          | 100MS/sで安定動作             | ○    |

| アナログテストパルスの信号入力量が適切ではない(飽和) | 入力端を適切に修正し入力電荷量を4~5p.e.に調整した      | 想定通りの波形、飽和なし             | ○    |

| デジタル出力のテストパターンが未実装          | 0b1001100011のみを出力するモードを設けた        | 全チャネル想定通りの出力を確認          | ○    |

| デジタルの出力が狭パルスで出力されノイズをまき散らす  | 最小パルス幅補償回路を実装し1~10ns程度に調整できるようにした | 想定通り動作                   | ✗→○  |

| デジタルの出力がSPIの信号入力に干渉する       | デジタルの出力とSPIの入力I/Oの電源を分けた          | 最悪条件でのエラー確率<br>90%→1%に低減 | △→○? |

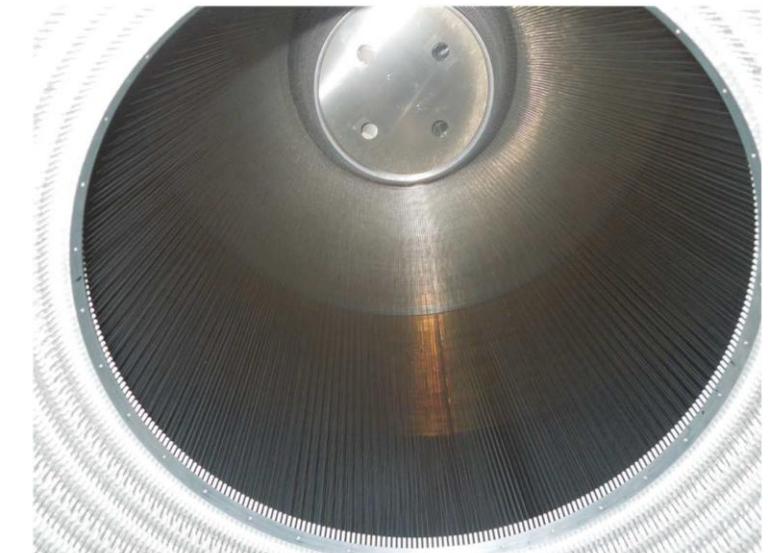

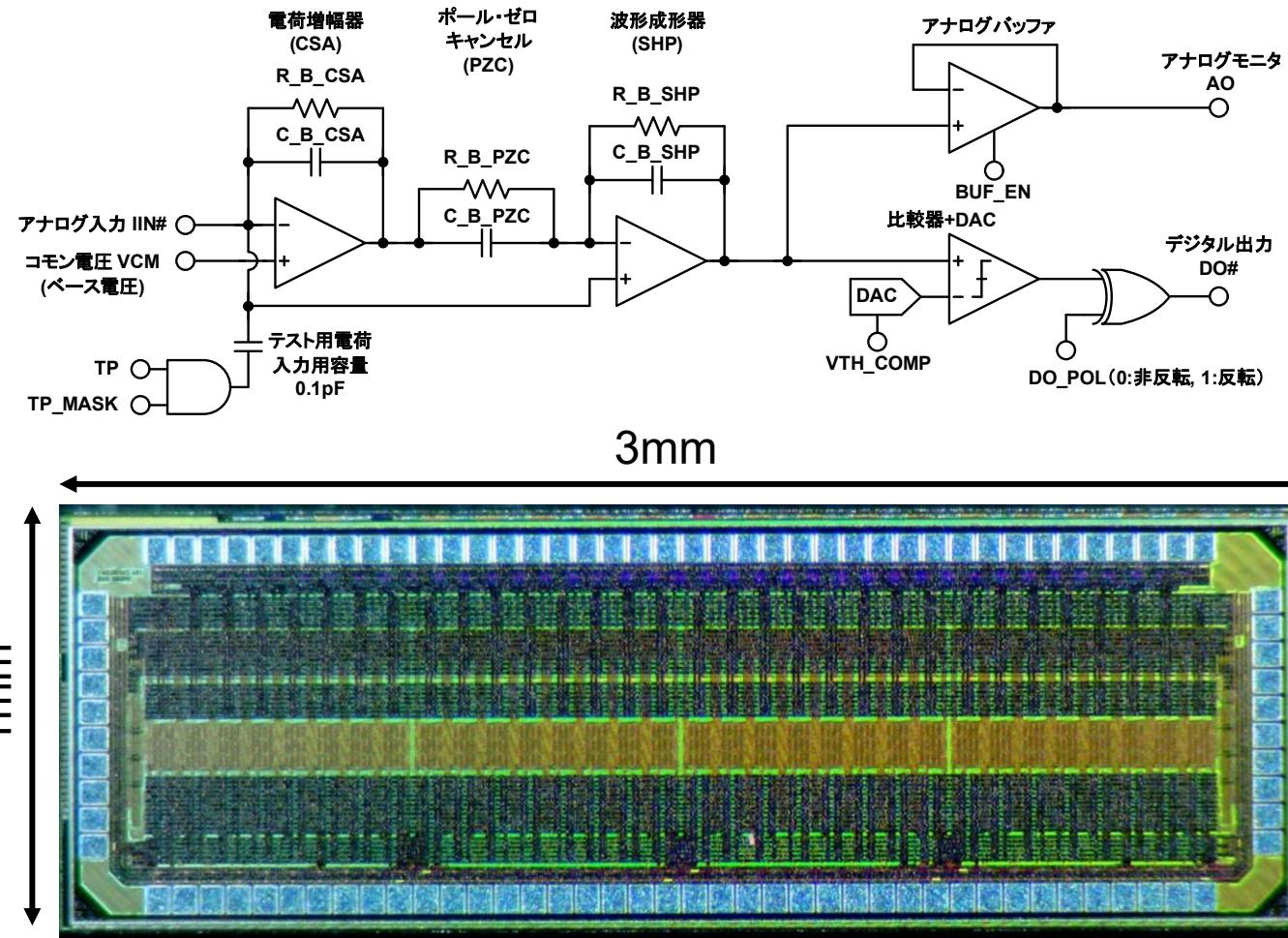

# ガスチャンバー向けASIC : AGASA

RAPIDのASDを改造し多チャンネル読出し化

応用先: J-PARC E50実験 CDC読出し その他

- SPADIAで読出し基板(ASAGI)を作成、普及

- $65\text{nm} \Rightarrow 180\text{nm CMOS}$  プロセスに変更中

# AGASAの開発変遷

- **AGASA v1.0**

- 32ch AGASA

- デジタル出力がアナログ入力に回り込み発振しやすい

- パッケージが大きく(P-QFP160)、電源、グランドが弱い

- SPIのレジスタのデータが飛ぶ

- **AGASA v1.5**

- 32ch AGASAを16ch分だけ使用

- パッケージをLQFP100に変更しボンディング長を低減

- ASICレベルでの電源、グランドの強化

- SPIのレジスタデータ飛びは抑制

- 発振は止められなかった

- チップサイズが小さくアナログとデジタルのワイヤが近い→電磁結合しているっぽい

- デジタルがシングル出力のためノイズを出しやすい

- 偶奇でデジタル出力の極性を反転させると発振を抑制できる→差動化が有効

- **AGASA v2.0**

- AGASA v1.5の設計に基づきASIC自体を16ch化したもの

- 構成はAGASA v1.5と変わらない→v1.5で起きる問題は同様に起きる

- SAPDI-AのSTAGボードはこれを使用

- ・ デジタル出力の回り込みを抑制するためにLVC MOSからLVDS出力に変更

- ・ 許容入力電荷量を2倍、時定数を1/2に変更

- CSAの容量を2倍、抵抗値を1/2に変更

- ・ 生産コスト抑制のため65nm→180nmにプロセスポートイング

- 65nmで開発したときにもアナログ回路はIO(350nmプロセス相当)のトランジスタを使用していた

- ・ SPI通信(3線)を1線で行えるようにするためのプロトコルコンバータIC(ONESPI8)もセットで開発

- 1線で8個のデバイスを制御可能

- 市販のデバイスにも使える(はず)

- ・ 2025年度内にASIC単体評価は終える予定

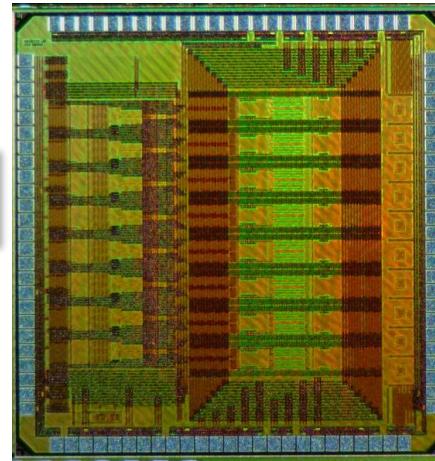

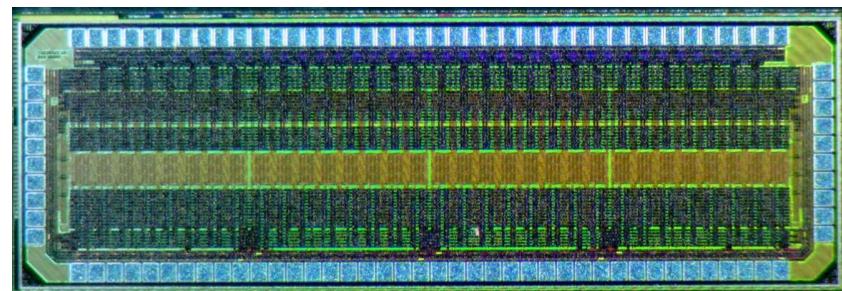

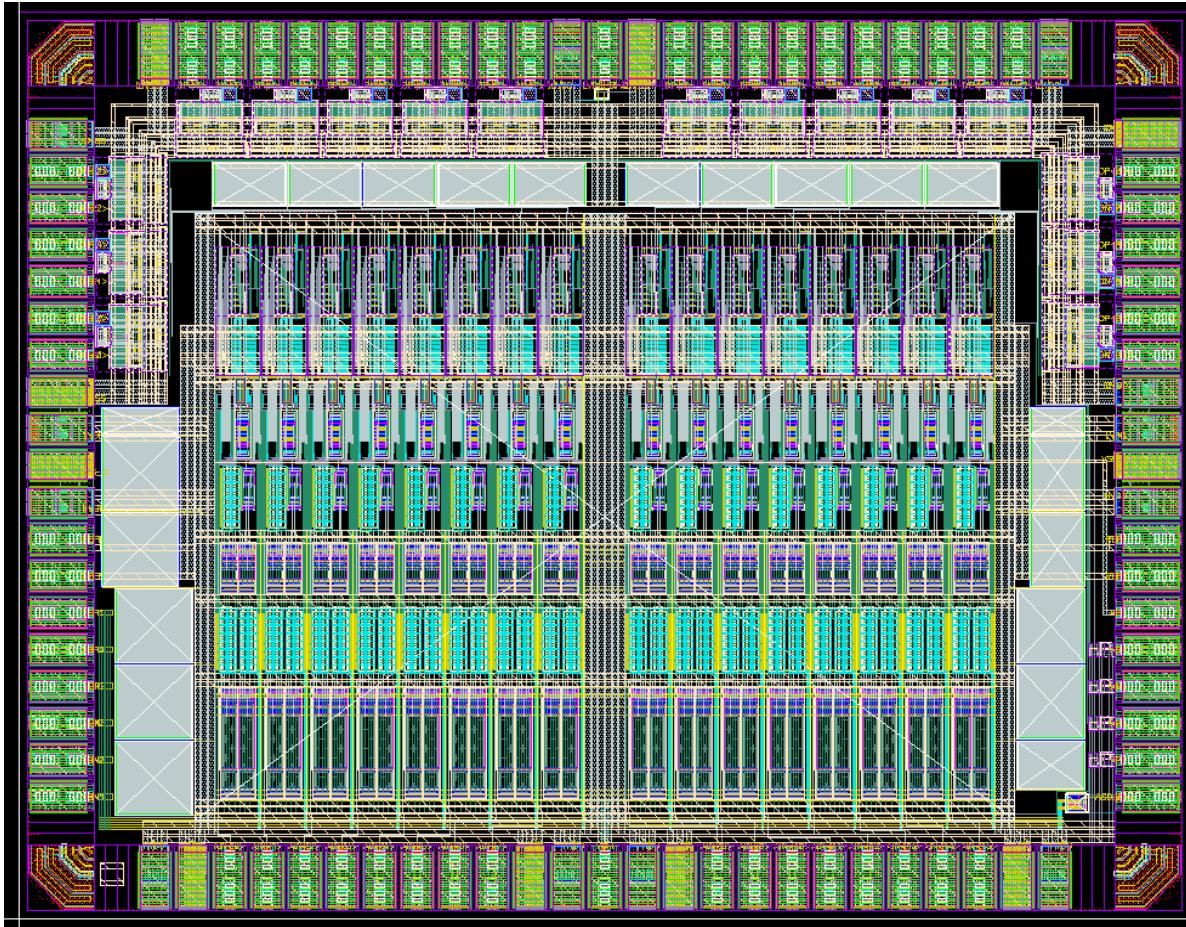

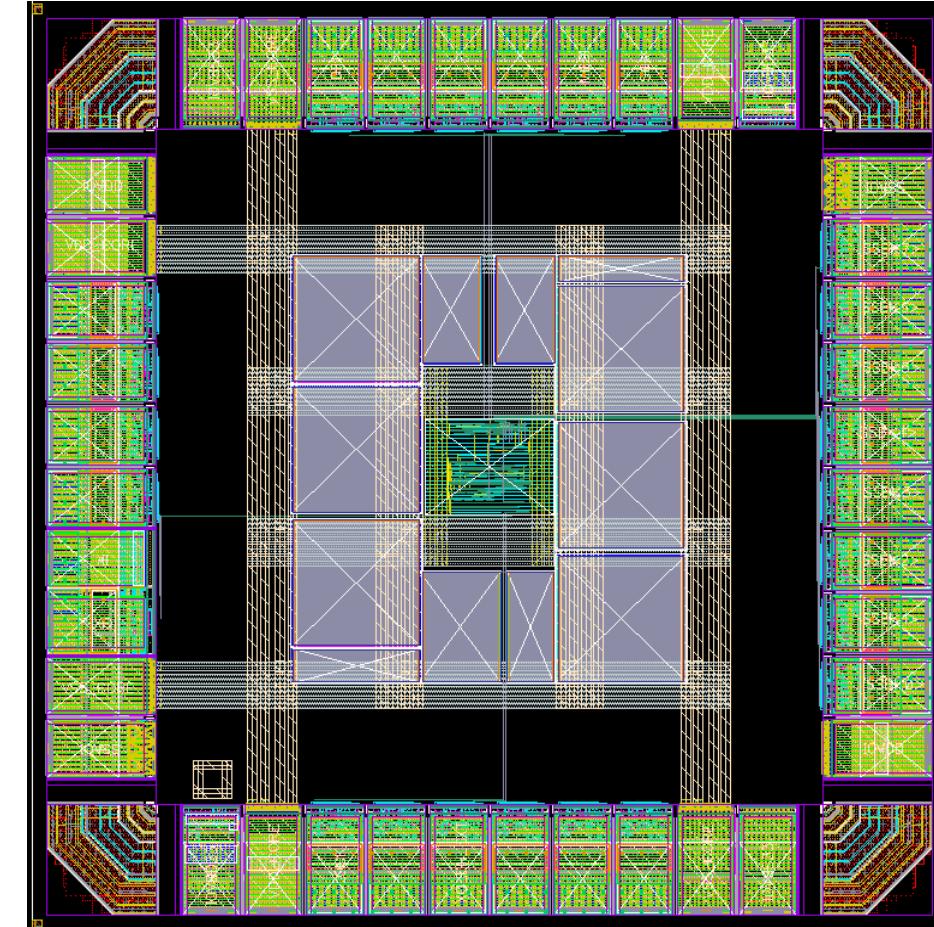

# AGASA v3.0のレイアウト

19

11/25 パッケージ(LQFP100)完了予定

16ch, LVDS出力 AGASA v3.0

11/19 チップ納品予定

1:8 SPI通信用ASIC ONE SPI8

- **YAENAMI v3**

- アンダーシュート問題への対応、最小パルス幅補償回路の効果が確認され、量産版として完成

- 900チップ量産済み QCが課題

- **AGASA v3.0**

- デジタル出力がアナログ入力に回り込むことによる発振が課題

- デジタル出力をLVDS化することによりデジタルノイズを抑制

- ダイナミックレンジを2倍に(v1.0, 1.5比較)

- 量産コストを抑えるために180nmにプロセスポーティング

- 年度内にASIC単体評価を終える見込み

- **ASICの量産版までに3回製作が必要**

- 1次試作：まずは動くもの。システム評価による課題洗出し。

- 2次試作：1次試作での課題が解決できたかの確認用。

- 3次試作(量産)：ほとんどの課題が洗い出されて安定的に動くもの

- 継続的な開発が必要なため、引き続きご協力お願いします**

本研究は、JST経済安全保障重要技術育成プログラム【JPMJKP24J2】の支援を受けたものです。