# COMET Phase-I

## CyDet トリガーシステムの開発状況

---

大阪大学 山田 千尋

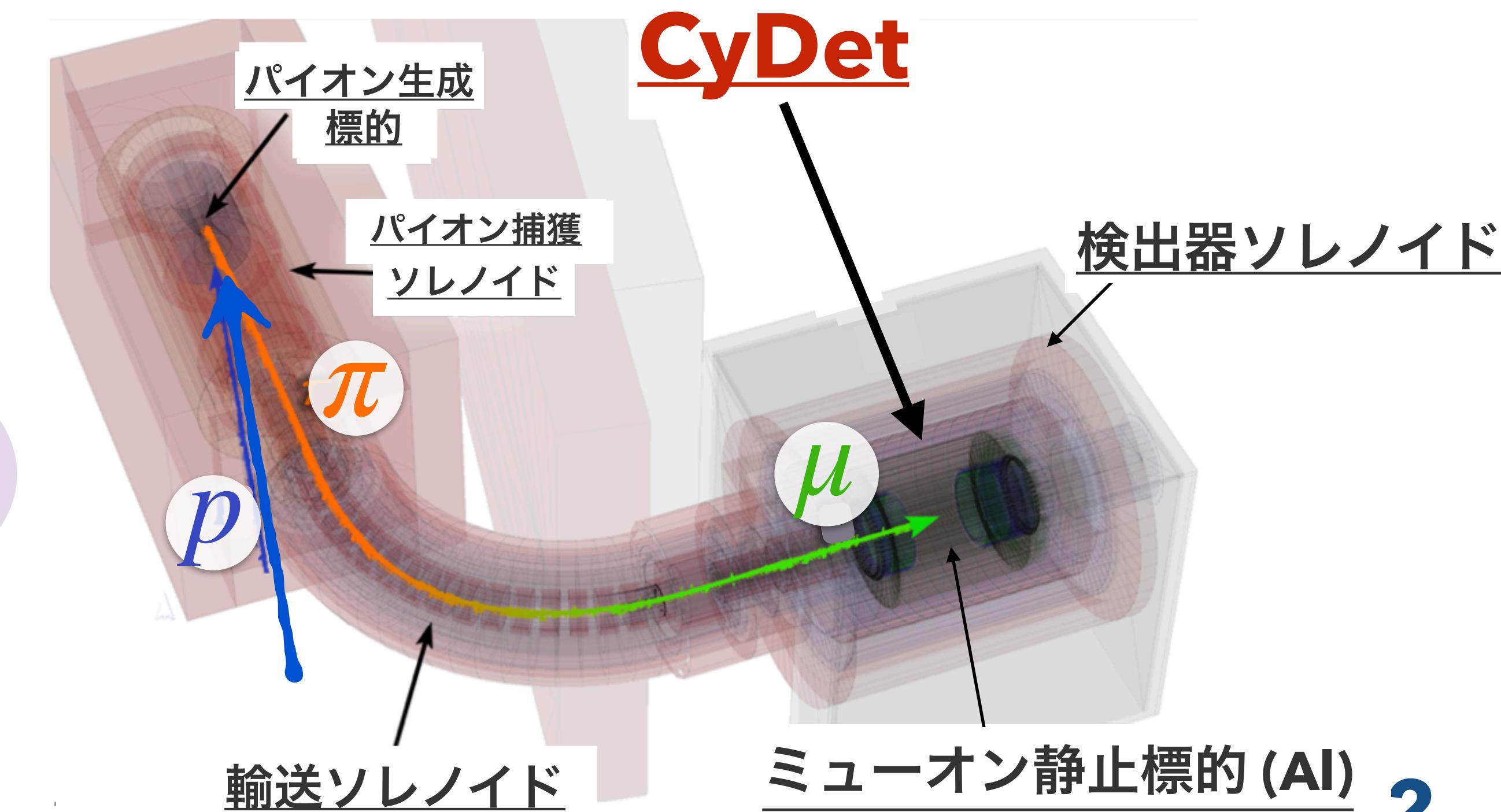

# COMET Phase-I @ J-PARC, Japan

## Al 原子核中の $\mu - e$ 転換探索実験 ... 荷電レプトンフレーバー非保存過程

- ニュートリノ振動を含めた標準模型での分岐比 ...  $\mathcal{B}(\mu^-N \rightarrow e^-N) < O(10^{-57})$

- 新物理 (SUSY-GUT, Z', etc..) ...  $\mathcal{B}(\mu^-N \rightarrow e^-N) \sim 10^{-15} - 10^{-13}$

- 目標単一事象感度:**  $3 \times 10^{-15}$  (測定期間: 150日)

- 現在の上限値 w/ Au  $\mathcal{B}(\mu^-Au \rightarrow e^-Au) = 7 \times 10^{-13}$  90% C.L. (SINDRUM II) Eur. Phys. J. C47, pp.337–346 (2006).

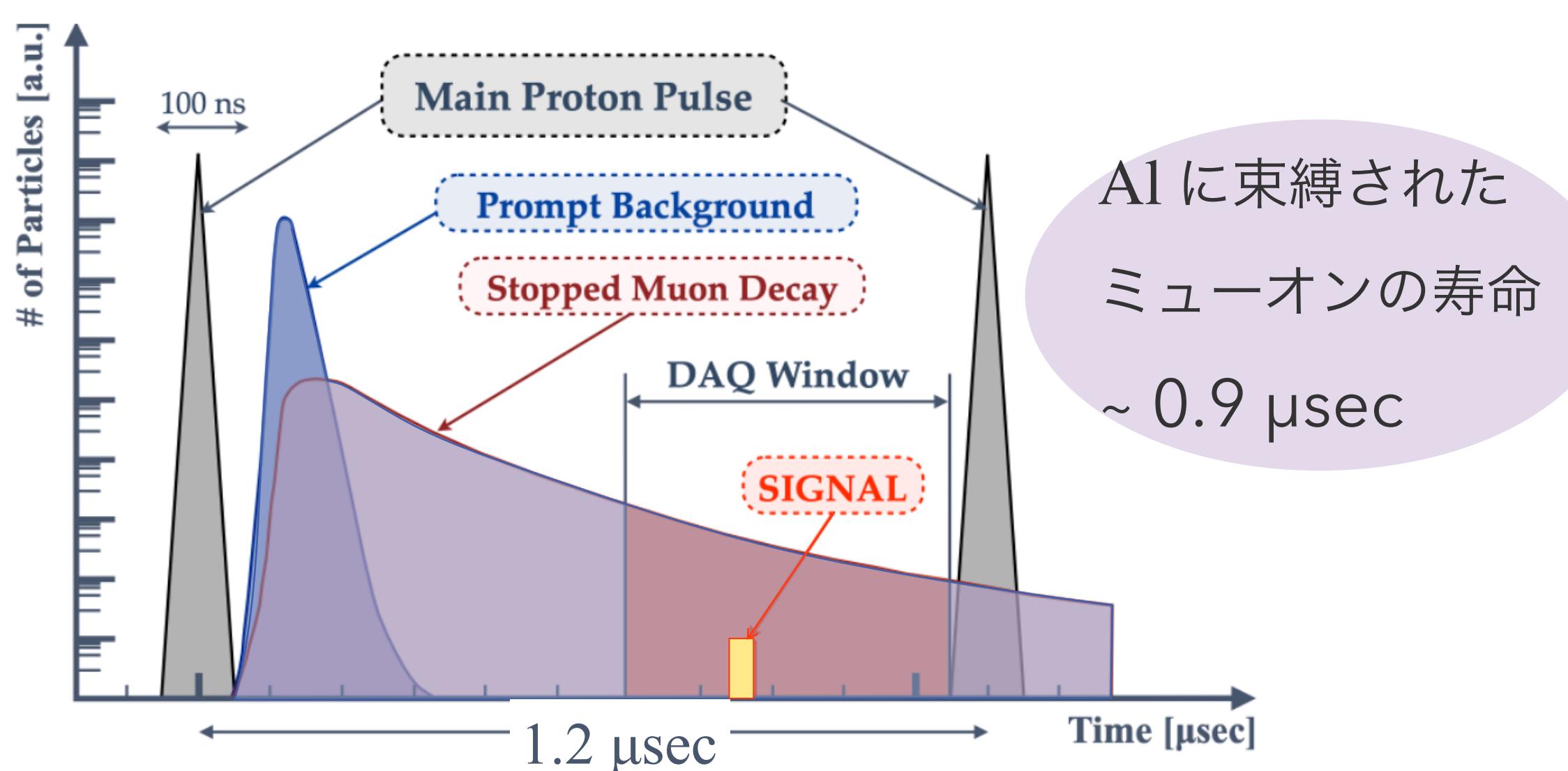

- ビーム**

- 大強度陽子ビーム  $\sim 10^{12}$  proton/sec

- 1.2  $\mu\text{sec}$  間隔パルスビーム

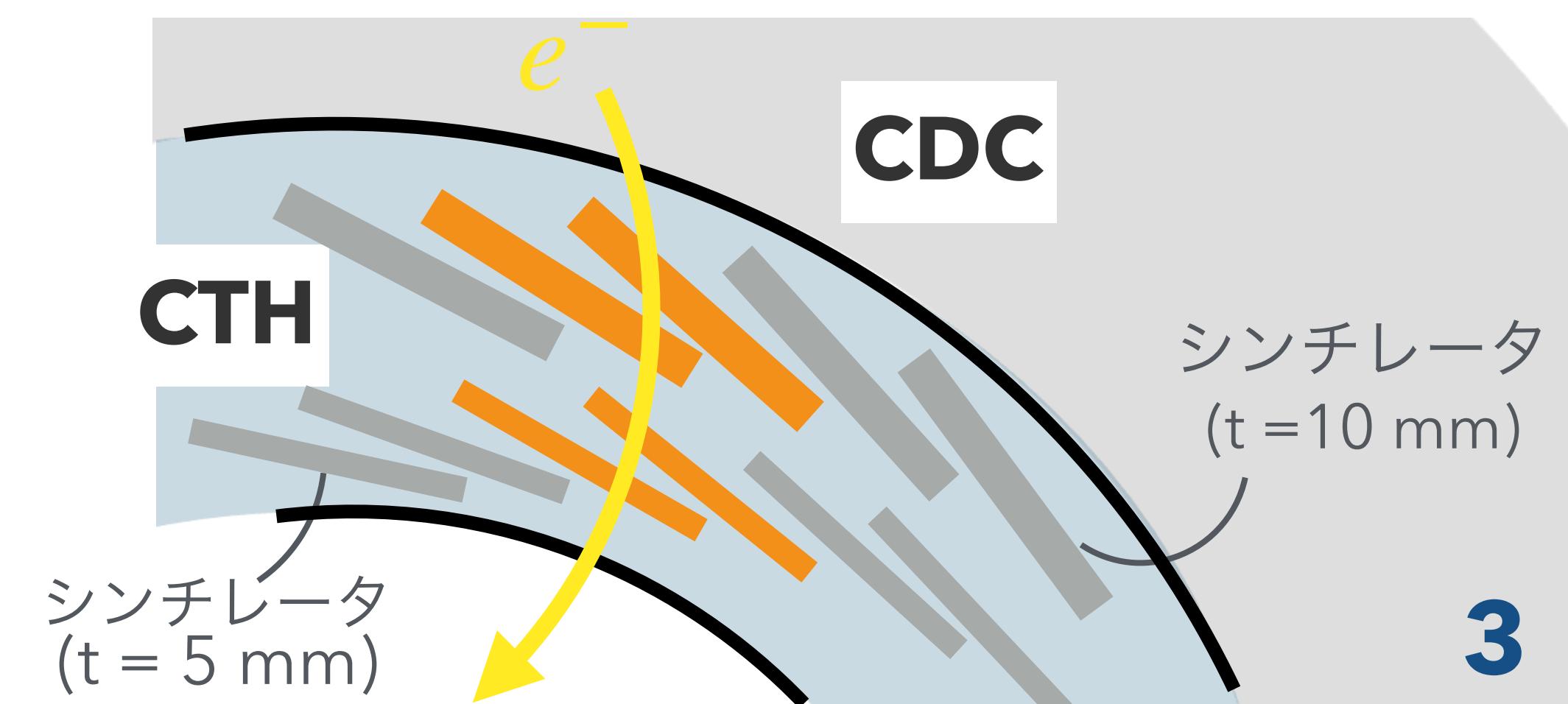

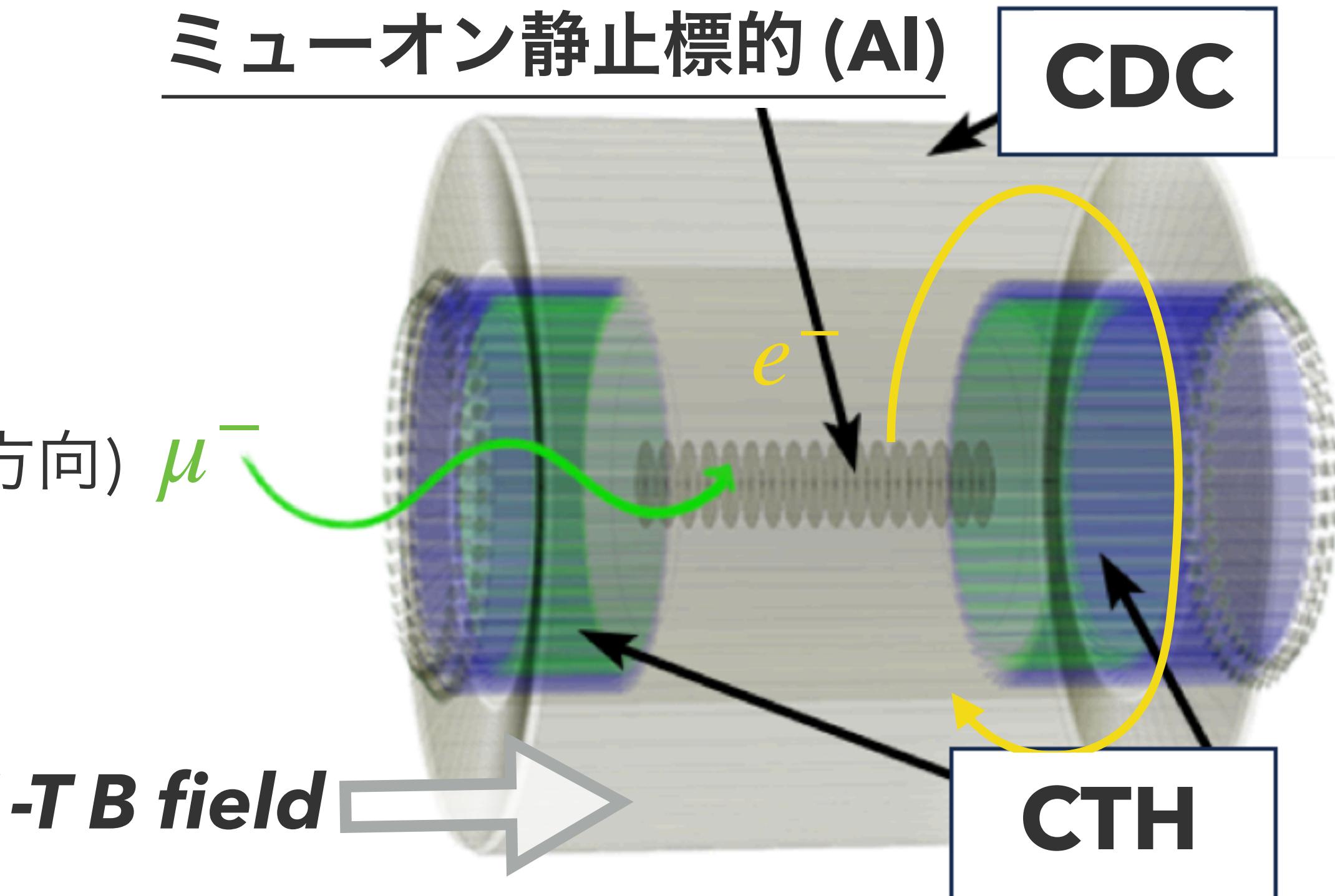

## CDC (Cylindrical Drift Chamber)

- 飛跡検出, 電子の運動量測定

- He:iC<sub>4</sub>H<sub>10</sub> = 90:10

- センスワイヤー 約5000 本

- 構造: 250セル(円周方向) × 20レイヤー(半径方向)

- 運動量分解能要求値 200 keV/c

A.Sato et al : [DOI:10.1016/j.nima.2024.169926](https://doi.org/10.1016/j.nima.2024.169926)

## CTH (Cylindrical Trigger Hodoscope)

- Primary trigger を生成

- 4重コインシデンスによる背景事象削減

- 時間分解能要求値 1 nsec

- プラスチックシンチレータ 64枚×2層×2(上流, 下流)

### ミューオン静止標的 (AI)

# トリガーシステムに対する要求

---

- 信号事象選択効率 > 90%

- トリガーレート < 20 kHz

- CTHのみのトリガーレート > 100 kHz → CDCトリガーとコインシデンスを取り背景事象削減

- 高速 & 固定トリガー遅延 < 8.5 μs

- FPGAを用いたハードウェア処理

- 安定した通信 ~ 目標：デッドタイム1%未満

- ケーブル選定, 長期安定性試験, etc..

- 高放射線耐性  $10^{12} \text{ n}_{\text{eq}}/\text{cm}^2$ , 1 kGy @150日間

- 高放射線耐性ICの選定、光通信を避ける、SEU対策

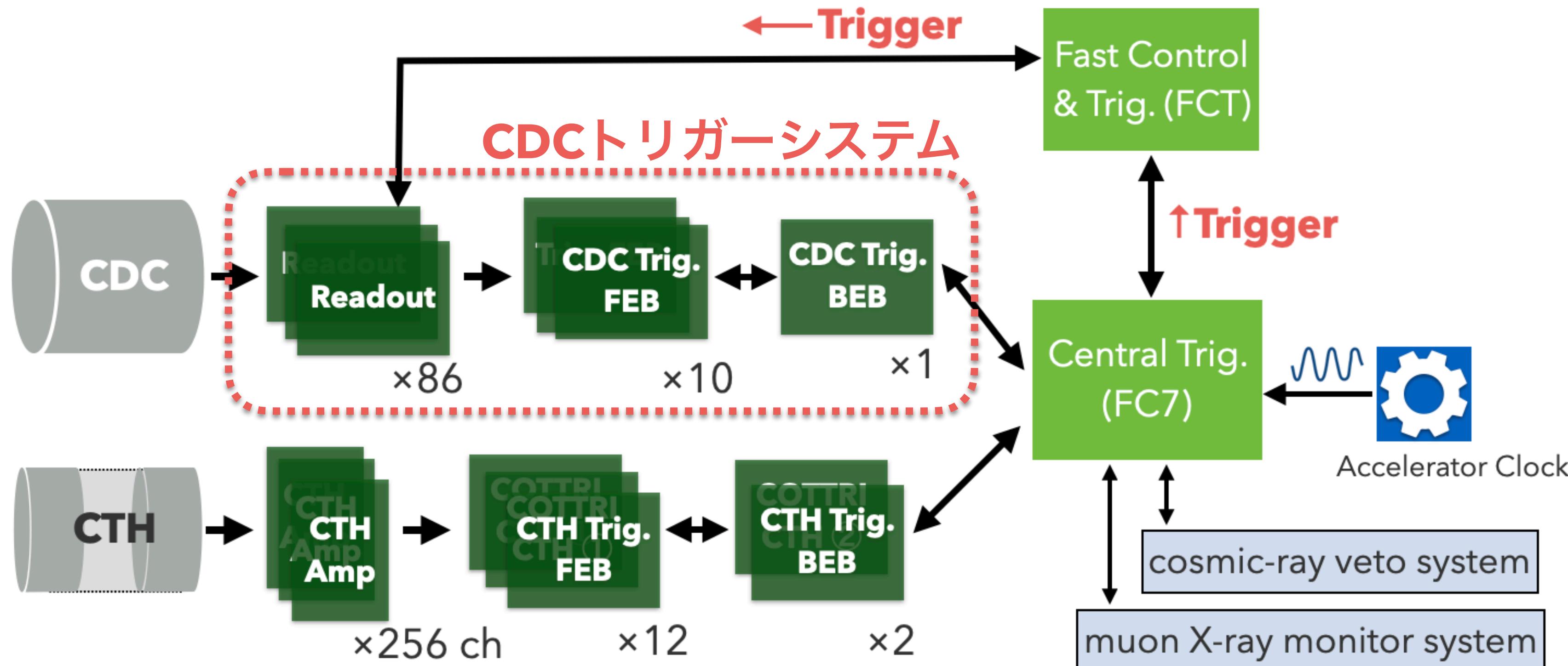

# トリガーシステム

- 多段階ハードウェアトリガーシステム

- CTHとCDCそれぞれでトリガー判断→ Central Trig. (FC7) でコインシデンスをとる

以下の基板にFPGA搭載

- CDC Readout** : Virtex-5

developed by Belle II

- Trig. FrontEndBoard (FEB),

Trig. BackEndBoard (BEB)** : Kintex-7

developed by COMET

- FCT** (Fast Control & Trigger) : Kintex-7

developed by COMET

- FC7** : Kintex-7

developed by CMS@CERN

現在の状況 : CDCトリガーシステムを構成する全基板を接続, 固定遅延用 fw開発中

このトーク: CDCトリガーシステムの現状、(CTH : 住村さんの発表)

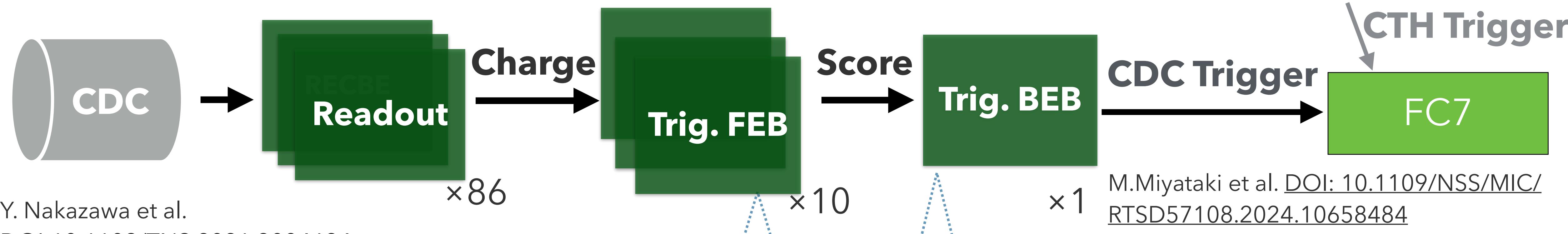

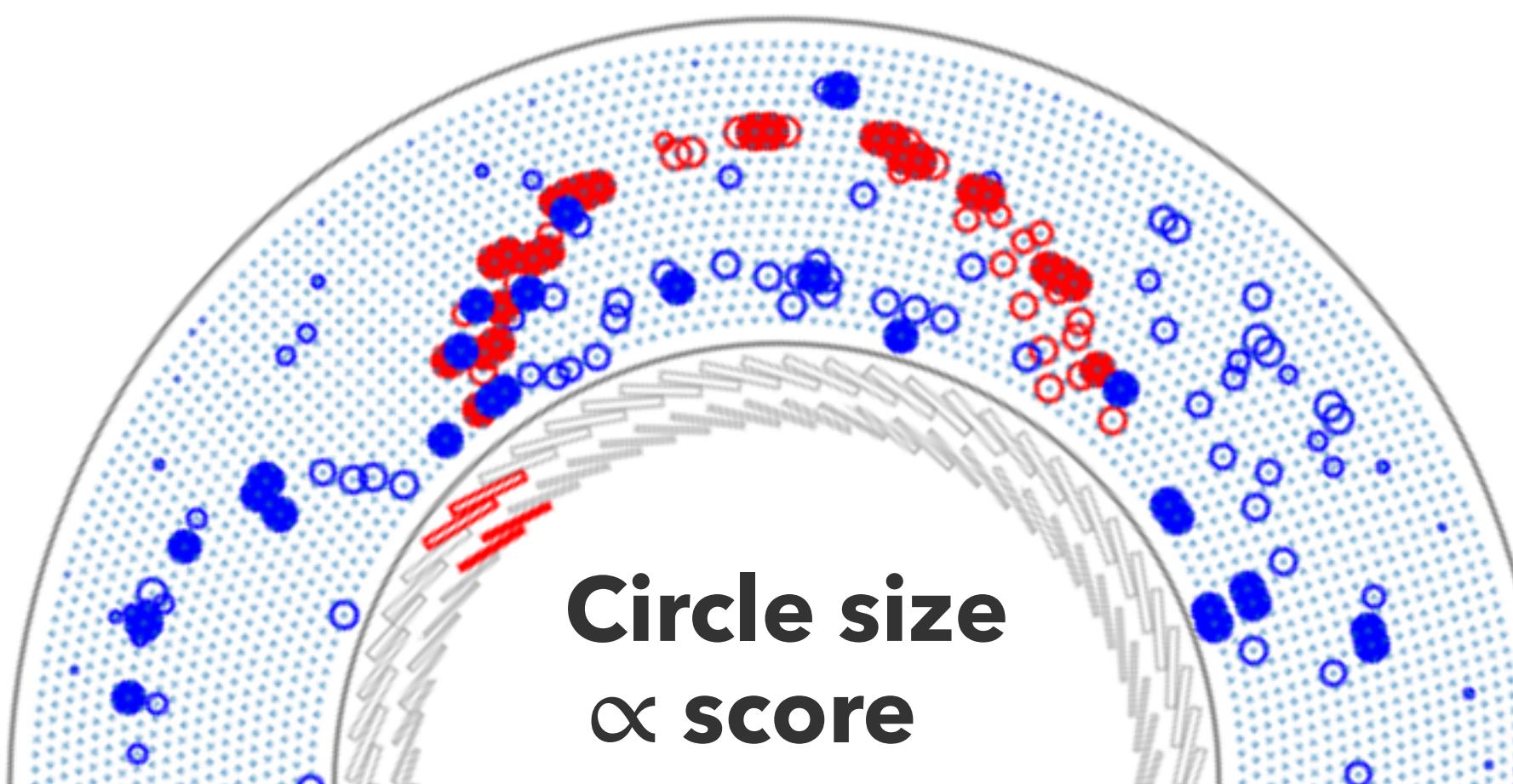

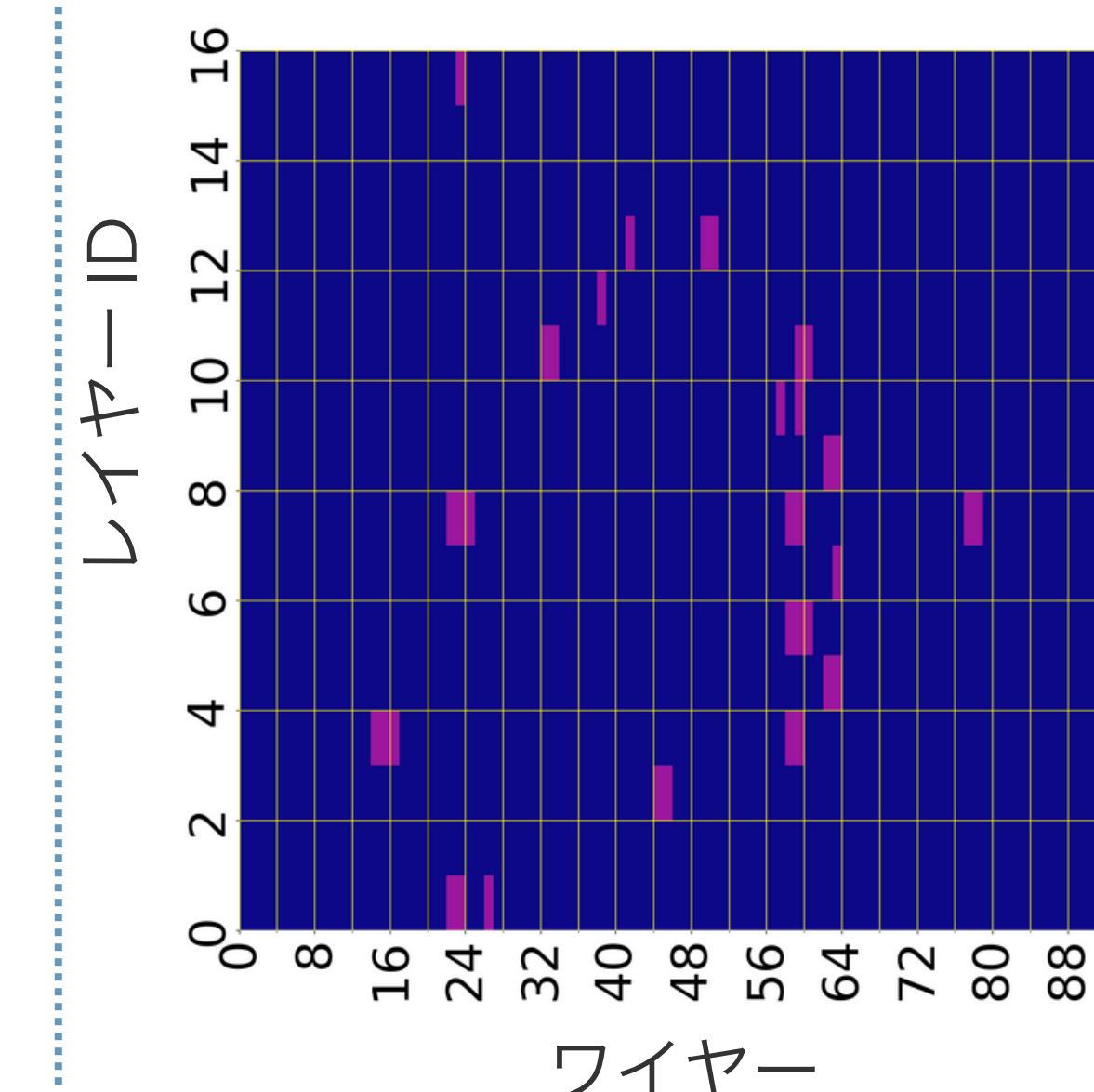

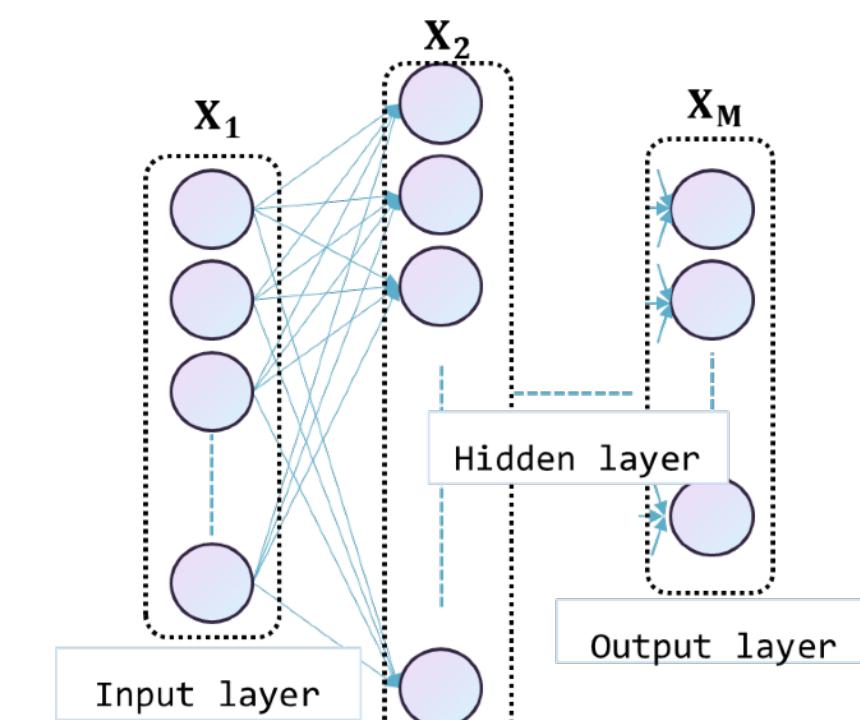

# CDC トリガーシステム・アルゴリズム

各ワイヤーにスコア付け (GBDT)

Input : ターゲットワイヤーの ADC sum (2bit @10MHz)

隣り合う二つのワイヤーのADC sum (2bit @10MHz x2)

レイヤーID

Score  $\leq 0.75$

○ Signal

○ Back ground

Score  $> 0.75$

● Signal

● Back ground

スコア分布から事象分類 (Neural Network)

開発中

2024年の計測システム

研究会で宮滝さんが発表

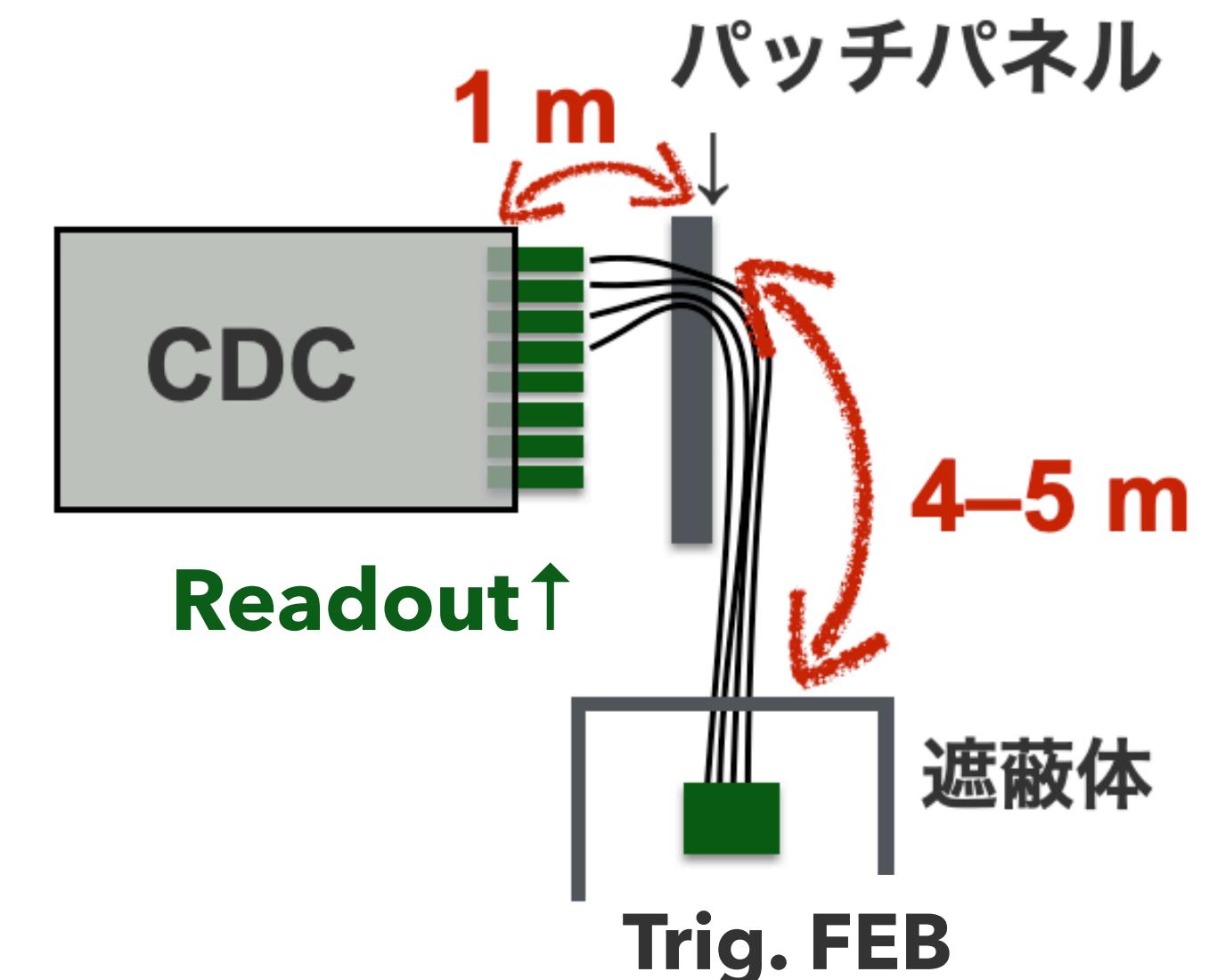

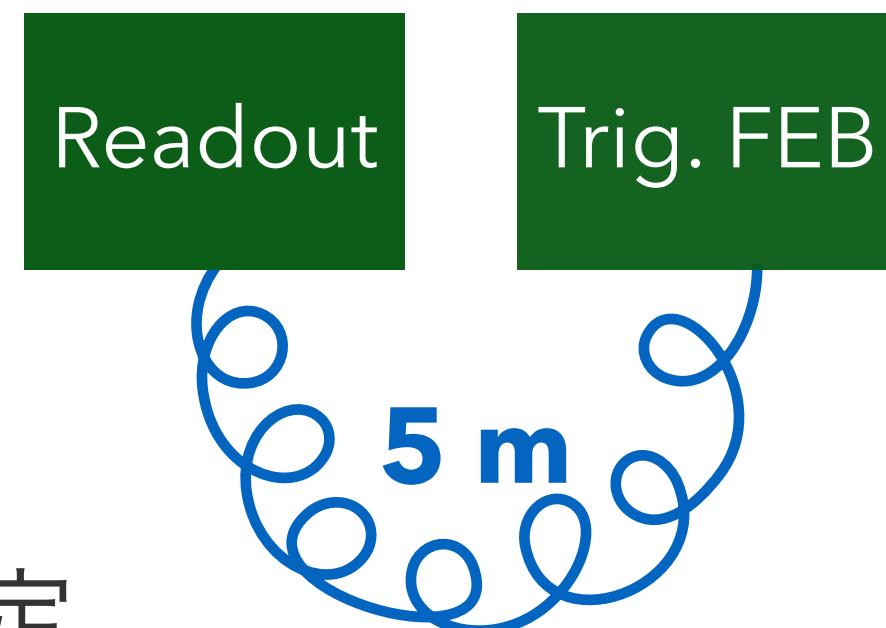

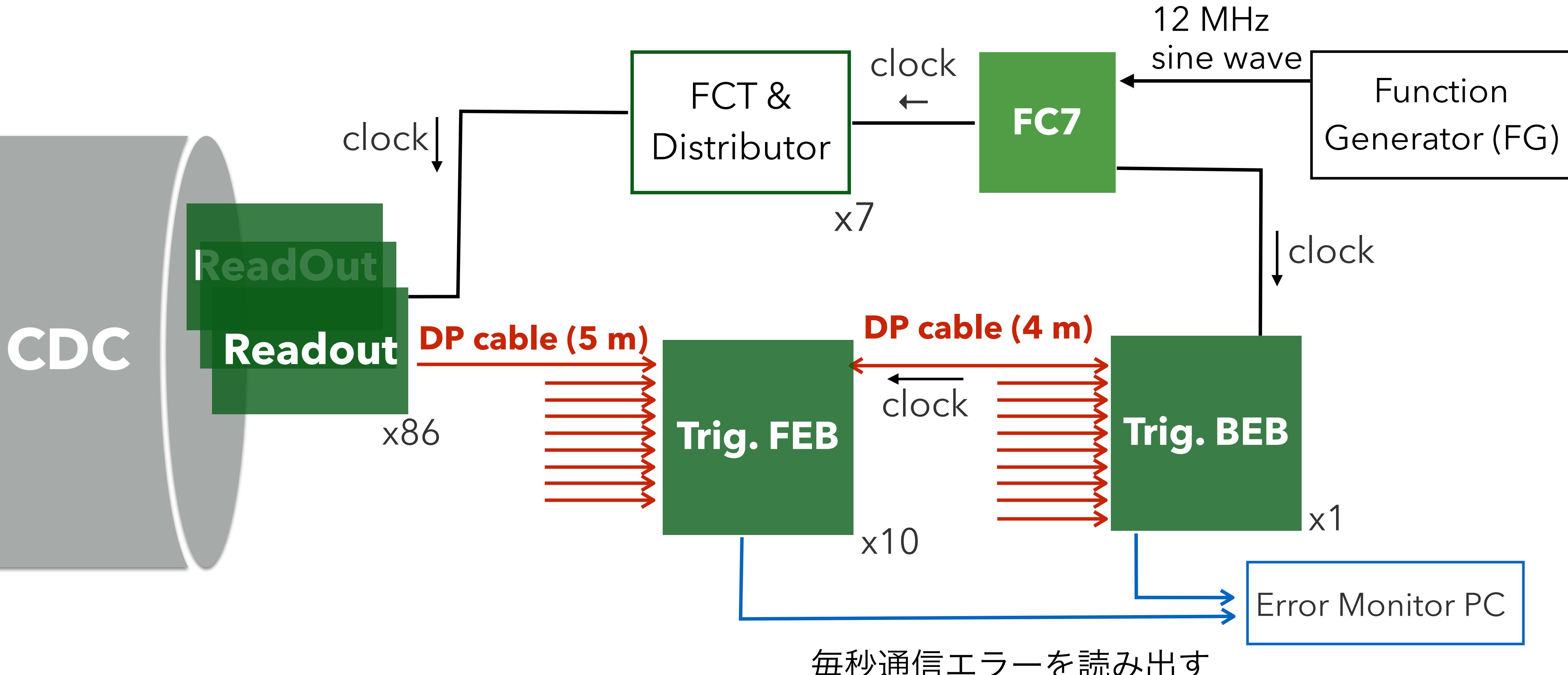

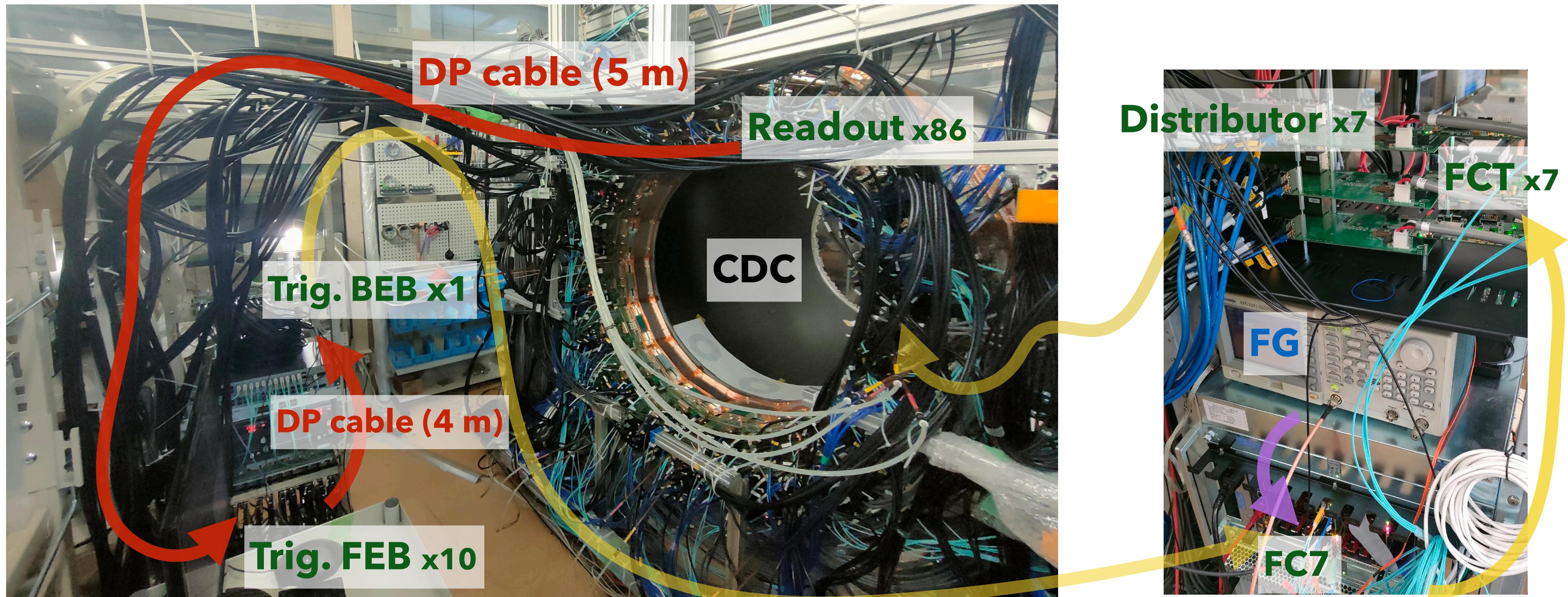

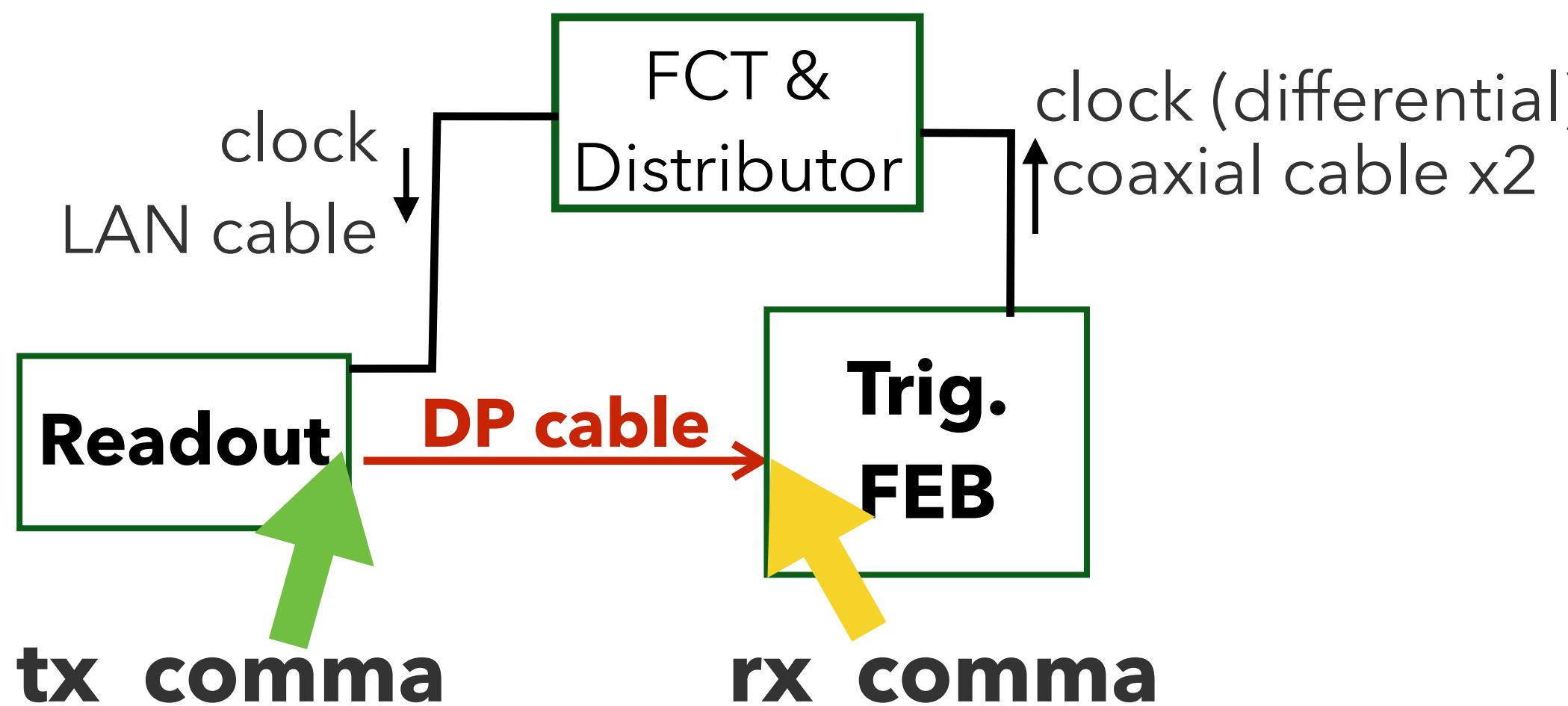

# トリガーシステム基板間の通信

接続 : DisplayPort (DP) ケーブル (copper)

RECBE - Trig. FEB 間 長さ要求値 : 約5 m

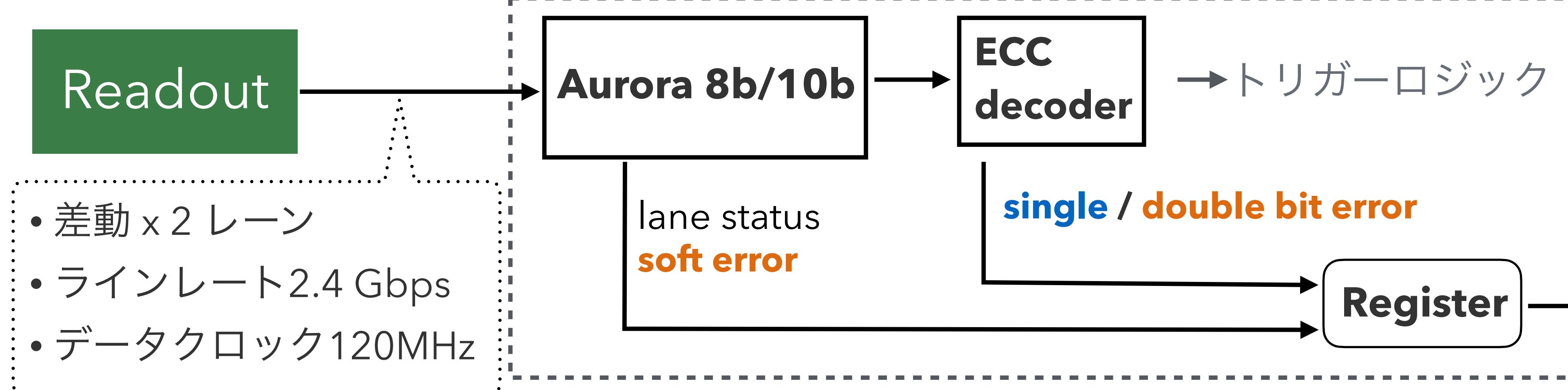

通信プロトコル : Aurora 8b/10b

通信エラー検出 :

- Aurora 8b/10b : **soft error** (8b10b符号エラー), lane status

- Error Correction Code (ECC) : **single bit error**, **double bit error**

ケーブル配線イメージ図

## FPGA on Trig.FEB

青: 自動修正可能

オレンジ: 自動修正不可

# CDCトリガー基板を用いた測定

## ・通信安定性測定

- ・本番用に選定した5 mのDPケーブルを使用し、通信安定性を確認

- ・通信が切斷した場合 → 通信リセット

- ・回復不能の場合、firmware を再プログラムする：3分のデッドタイムを想定

- ・全ケーブル接続時の要求エラーレート  $< 5.6 \times 10^{-5}$  **error/sec** for <1% デッドタイム

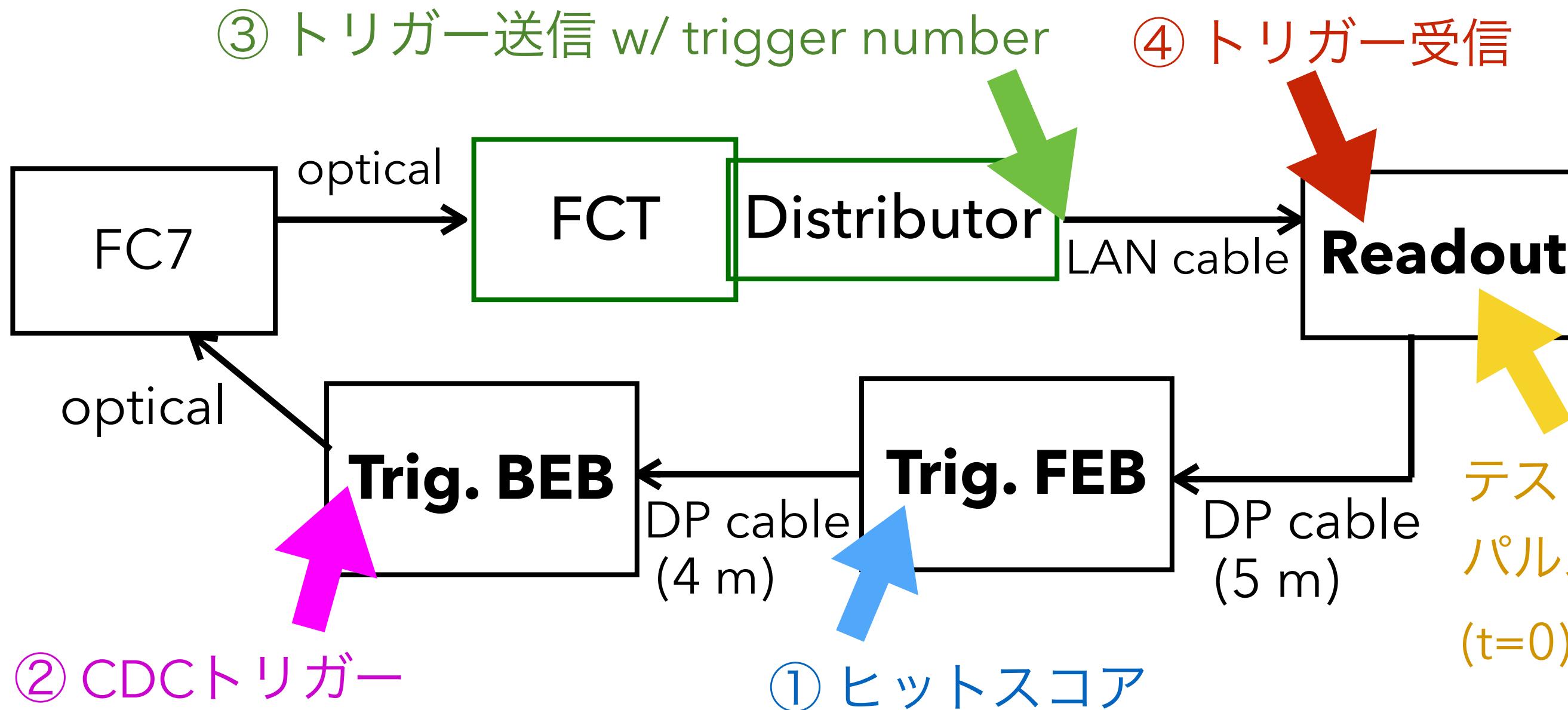

## ・トリガー遅延測定

- ・CDCトリガーだけで **8.5  $\mu$ sec 未満** の遅延要件を満たすか確認

# 通信安定性試験セットアップ

# 通信安定性試験 @ J-PARCハドロン実験準備棟

CDCトリガーシステムに関連する 全ケーブル,全基板 を接続

66,880 秒 (~18 時) 間測定 → 通信エラーなし

エラーレート  $< 4.6 \times 10^{-5}$  error/sec (95% C.L.)

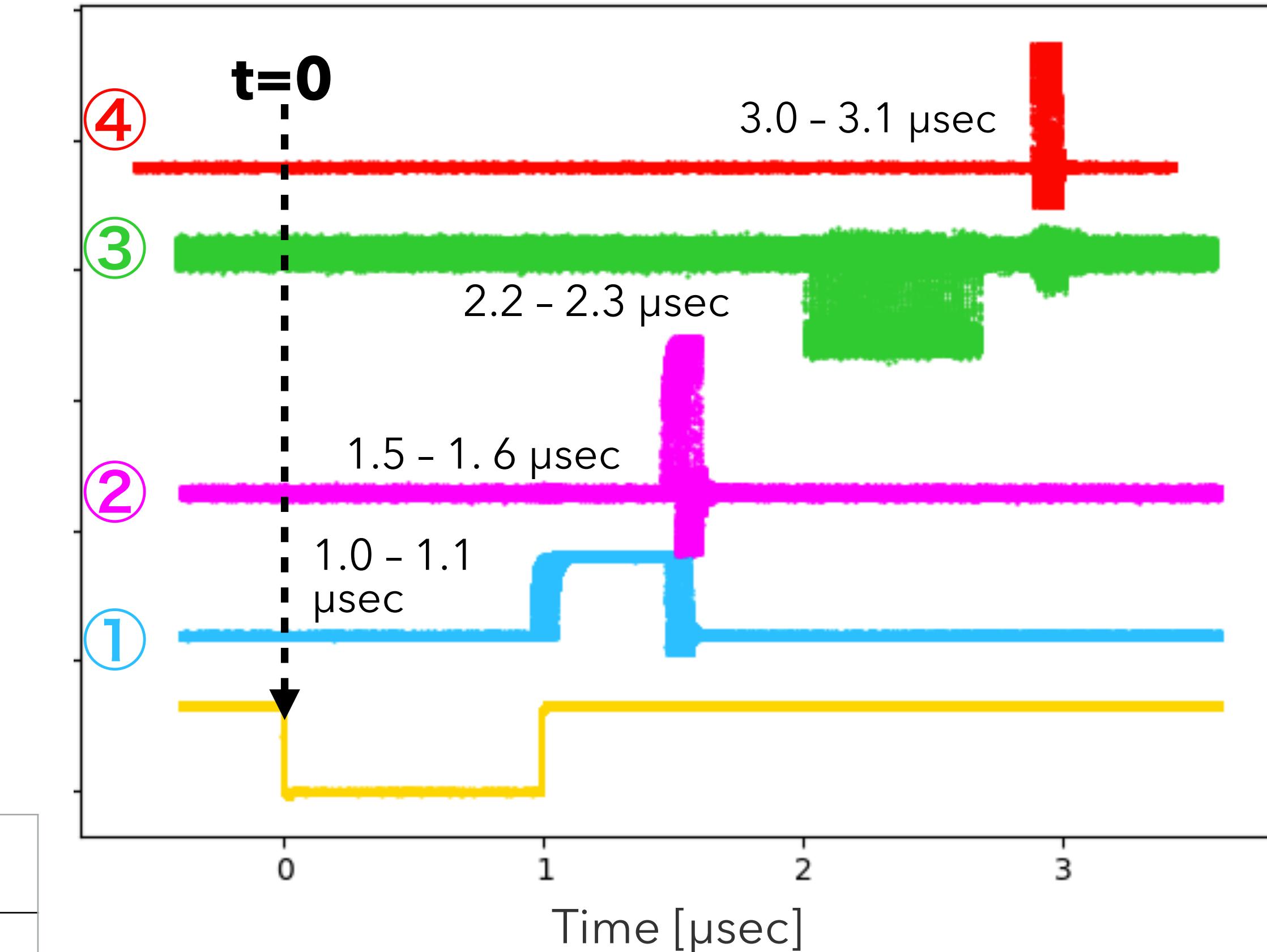

# トリガー遅延測定

各基板1枚ずつのチェーン

|              | 遅延時間 [μsec]      |

|--------------|------------------|

| 遅延時間測定値      | 3.0-3.1          |

| CDCドリフト時間    | 0.4              |

| <b>Total</b> | <b>3.4 - 3.5</b> |

<< 8.5 μsec

要求値未満

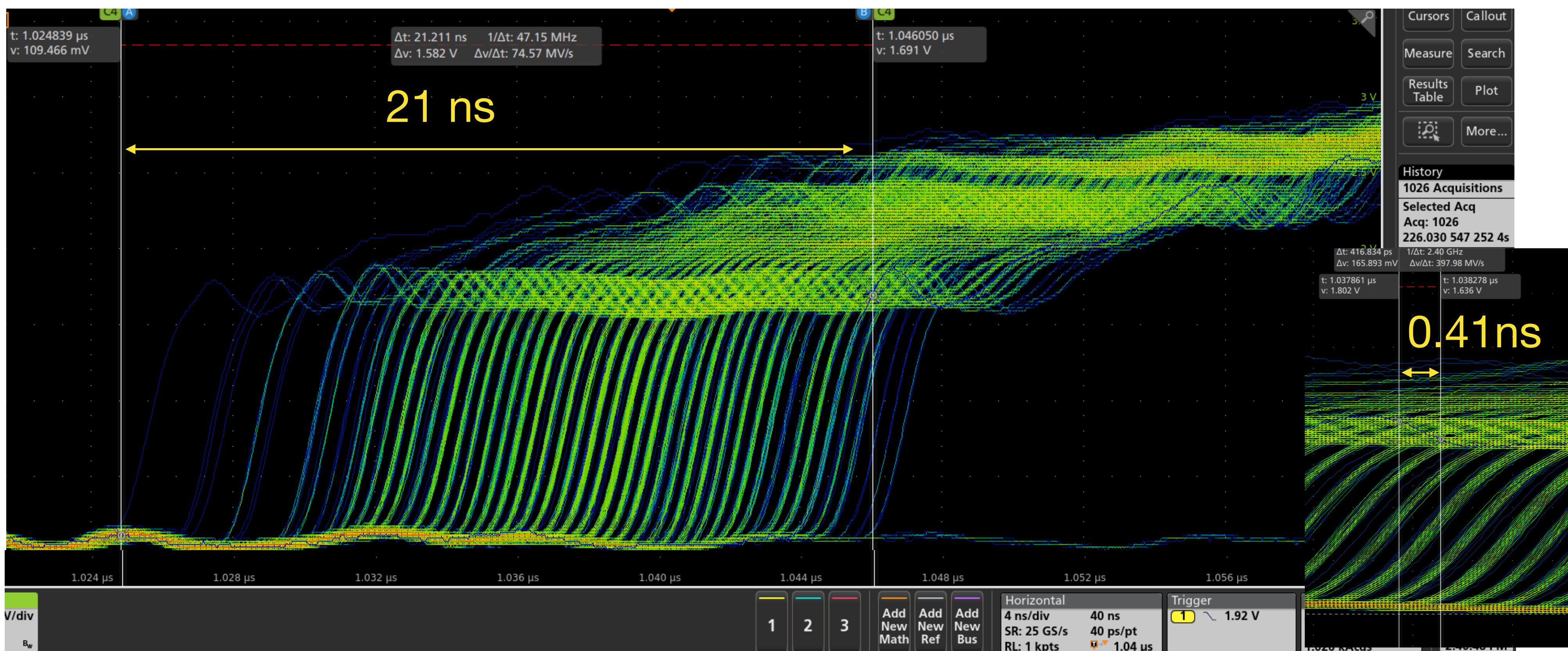

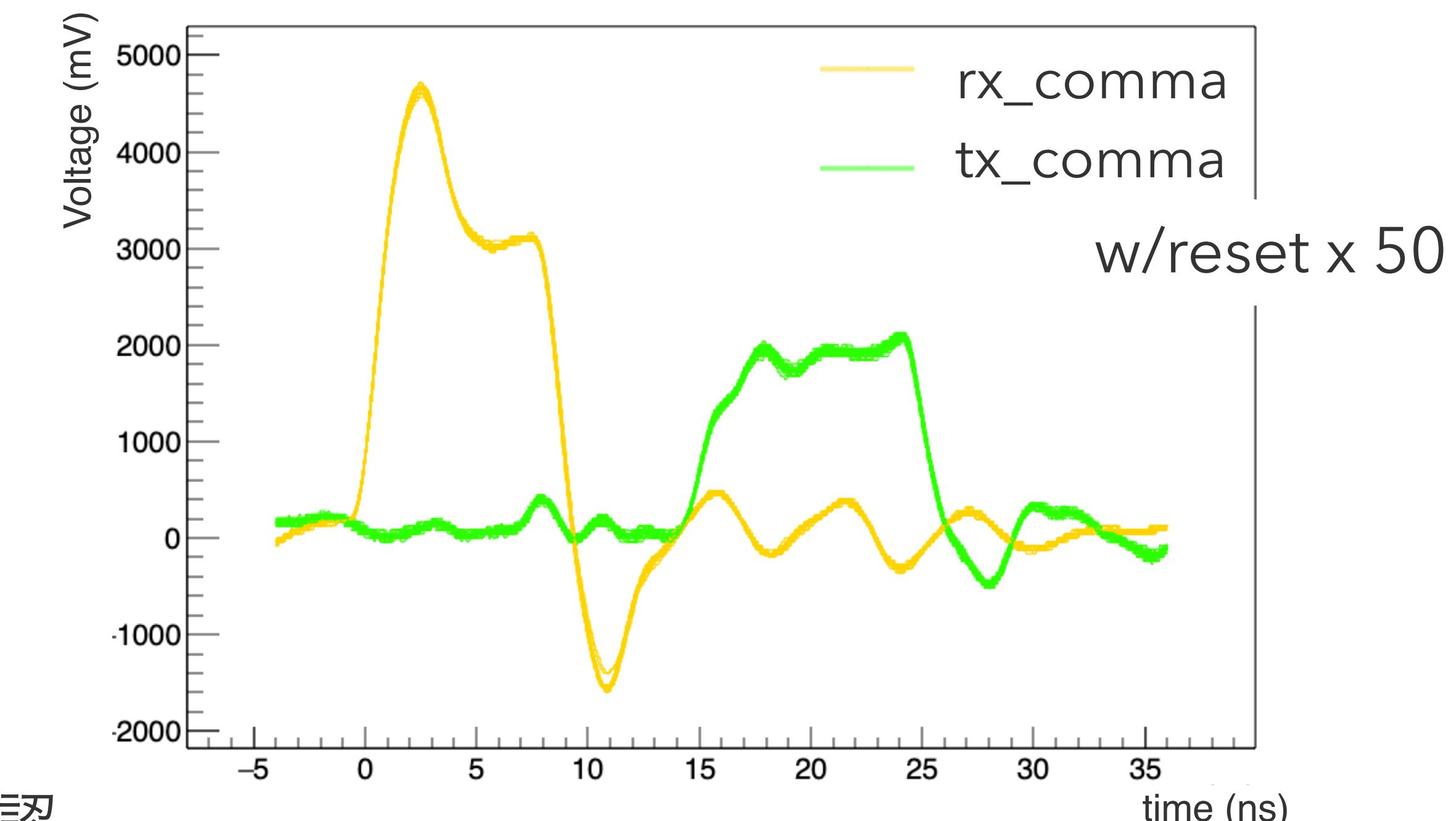

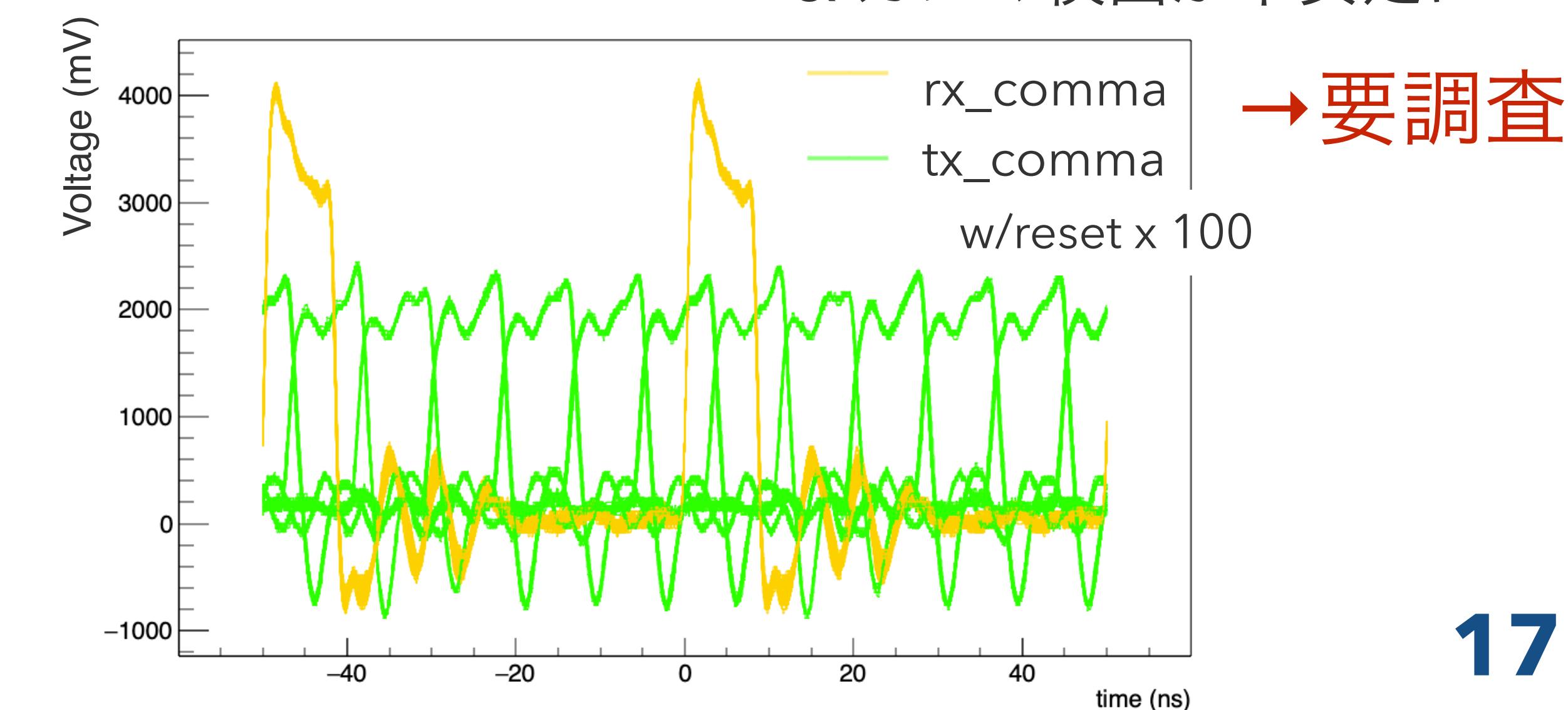

# トリガー遅延に関する問題点

- 通信モジュールをリセットすると遅延時間が変わる

- ATLASではこれを解決しているとの情報を聞き、教えを請う（去年の計測システム研究会）

trigger: テストパルス送信タイミング@Readout      信号: テストパルス受信タイミング@Trig. FEB

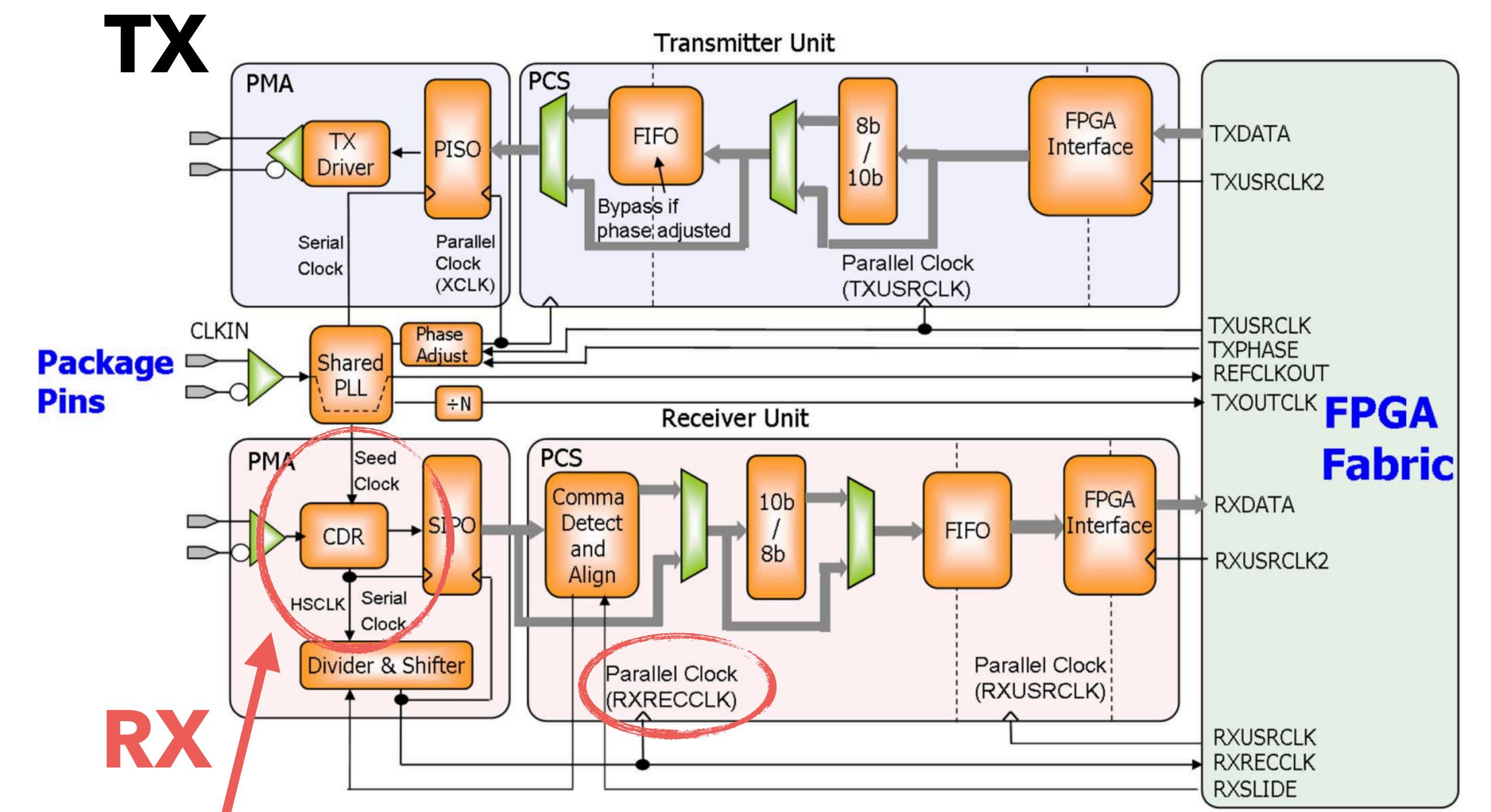

# 固定遅延通信firmware開発

ATLASの手法↓を真似して通信モジュールを改修

ref.) R. Giordano and A. Aloisio, "Fixed-Latency, Multi-Gigabit Serial Links With Xilinx FPGAs,"

(⚠私の理解。間違ってたらすみません。。。)

遅延時間変動の原因

- RXバッファ, TXバッファの取り出し位置が変動

- リカバリクロックの位相がリセット毎で変動

シリアルデータクロックの周期 (UI) 単位でパラレルデータクロックの位相に自由度があり、パラレルデータのフレームをPCS (Physical Coding Sublayer) 層で調整する場合、リカバリクロックの位相が一意に決まらない

対処方法

- バッファはバイパスする

- 共通のリファレンスクロックを使っている場合にのみ可能

- パラレルデータビットシフトをPCS層ではなくPMA (Physical Medium Attachment) 層で行う

CDR (Clock Data Recovery) でパラレルデータクロックの位相が決まる

# 固定遅延通信firmware開発

---

## 具体的な実装

- これまで : Auroraプロトコルのモジュールを生成する LogicIPCore Aurora8b10b で通信モジュール作成

- リンク層まで作ってくれるのでほとんどそのまま実装できる

- 実装は比較的簡単だがカスタマイズが難しい

- GTX Transceiver Wizard IPで作り直し

- 物理層のみ作成され、自由度が高い (=難しい、、、)

- 固定遅延の場合、レーンごとにリカバリクロックが異なるため、2 lane × 10 chのデータを合わせるのに苦戦

東大ATLAS奥村さん、KEK e-sys本多さんとかなり助けていただいています m(\_\_)m

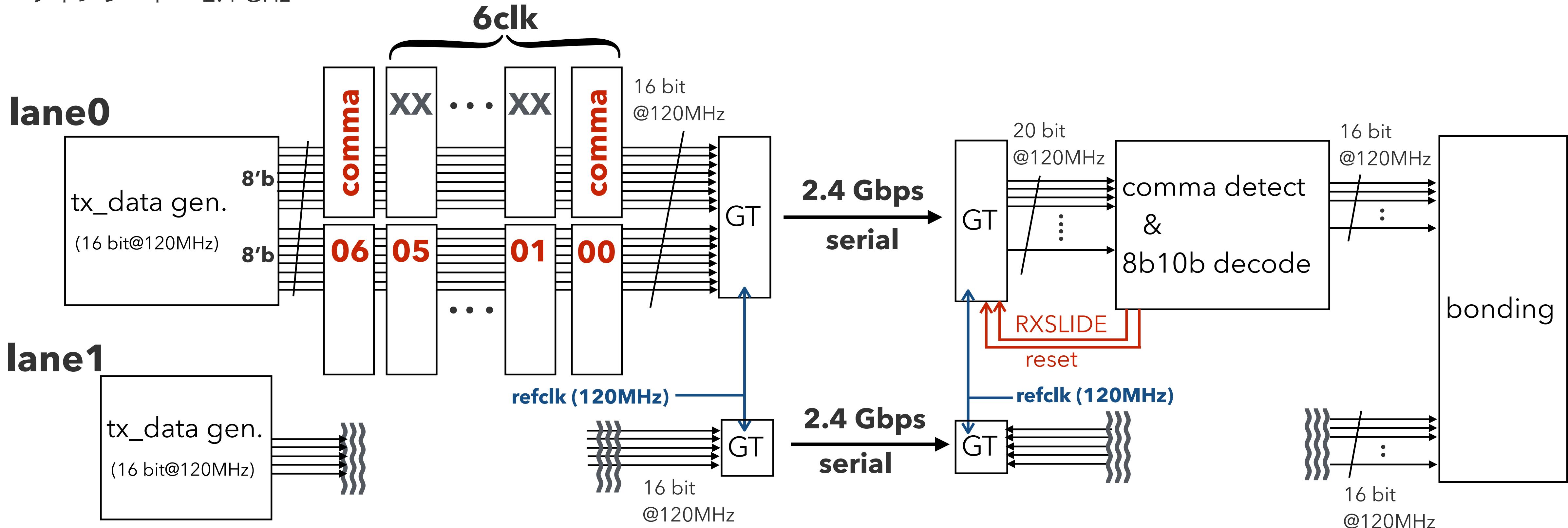

# 固定遅延通信firmware 構造図

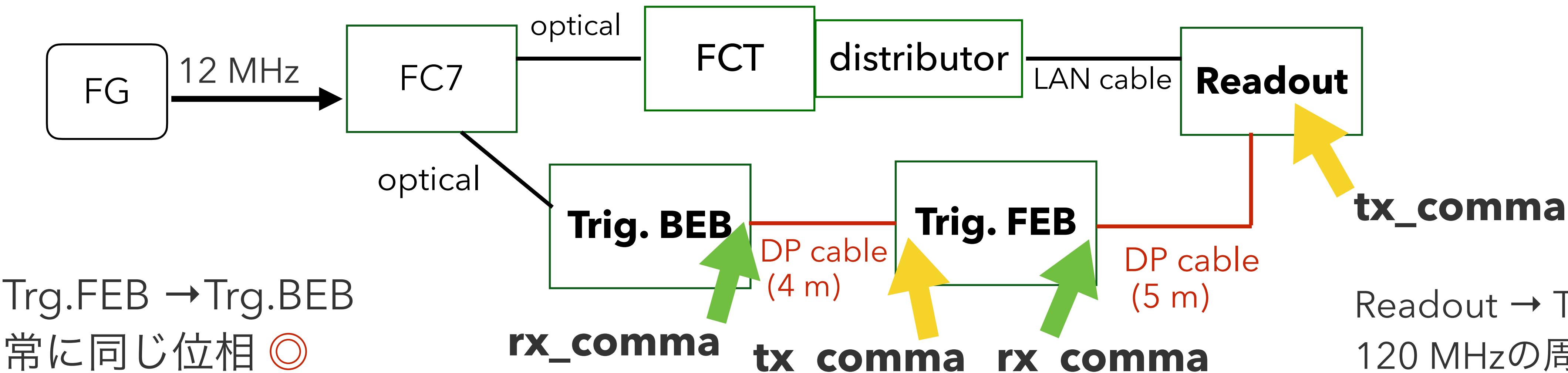

TX : テスト用データとして 8 bitのカウンタ + (6 clockに一回) カンマワード (K28.5) を送信

RX : カンマワードを検出するまでRXSLIDEをPMAモードで実行、偶数RXSLIDEの場合はリセットも送信

bonding : 共通クロックに載せ替え、カウンタを見てシフトレジスタでタイミング調整

リファレンスクロック (refclk) = 120MHz (全基板で共通のクロックソース)

ラインレート = 2.4 GHz

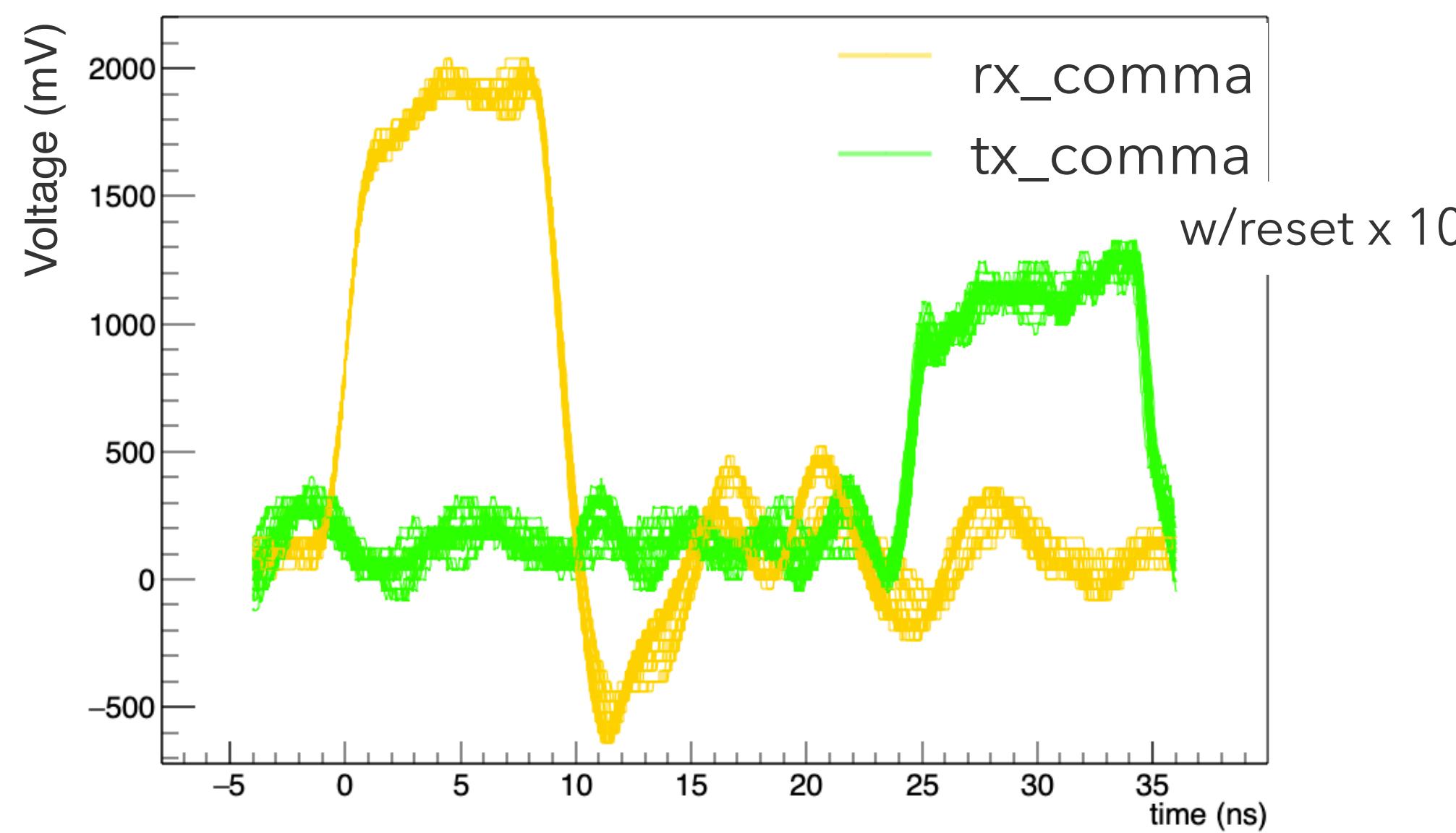

# 固定遅延通信firmware検証 @ミニマムセットアップ

## firmware開発用ミニセットアップで開発

ミニマムセットアップ (clock source : Trig.FEB のオシレータ)

header pinに出力し、オシロスコープで測定 →

カンマワードのタイミングの位相で遅延時間の変動を確認

リカバリクロックの位相が固定されていることを確認

データ確認：カウンタデータをTCP/IPで周期トリガーで取得

|    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 00 | 00 | a6 | a6 | a5 | a5 | a4 | a4 | a3 | a3 | a2 | a2 | 00 | 00 | 00 | 00 |

| 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 | 00 |

1event = 16 bit × 2 lane × 5フレーム

2 laneでデータが揃っている◎

# 固定遅延通信firmware検証 @フルチェーンセットアップ

FC7込みのフルチェーンセットアップで位相測定

# まとめと今後の展望

---

- **COMET Phase-I** は  $\mu - e$  転換を探索する実験

- 目標单一事象感度 :  $3 \times 10^{-15}$  (先行実験の100倍)

- トリガーシステム

- 高速 & 高事象選別 & 高安定性が求められる

- CDC(飛跡検出) & CTH(タイミング検出 & 4重コインシデンス) の組み合わせ

- **CDCトリガーシステム通信試験**

- 通信安定性測定 : 全基板で1%未満のデッドタイムで安定した通信を確認

- トリガー遅延時間測定 : 要求値 8.5 nsecを満たすことを確認

- しかし、リセットによる遅延時間の変動が問題となっている

- 研究室や実験グループを超えて相談できる繋がりが非常に助かっています

- **今後の展望**

- 固定トリガー遅延のためのfirmware改修

- 全数で遅延時間測定 & トリガー性能試験