MoGURA

概要

当初は1kton液体シンチレータ型反電子ニュートリノ検出器 (KamLAND)の次期フェーズのために必要なFADCボードを開発することを目的としていた。KamLAND全体の方針により、次期フロントエンド回路はRFSoCをベースとしたものに変更となった。本プロジェクトは

- RFSoCベースのフロントエンド回路のための要素技術検証 (アナログ回路、デジタルベースライン補正)

- RFSoCベースのフロントエンド回路と同様にインターフェスを持ちキャリブレーション時などに遠隔地での統一的なデータ取得を補助するサブのフロンドエンド回路

- ニュートリノ科学研究センターでのPMTを使ったテストベンチでの使用

メンバー

- 石徹白晃治 (代表:東北大学・准教授)

- 鈴木貴士 (東北大学 技術職員)

- 池野正弘 (IPNS KEK)

- (過去メンバー, 所属は当時)

- 竹本康浩 (大阪大学 助教)

- 林田真悟 (東北大学)

- 大塚竣太 (東北大学)

- 本田佳己 (東北大学)

- 内田智久 (IPNS KEK)

機能・特徴

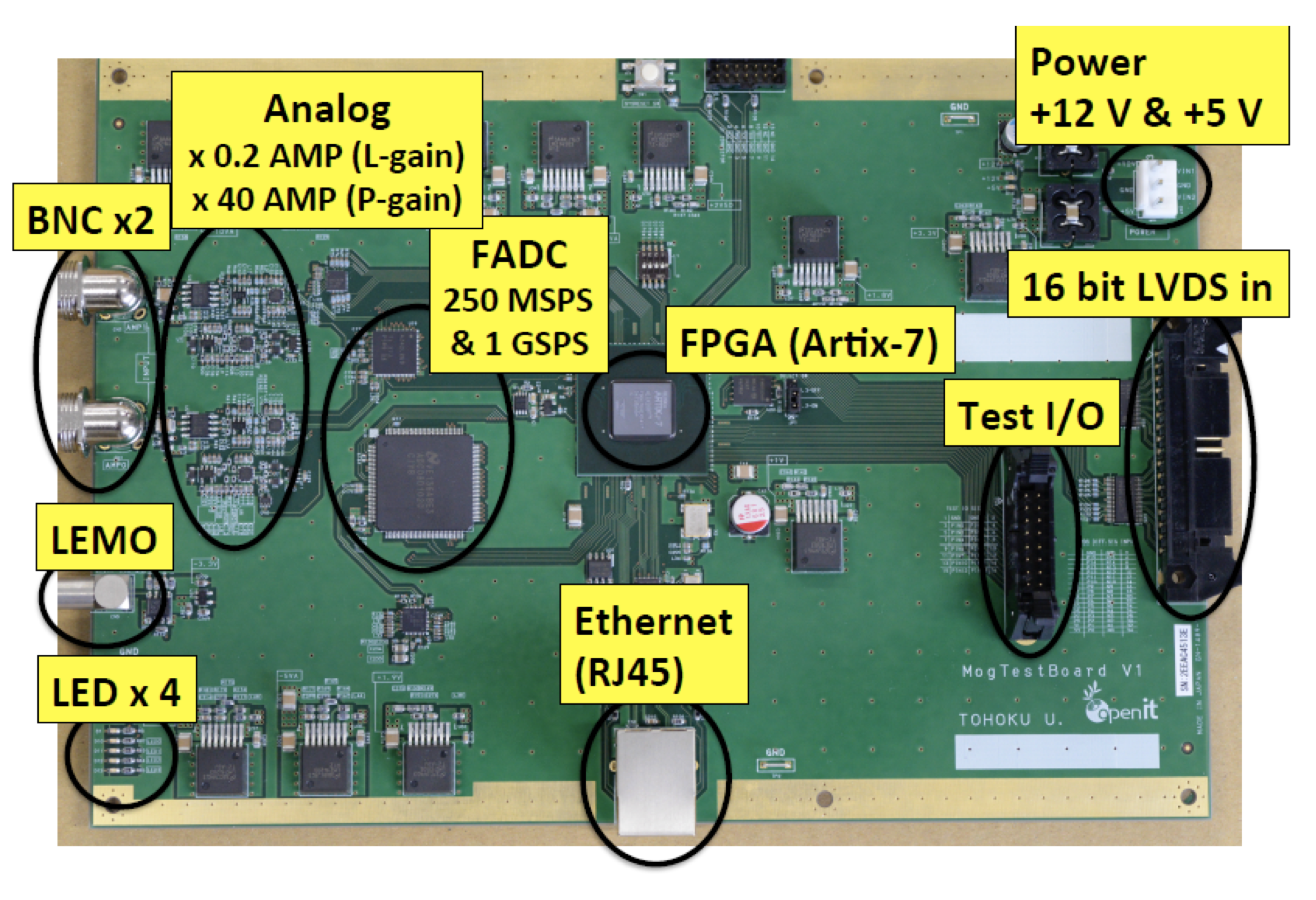

Ver1.

- 基板サイズ: VME6U (ただし, VME I/Fは持たない)

- 電源: +5V (デジタル), +12V(アナログ)

- 外部I/F: Ethernet (SiTCPを使用)

- FPGA: XC7A200T-2FBG676C

- ADC: ADC08D1020CIYB, ADS42LB69IRGCT

- アナログ:

- ADC08D1020CIYBでの1GS/sを想定して入力換算で+2mV -- -20mVを0.1mV分解能でカバーするp-ゲインチャンネル

- ADS42LB69IRGCTでの250MS/sを想定して入力換算で+3V -- -10Vを0.2mV分解能でカバーするl-ゲインチャンネル

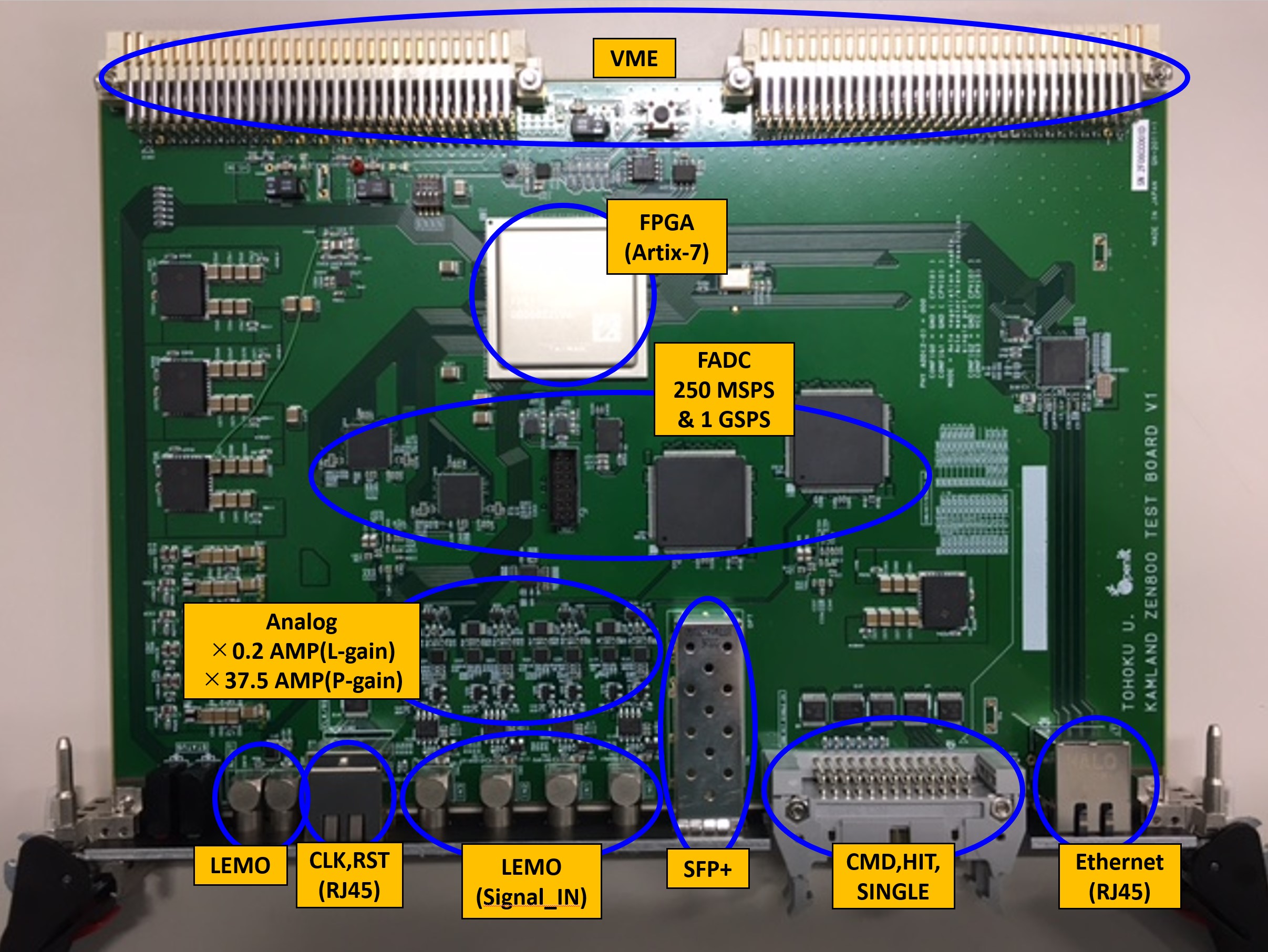

Ver2.

- 基板サイズ: VME6U (VME I/Fを持つ、電源供給のみ可、VMEバス未対応)

- 電源: +3.3V (デジタル), +5V (デジタル), +12V(アナログ)

- 外部I/F: Ethernet(SiTCPを使用), SFP+(波形情報取得),

- FPGA: XC7A200T-2FFG1156C

- ADC: ADC08D1020CIYB, ADS42LB69IRGCT

- アナログ:

- ADC08D1020CIYBでの1GS/sを想定して入力換算で+2mV -- -20mVを0.1mV分解能でカバーするp-ゲインチャンネル

- ADS42LB69IRGCTでの250MS/sを想定して入力換算で+3V -- -10Vを0.2mV分解能でカバーするl-ゲインチャンネル

公開リソース

図・写真等

- Ver1の写真

発表論文リスト

- 林田 眞悟, 次期KamLAND実験へ向けたフロントエンドエレクトロニクスの開発, 東北大学修士論文 (2016)

- 石川 貴寛, KamLANDにおける近傍超新星ニュートリノ観測に向けた新規トリガー機能開発, 東北大学修士論文 (2016)

- 本田 佳己, KamLAND2-Zenに向けた10Cバックグラウンド低減のための新手法の研究開発, 東北大学修士論文 (2019)

- 大塚 竣太, KamLAND2に向けた新型読み出し回路のアナログ部の最適化とデジタルBLRの実証, 東北大学修士論文 (2019)