シリコンストリップ検出器デジタル読み出し集積回路

概要

g-2実験用シリコンストリップデジタルパターン読み出し集積回路の開発を行う。

g-2で使用するシリコンストリップの仕様はg-2のホームページを参照の事。

ミューオン崩壊からの荷電粒子の入射レートは3MHz/chであり、この環境下でトラックを効率よく検出するためにパターンファインダーにおけるコインシデンスウインドウは5〜7nsec程度に短くしたい。よってTime walkを同程度以下に抑える必要がある。また高レート環境下でパイルアップを防ぐためにパルス幅100nsec未満になるようにシェーパーの時定数を短くしかつS/Nを10以上に確保しなければならない。

メンバー

- 三部勉、Mibe Tsutomu(代表:高エネルギー加速器研究機構、素粒子原子核研究所、准教授)

- 池田博一, Ikeda Hirokazu (JAXA, 教授)

- 池野正弘, Ikeno Masahiro (KEK素核研, シニアフェロー)

- 上野一樹, Ueno Kazuki (KEK素核研, 助教)

- 内田智久, Uchida Tomohisa (KEK素核研, 准教授)

- 佐々木修, Sasaki Osamu (KEK素核研, 教授)

- 庄子正剛, Shoji Masayoshi (KEK素核研, 准技師)

- 末原大幹, Suehara Taikan(九州大学 助教)

- 田中真伸, Tanaka Manobu (KEK素核研, 教授)

- 東城順治, Tojo Junji (九州大学, 准教授)

- 長澤翼, Nagasawa Tsubasa (九州大学, M2)

- 西村昇一郎, Nishimura Shoichiro (東京大学, D2)

- 真玉将豊, Matama Masato(九州大学, M1)

- 村上武, Murakami Takeshi (KEK素核研, シニアフェロー)

- 吉岡瑞樹, Yoshioka Tamaki (九州大学, 准教授)

機能・特徴

チャンネル数:128ch

チップサイズ:〜1cm x 1cm

アナログ部

チップサイズ:〜1cm x 1cm

アナログ部

コンバージョンゲイン:30mV/fC

ピーキングタイム:〜30nsec(可変)(パルス幅<100nsec)

ENC:<2000@30pF

ENC:<2000@30pF

出力:アナログモニター(切り替え)、10pF負荷ドライブ可、デジタル(全チャンネル)

チャンネル数:128ch

チャンネル数:128ch

デジタル部

機能:

TDC部:時間分解能5nsec

パターン記録メモリ

外部出力バッファ

シリアルインターフェース

アナログ部デジタルコントロール

テストパルス制御

アナログモニター制御

オフセット電圧制御

コンパレータ閾値制御

コンパレータON/OFF制御

公開予定リソース

NDAを締結後、回路図、レイアウトを公開

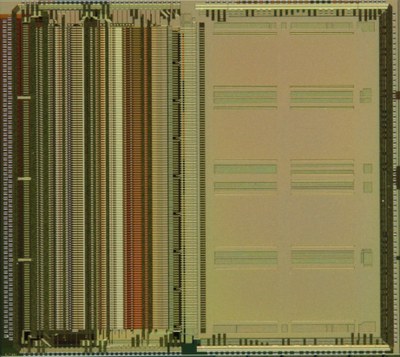

図・写真等

関連リンク

発表論文リスト

1.2014 Master 九州大学 調 翔平 ミューオンg-2/EDM実験に用いるシリコン検出器の読み出しASIC

2.2015 Master 九州大学 長澤 翼 J-PARCミューオンg-2/EDM実験に用いるシリコンストリップ検出器読み出しASICの開発