AMANEQ (連続読み出しDAQ用フロントエンド主回路)

概要

J-PARC E50実験ではトリガーレスでFEEからデータを収集し、ソフトウェアで選別お行う連続読み出しDAQの導入を進めている。

連続読み出しDAQにおけるFEEは全ヒットデータをPCへ送信する必要がある事かから、高速なデータリンクと十分な容量のバッファを有する必要がある。

本回路はE50実験におけるFEEの中心的役割を果たす予定であり、名称を

A main electronics for network oriented trigger-less data aquisition system (AMANEQ) とする。

10GbE版SiTCPであるSiTCP-XGを使用し、2GbのDDR3 SDRAMを搭載する。

これまでJ-PARCハドロンで開発した資産の再利用のため、メザニンスロットをHadron Universal Logic module (HUL) と互換とする。

メンバー

- 本多良太郎 (代表: KEK 素核研)

- 高橋智則 (理化学研究所)

- 池野正弘 (KEK 素核研)

- 庄子正剛 (KEK 素核研

機能・特徴

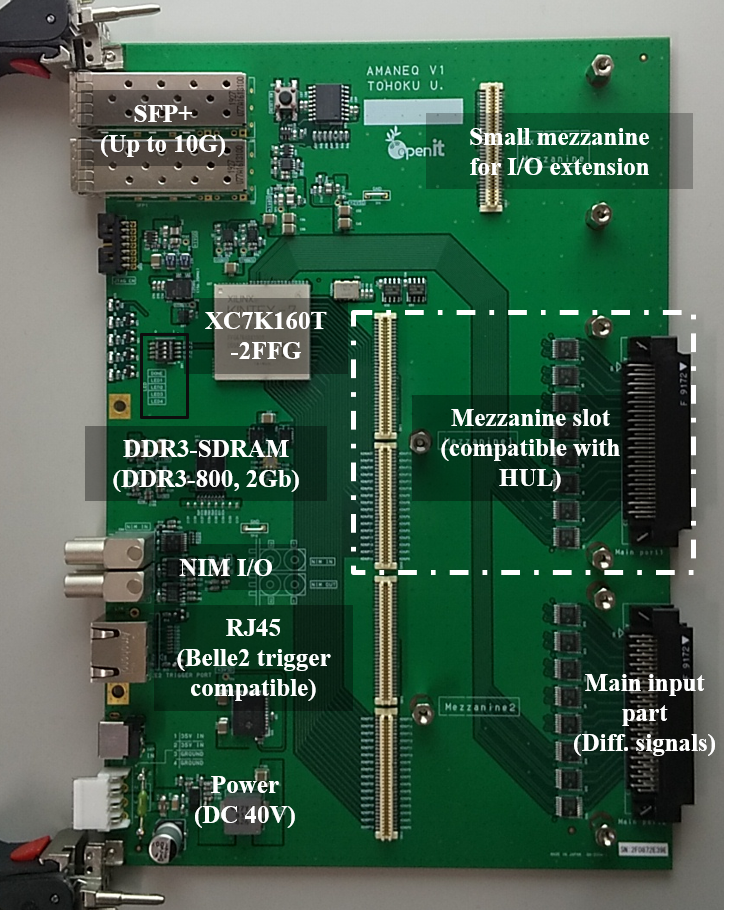

基板特徴

基板サイズ

- VME 6Uサイズ(サイズのみ。VMEバスは存在しない。)

- バックプレーンや電源がないVMEサブラックに挿入可能

FPGA

- Kintex-7, XC7K-160T-2FFG676 (speed grade -2)

DDR3-SDRAM

- 最大DDR3-1333で動作, バス幅16ビット

- 容量2Gb

データ通信

- 10Gbpsまで通信可能なGTXトランシーバを2つSFP+モジュールに接続。

- SiTCPおよびSiTCP-XGで通信可能。SiTCPは2つ実装可能であり、2リンクで通信可能。

メイン入力ポート

- 64ch差動入力, LVDS/ECLをサポート, HULと互換

メザニンスロット

- HULと互換のスロットを2つ搭載。HR-TDCなどHULの資産が利用可能。

- どうしてもIOを追加したい場合要に、差動1ペア、単一単2本が接続可能な小型メザニンスロットが上部に存在。

マスタークロック受信

- MIKUMARI link protocol

電源

- DC 35V(それよりも低くても可)

NIM I/O

- 入力x2, 出力x2

FPGA機能

- Skeleton [Github repository]

- Streaming low-resolution TDC [Github repository]

- 連続読み出しの1ns精度TDC

- Streaming high-resolution TDC

- 連続読み出しの23 ps精度TDC

- Str-HRTDC Base [Github repository]

- Mezzanine Str-HRTDC [Github repository]

- Mikumari ClockRoot [Github repository]

- Mikumari ClockHub [Github repository]

公開予定リソース

- 回路図(Open-Itメンバー以外で必要な場合は本多へ問い合わせてください)

- 基板開発のまとめ(Open-Itメンバーのみ)

- User guide

ハードウェア

AMANEQ(親基板)(GN-2006-4)

MIKUMARIを使ってクロックを受信する場合、GN-2006-1,2,3ではMini-mezzanine CRVを必要とします。

HUL用のmezzanine cardを利用することが可能です。

AMANEQ専用mezzanine cardのリスト

Mezzanine cardはHULと互換です。以下にはAMANEQ専用のものだけリストします。

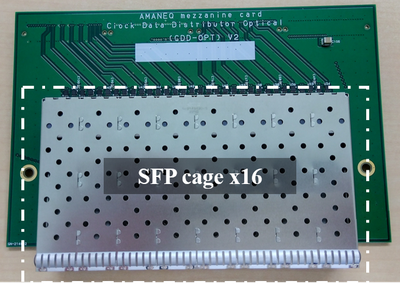

1. Clock-Data Distributer Optical (CDD-OPT) v2 (GN-2140-2)

MIKUMARIを使って複数の回路をクロック同期するための拡張カードです。

16個の光ファイバーモジュールを挿入可能であり、最大16台の下流モジュールを同期できます。

2スロット占有する大型メザニンカードです。

2. Mini-mezzanine Clock Receiver (CRV) (GN-2139-2)

古いバージョンのAMANEQ(GN-2006-1,2,3)がMIKUMARI経由でクロック同期を受ける際に必要な子基板です。

AMANEQ右上の小スロットに搭載します。

図・写真等

AMANEQの写真

VME 6Uサイズ基板であるがVMEであればバックプレーンとなる側に信号入力がある。

この関係からHULとはメザニンは180度反対に接続される。

Mezzanine card CDD-OPT v2の写真

AMANEQ専用メザニンカード。2スロットを占有する。

関連リンク

Open-It project, Hadron Universal Logic module

発表論文リスト

- J-PARCハドロン実験における連続読み出しDAQ用主回路, AMANEQの開発, 本多良太郎, 池野正弘, 庄子正剛, 髙橋智則, 日本物理学会2021年秋季大会, 16pV1-10 (pdf)

- Clock-duty-cycle-modulation (CDCM)を用いたクロック・データ伝送システムの開発, 本多良太郎, 日本物理学会2021年秋季大会, 17pT4-8 (pdf)

- R. Honda, IEEE TNS, vol. 70, no. 6, pp.1102–1109, Apr. 2023, doi: 10.1109/TNS.2023.3265698.