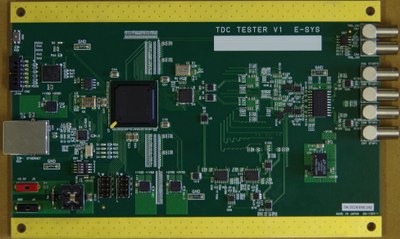

TDC Tester

メンバー

- 庄子 正剛(IPNS, KEK)PCB担当

- 濱田 英太郎(IPNS, KEK)FPGA担当

- 内田 智久(IPNS,KEK)

- 池野 正弘(IPNS,KEK)

- 田中 真伸(IPNS,KEK)

概要

TDCの性能評価を行なうTDCテスターを開発する。

既存のテスターと比べ、コンパクトで場所を選ばず簡単に利用でき、安価に作成可能となるものを開発する。

機能・特徴

動作概要

スタート信号とストップ信号を任意の時間差で、NIM出力する。時間差の設定は、指定されたカウント数と、カウンタの周波数によって定められる。

ブロック図

- 16bit counter

スタート信号とストップ信号用のために用意された2つの16bitカウンタ。それぞれのカウンタは、2つの8bitカウンタ(オン・セミコンダクター社, MC100EP016A)を用いて、16bitカウンタを形成している。あらかじめ、カウント数を設定する。「trigger logic」からCE信号等が送られたらカウントを初め、設定したカウント数に達したら、スタート信号またはストップ信号を出力する。また、ストップ信号を出力すると同時に、Stop in信号を「trigger logic」にDFFを通して出力する。

詳細は、こちら

- trigger logic

「FPGA」からトリガー信号を受け取ると、MR信号、CE信号、PE信号(カウントスタート処理に必要)を作り、「16bit counter」に送信する。

また、Stop in信号を受け取ると、MR信号、CE信号(カウントストップ処理に必要となる)を作り、「16bit counter」に送信する。

詳細は、こちら

- PLL分配器

800MHz、または800MHzを分周したクロック信号を「16bit counter」、「trigger logic」、「FPGA」に送信する。

クロックジェネレータには、アナログ・デバイス社のAD9517-4を利用している。このクロックジェネレータを用いることで、PLL(phase locked loop)が可能となり、周波数多様かつ安定したクロック信号をoutputできる。

詳細は、こちら

- FPGA

以下の機能を持つ

・カウンタの初期設定

・trigger入力

・外部trigger入力

・PLL clock(AD9517-4)レジスタ設定

・SiTCP(スローコントロール)

- ethernet

レジスタの設定値情報を「FPGA」にUDP通信する。

- NIM_IN

外部トリガー信号を「FPGA」にNIM入力する。

- DFF

入力信号の歪みやジッタ等を排除し、波形整形した信号を出力する。

公開予定リソース

発表論文リスト

- 2012年度 日本物理学会秋季大会 Belle II実験 Zero Degree Luminosity Monitor(ZDLM)のTDCモジュールプロトタイプ開発(PDF)

- 2012年度 日本物理学会年次大会 Belle II実験 ZDLM用時間計測システムの構築に向けたTDCモジュール開発(PDF)

関連リンク