PLL

メンバー

- 戸本 誠(代表:名古屋大学)

- 志知秀治(名古屋大学)

- 佐々木修(IPNS KEK)

- 田中真伸(IPNS KEK)

概要

PLL(Phase Locked Loop)は任意の周波数のクロックを作るための回路である。特徴として、温度変化や電源電圧の変化などの環境の変化に対してもその周波数が保証されることがあげられる。

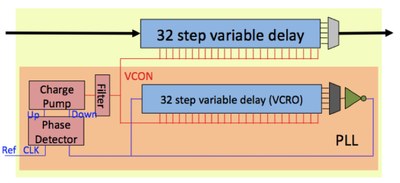

今回は遅延回路において遅延時間の保証としてPLLを用いた。また今後は任意の時間分解能を持つTDCなどへ応用が期待されている。用いたプロセスはUMC025である。

機能・特徴

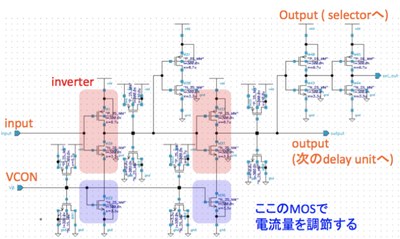

PLLは大きく、inverterによる発振回路とそれを制御する回路に分かれる。発振回路は図のように2つのinverterを1unitとして構成される。

これを任意の数つなげてselector + inverterを通してフィードバックすることで発振回路ができる。制御回路はその発振回路と、リファレンスとなるクロックの立ち上がり時間の差を比較し、inveterのGND側の電流量を調整し、1unitあたりの遅延時間を変化させる。

今回は発振回路と同じものを並べて、1unitあたりの遅延時間が保証された遅延回路として用いた。

リソース

- 回路図、レイアウト(NDA締結後オープン)

- 放射線試験データ(Open-It関係者に公開)

- プレゼンテーション等(合意がとれた物を公開する予定)

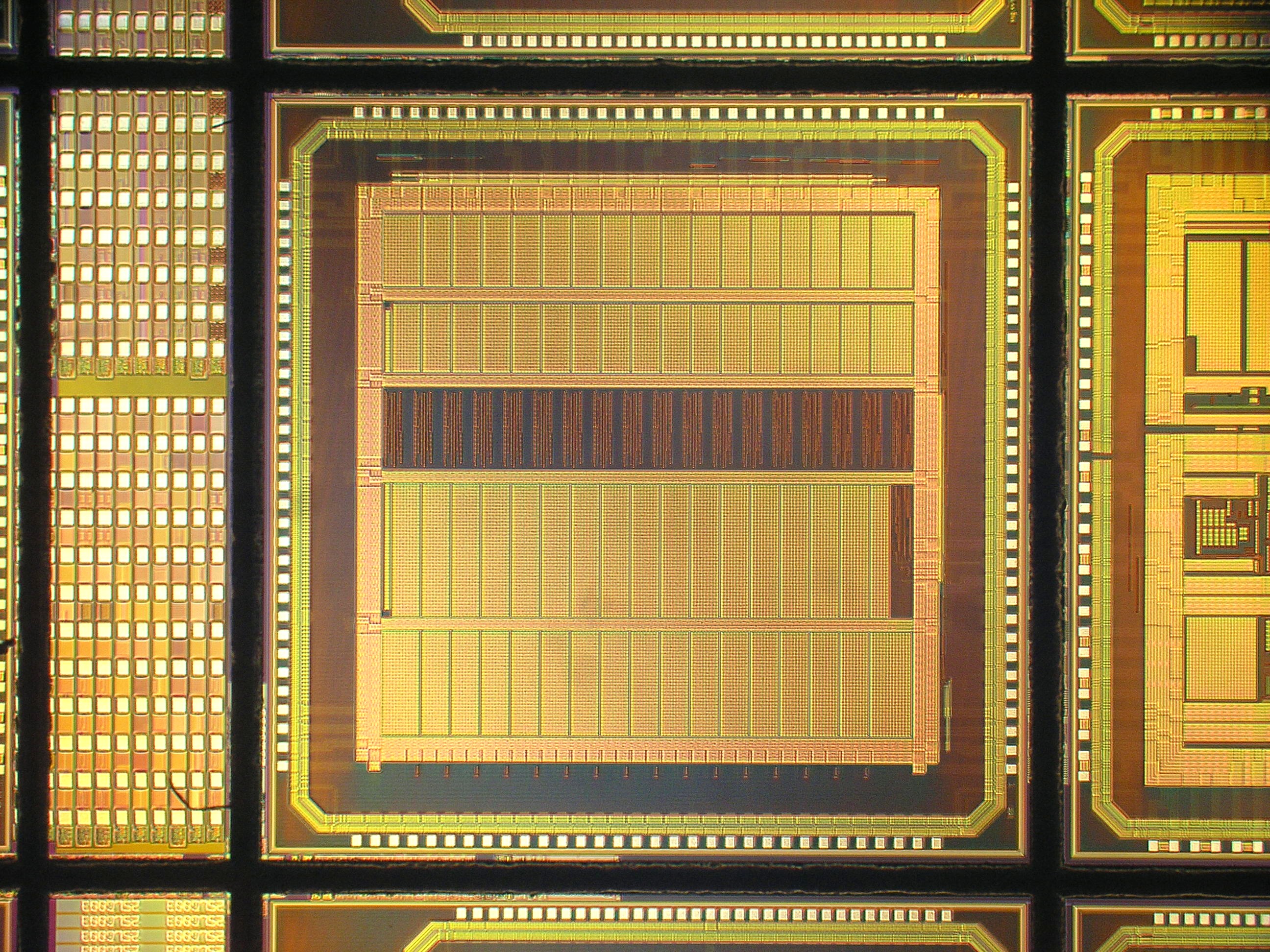

図・写真等

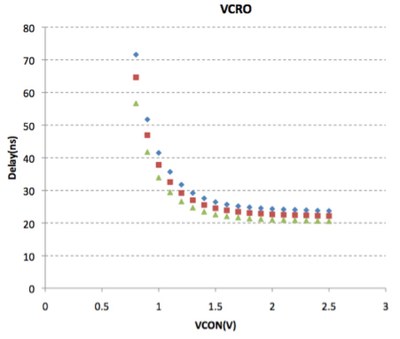

測定結果。横軸が電流量を調整するための電圧、縦軸が遅延回路の遅延時間。遅延時間にはプローブなどの伝播遅延が含まれているので、遅延回路単体での遅延時間は最小15ns程度。

関連リンク

発表論文リスト

2011/1/24 名古屋大学修士論文 志知秀治 ”ATLAS実験のアップグレードに向けた高放射線耐性を持つmu粒子トリガー回路系ASICの開発研究"(インターナル)