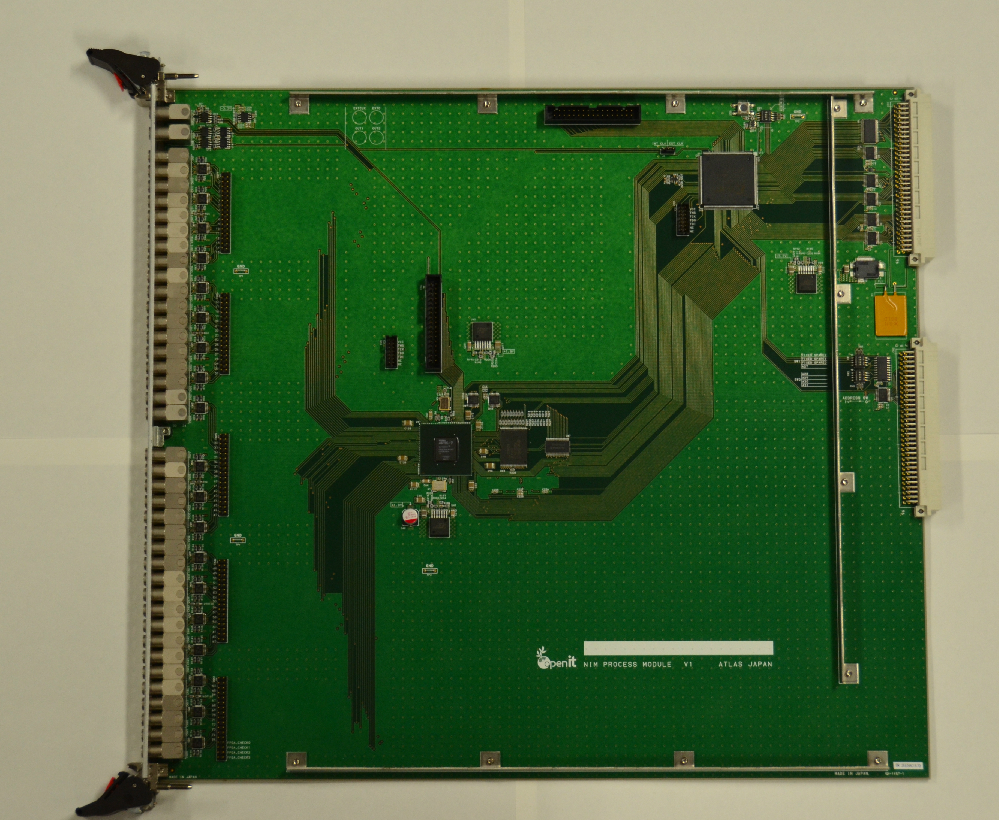

汎用多チャンネルNIM論理回路モジュール

概要

多チャンネルのNIMシグナルINPUTの汎用論理回路ボードの開発。ATLASエンドキャップミューオン検出器TGCにおいてRun-2から導入されている信号処理回路。

メンバー

- 前田順平, Maeda Junpei (代表、神戸大)

- 鈴木翔太, Suzuki Shota* (総研大 D2)

- 救仁郷拓人, Kunigo Takuto* (京大 D2)

- 池野正弘, Ikeno Masahiro (IPNS KEK)

- 佐々木修, Sasaki Osamu (IPNS KEK)

- 石野雅也, Ishino Masaya (京大)

機能・特徴

- VMEスレーヴモジュール (9U サイズ)

- NIMシグナル、76チャンネルのLEMOタイプのINPUTを搭載

- FPGAを搭載し、論理計算したNIMシグナルを出力 (2チャンネル)

- CPLDによりVME制御、FPGAのコンフィギュアが可能

- BPIメモリを搭載。FPGAの高速コンフィギュアが可能

- 内部クロック (CMOS 40.08MHz) の他、外部クロックサポート

公開リソース

- 論理回路ボードの仕様書: PDF

- 回路図、レイアウト図 (Open-It memberのみ。他要問合せ)

- CPLDのHDLデザイン: CPLD.tar.gz (Open-It memberのみ。他要問合せ)

- FPGAのHDLデザイン例: FPGA.tar.gz (Open-It memberのみ。他要問合せ)

図・写真等

関連リンク

発表論文・学会リスト

- 救仁郷拓人 他, LHC-ATLAS実験 Run 2におけるレベル1ミューオントリガー改良のハードウェアへの実装, 日本物理学会 2014年秋季大会