TDC

メンバー

- 戸本誠(代表:名古屋大学)

- 堀井泰之(名古屋大学)

- 臼井主紀(名古屋大学)

- 小野木宏太(名古屋大学)

- 佐野祐太(名古屋大学)

- 佐々木修(IPNS KEK)

- 田中真伸(IPNS KEK)

- 田内一弥(IPNS KEK)

概要

高エネルギー素粒子実験において、時間測定はドリフトチェンバーを使用した荷電粒子トラッキングシステム、シンチレータ等を用いたTOFシステムにおいて非常に頻繁に使用される。我々は2010年度PLLを用いた数百psec~1nsec間隔遅延調整集積回路を開発し放射線環境下での動作試験等行いsLHCにおいて使用可能なことを確認した。2011年度からこのPLL等を用いTDC(Time to Digital Converter)の研究開発を行う。複数のPLL,DLL等の回路構成を比較検討し100psec未満の時間分解能を持つTDCに必要な条件等を洗い出す。

資料

- 臼井主紀, 小野木宏太, 「Phase Locked Loop回路を用いたTDCの開発」, 高エネルギー物理春の学校, 2013年5月: スライド

- 小野木宏太, 他, 「Phase Locked Loop回路を用いたTDCの開発」, 計測システム研究会, 2013年7月: スライド

- 小野木宏太, 他, 「Phase Locked Loop回路を用いたTDCの開発」, 若手研究会, 2013年10月: スライド

- 臼井主紀, 他, 「0.18プロセスPLL開発の現状」, 若手研究会, 2013年10月: スライド

- 小野木宏太, 他, 「Phase Locked Loop回路を用いたTDCの開発」, 日本物理学会, 2014年3月: スライド

- 臼井主紀, 他, 「PLL回路の最適化とTDCへの応用」, 日本物理学会, 2014年9月: スライド

- 臼井主紀, 「位相同期回路を用いた汎用タイムデジタイザの開発」, 修士論文, 2015年2月: 論文, スライド

- 臼井主紀, 他, 「最適化した位相同期回路を組み込んだタイムデジタイザの開発」, 日本物理学会, 2015年3月: スライド

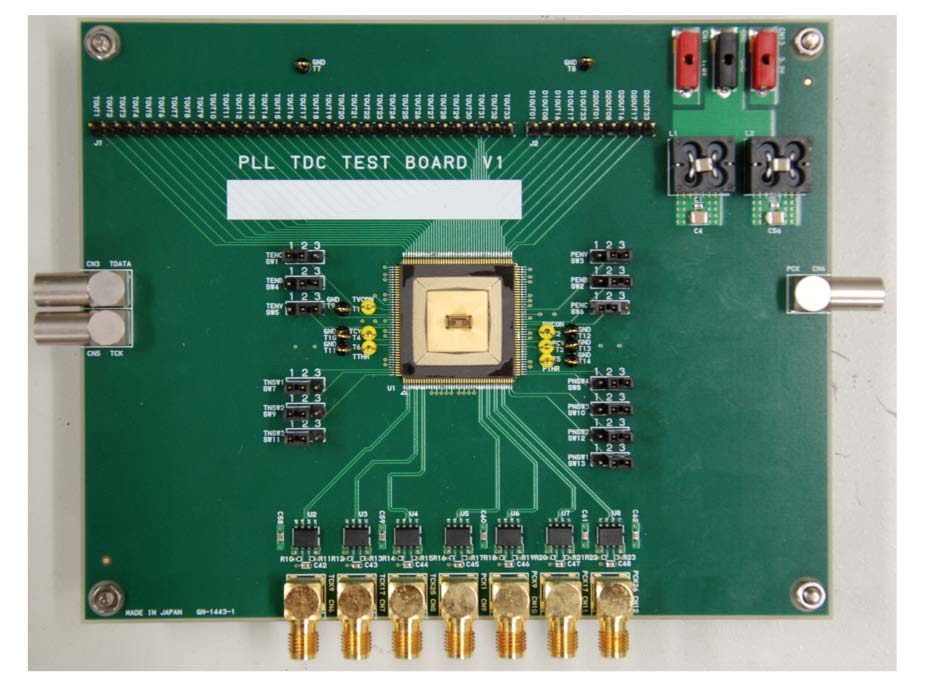

図・写真等

関連リンク

発表論文リスト

1.2015 Master 名古屋大学 臼井主紀 「位相同期回路を用いた汎用タイムデジタイザの開発」