シリコンストリップ読み出しアナログ回路

概要

高速シリコンストリップ検出器デジタル読み出し用多チャンネルアナログ回路の開発

プロセスはCMOS0.25um,CMOS0.18umを使用した。

本プロジェクトはSliT128Aへ引き継がれ、アナログ回路部分は微修正後使用。

メンバー

- 田中真伸,Tanaka Manobu(代表:高エネルギー加速器研究機構、素粒子原子核研究所)

- 上野 一樹(IPNS, KEK)

- 古浦 新司(九州大)

- 調 翔平(九州大)

- 東城 順治(九州大)

- 三部 勉(IPNS, KEK)

- 佐々木 修(IPNS, KEK)

- 高力 孝(IPNS, KEK)

- 内田 智久(IPNS, KEK)

- 池野 正弘(IPNS, KEK)

- 池田 博一(JAXA)

機能・特徴

シリコンストリップ用アンプシェーパーディスクリミネータ集積回路

CMOS 0.25um

検出器容量:30pF以下推奨

検出器容量:30pF以下推奨

極性:p-side,n-side切り替え

コンバージョンゲイン:20mV/fC

ピーキングタイム:〜50nsec(可変)(パルス幅〜100nsec)

ENC:〜2400@30pF

ピーキングタイム:〜50nsec(可変)(パルス幅〜100nsec)

ENC:〜2400@30pF

出力:アナログモニター(切り替え)、10pF負荷ドライブ可、デジタル(全チャンネル)

チャンネル数:32ch

チャンネル数:32ch

CMOS 0.18um

検出器容量:30pF以下推奨

極性:p-side

コンバージョンゲイン:30mV/fC

ピーキングタイム:〜30nsec(可変)(パルス幅<100nsec)

ENC:<2000@30pF

ピーキングタイム:〜30nsec(可変)(パルス幅<100nsec)

ENC:<2000@30pF

出力:アナログモニター(切り替え)、10pF負荷ドライブ可、デジタル(全チャンネル)

チャンネル数:64ch

チャンネル数:64ch

公開予定リソース

NDAを締結後、回路図、レイアウトを公開

図・写真等

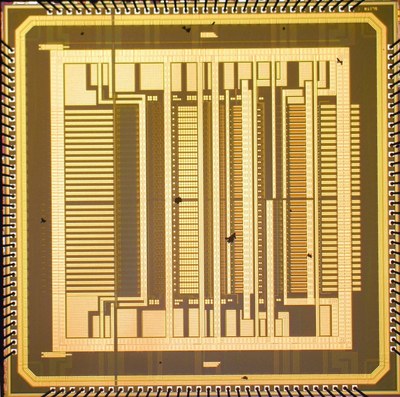

UMC 0.25um プロセス

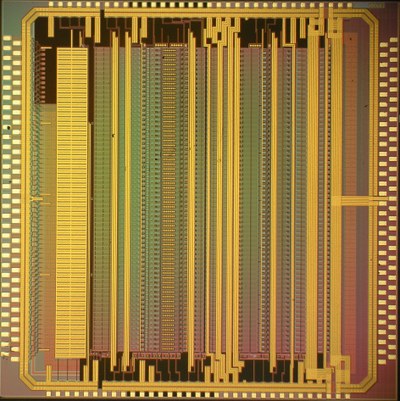

Silterra 0.18um プロセス

関連リンク

発表論文リスト

- 「J-PARC ミューオンg-2/EDM実験:シリコンストリップ検出器用ASICの性能評価」、日本物理学会第69回年次大会、調翔平他 2014年3月3日

- 「J-PARC ミューオンg-2/EDM実験:シリコンストリップ検出器用読み出し回路の要求性能」、日本物理学会第69回年次大会、古浦新司他 2014年3月30日

- 「J-PARC ミューオンg-2/EDM実験:シリコンストリップ検出器用ASICの性能評価 」、20th ICEPP Symposium、調翔平他 2014年2月26日

- 「Fast Readout ASIC for Si-Strip Detector in the J-PARC Muon g-2/EDM Experiment and Other Related Applications」、IEEE NSS 2013、K. Ueno, et al、2013年10月30日

- 「J-PARC g-2/EDM実験:シリコントストリップ検出器用ASIC開発-デジタル部」、日本物理学会第68回年次大会、内田智久他 2013年3月26日

- 「J-PARC g-2/EDM実験:シリコントストリップ検出器用ASIC開発-アナログ部」、日本物理学会第68回年次大会、上野一樹他 2013年3月26日

- 「J-PARC muon g-2/EDM実験のための検出器開発」、計測システム研究会、上野一樹他 2012年11月5日

- 「g-2実験用シリコンストリップトラッカーASIC(SliT)開発」、日本物理学会第67回年次大会、田中真伸他 2012年3月27日