High rate MPPC readout evaluation

概要

J-PARC E50実験用ではMPPC読み出しのscintillation fiber trackerを採用予定である。

多チャンネルMPPC読み出しには専用のfront-end ASICが必要であり、候補としてOmegaグループによって開発されたCITIRO/PETIROC2を考えている。これらのASICはOpen-Itプロジェクトでも度々用いられているEASIROCの後継版である。

本実験は大強度のパイオンビーム(30 MHz)を使用予定で、fiber trackerにおいても最大で1 MHz/MPPCのレートが見込まれる。

J-PARCE50実験では連続読み出しDAQの導入を予定しており、全ヒットへの時刻情報付与とPCへの転送が必要である。

多チャンネルMPPC読み出しには専用のfront-end ASICが必要であり、候補としてOmegaグループによって開発されたCITIRO/PETIROC2を考えている。これらのASICはOpen-Itプロジェクトでも度々用いられているEASIROCの後継版である。

本実験は大強度のパイオンビーム(30 MHz)を使用予定で、fiber trackerにおいても最大で1 MHz/MPPCのレートが見込まれる。

J-PARCE50実験では連続読み出しDAQの導入を予定しており、全ヒットへの時刻情報付与とPCへの転送が必要である。

ASICの制御や性能試験だけでなく、連続読み出しのノウハウ蓄積のためにもこの基板を利用する。

メンバー

- 本多良太郎(代表:大阪大学・特任研究員)

- 白鳥昂太郎(RCNP,助教)

- 高橋智則(RCNP,技術補佐)

- 池野正弘(KEK 専任技師)

- 内田智久(KEK 准教授)

機能・特徴

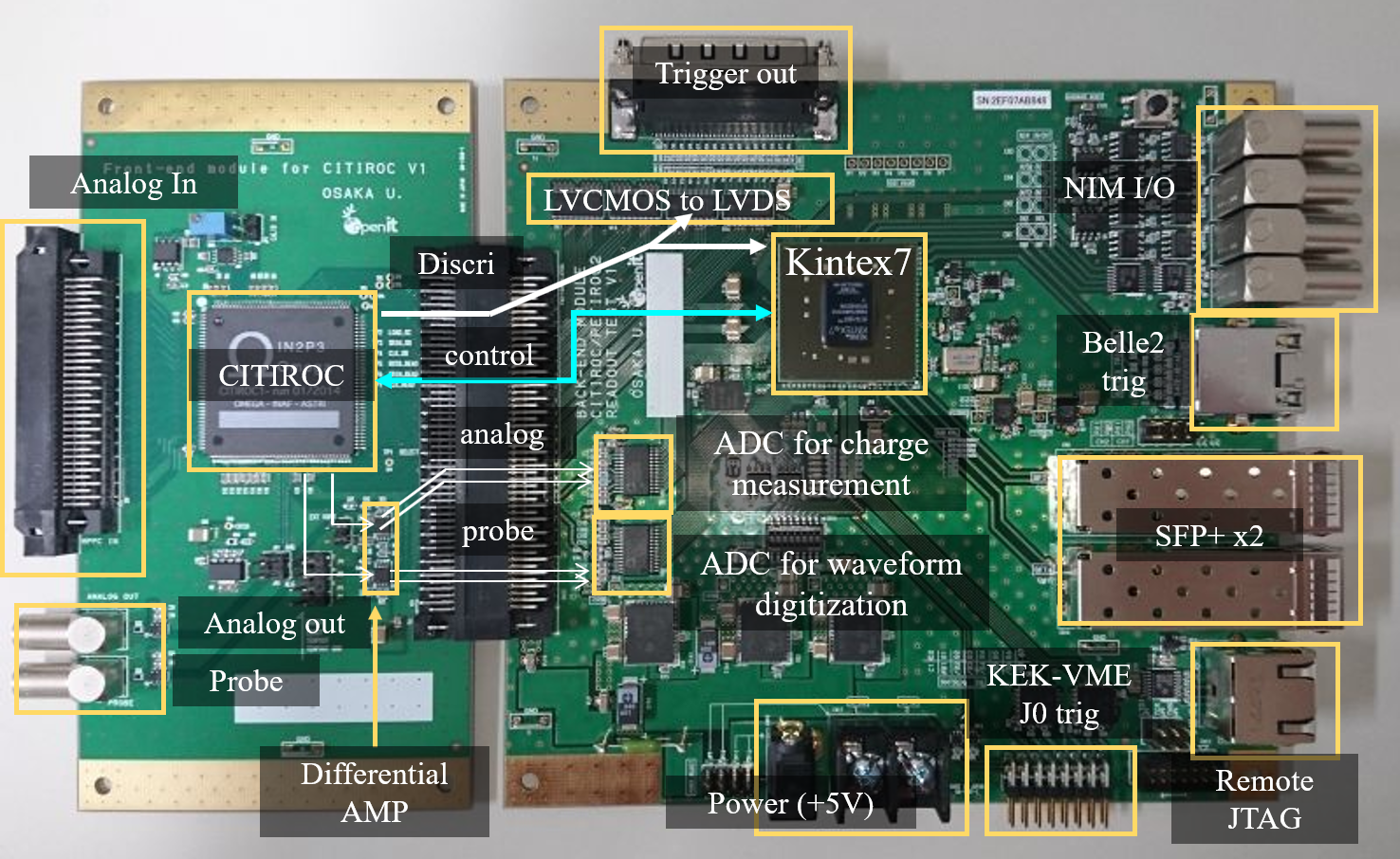

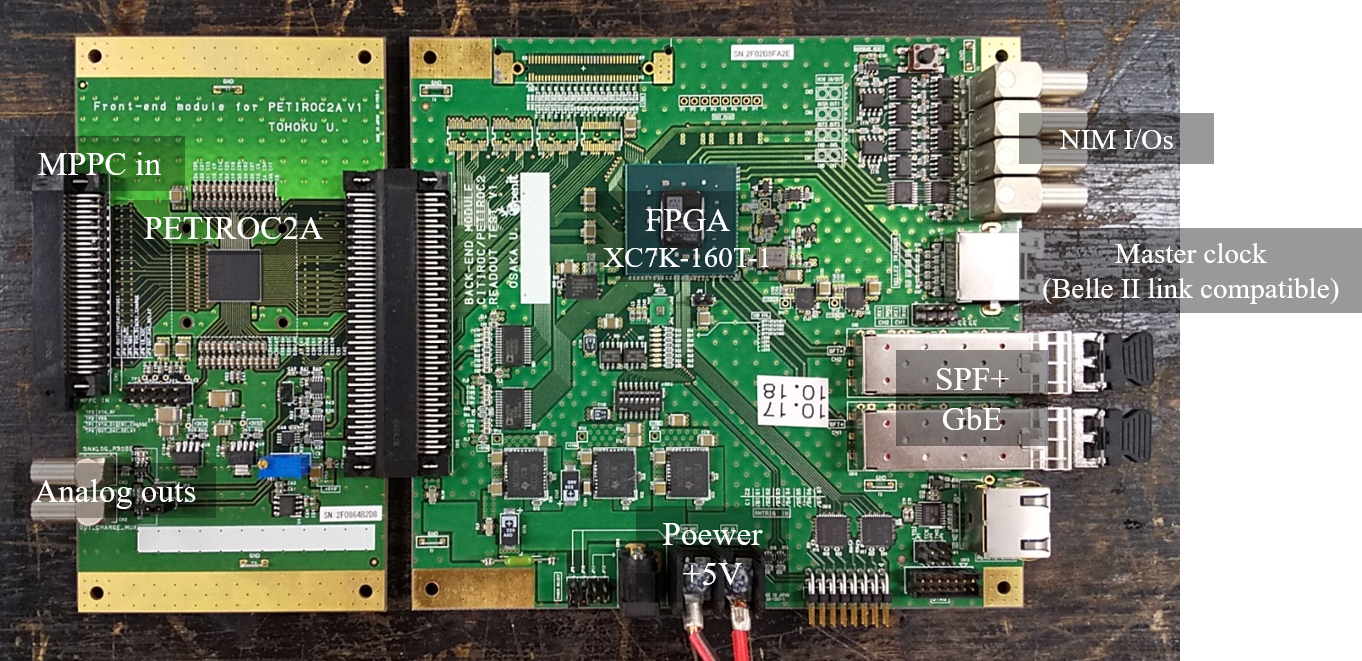

CITIROC1AとPETIROC2Aは両方ともOmega製のASICであるがピンコンパチではないため、アナログ基板は2種類作成する必要がある。

そのため、アナログボードとデジタルボードに分けて基板を製作し、アナログボードを付け替えることでASICを使い分けるようにする。

デジタルボードにはKintex7 (XC7K-160T-1-FBG676) を搭載し、SFP+モジュール2つをGTXトランシーバへ接続する。

デジタルボードにはKintex7 (XC7K-160T-1-FBG676) を搭載し、SFP+モジュール2つをGTXトランシーバへ接続する。

SiTCPを2つ実装して最大2Gbpsの通信速度を確保し、連続読み出しDAQの試験を行えるようにする。

またRJ45とフラットケーブルコネクタ両方を実装しBelle2 trigger portとcopper triggerの両方の試験を行えるようにする。

またRJ45とフラットケーブルコネクタ両方を実装しBelle2 trigger portとcopper triggerの両方の試験を行えるようにする。

原則クロック同期はBelle2 triggerポートから行う。

電源は+5Vの単電源とする。

FPGAはCITIROC1AおよびPETIROC2の制御を行う。また時間精度1nsのTDCの用いてASICからのdiscriminator信号をデジタイズする。

電源は+5Vの単電源とする。

FPGAはCITIROC1AおよびPETIROC2の制御を行う。また時間精度1nsのTDCの用いてASICからのdiscriminator信号をデジタイズする。

連続読み出しDAQを用いる場合、各ヒットがJ-PARCハドロンの遅い取り出し時間 (2秒) のどの時点のヒットであるあるかを再構成しかえればならない。

そこで、FPGA内部でheartbeatと呼ばれる特殊データを500μ秒周期で生成し、データ列へ混ぜ込むことでスピル開始からの時刻を調べる。

本回路ではCITIROC1AおよびPETIROC2Aの制御・アナログ性能を調べることと、上記連続読み出しにおける時間再構成について知見を蓄積することが目的である。

公開予定リソース

回路図等

- 回路図 (Open-Itメンバー以外の方はEsys本多へご相談ください。)

- CITIROC1Aアナログ

- CITIROC1Aのアナログ基板には設計ミスがあり、電源カップリングが起きています。そのままコピーはしないようお願いします。

- PETIROC2Aアナログ

- デジタル基板

- CITIROC1Aアナログ

- 基板図はEsys本多へご相談ください。

FPGA FW

以下の事がこれまで達成できています。この回路はASIC試験と連続読みだしTDCの試験が用途のため、物理実験で使えるレベルのFWは開発されていません。

蓄積したノウハウの共有は喜んで行いますので、何かあればEsys本多へご相談ください。

- CITIROC1Aの制御

- PETIROC2Aの制御

- 連続読み出しTDCの実装。

- Heartbeat法による時間再構成。

- 2つのSiTCPによる負荷分散。2 Gbps読み出し。

図・写真等

CITORORC1Aアナログボードとデジタルボードを接続した図。

PETIROC2Aとデジタルボードを接続した図。

関連リンク

発表論文リスト

荒巻 昂, 2020年 東北大学 修士論文, pi-p → K*0(892)Λ反応を用いたΛp散乱実験におけるシンチレーションファイバー飛跡検出器および読み出しシステムの開発, https://lambda.phys.tohoku.ac.jp/strangeness/gakui_ronbun-j.html#M_thesis