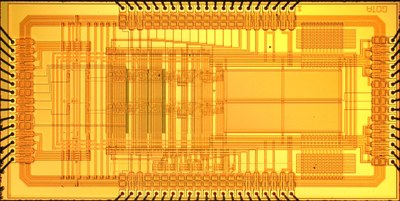

HBD trigger ASIC

概要

J-PARC E16実験の電子識別triggerのため、HBD検出器のGEMフォイル信号読み出しのフロントエンドとして、大入力容量に対応したハイレート耐性・低ノイズ読み出しASICを開発する。

メンバー

- 四日市 悟(代表, 理研仁科センター 専任研究員)

- 小原 裕貴(東京大学)

- 菅野 光輝(東京大学/理研仁科センター)

- 鈴木 一輝 (京都大学)

- 小沢 恭一郎(KEK 准教授)

- 森野 雄平 (KEK 助教)

- 田中 真伸 (KEK 教授)

機能・特徴

HBDのsignalをチャージアンプで増幅し、comparatorでトリガー用のデジタル信号

として読み出しを行う。

検出器側の容量、10nFに対応し、時定数 1micros程度、 3fC程度の入力に対して

thresholdをかけられるような、

ハイレート耐性・低ノイズ読み出しASICを開発を行う。

公開予定リソース

NDAを締結後回路図、レイアウト等

図・写真等

関連リンク

発表論文リスト