Cold readout electronics for liquid argon TPC detector

メンバー

- 長谷川 琢哉(IPNS,KEK)

- 坂下 健(IPNS,KEK)

- 田中 真伸(IPNS,KEK)

- 内田 智久(IPNS, KEK)

- 池野 正弘(IPNS, KEK)

- 千代 浩司(IPNS,KEK)

- 中村 正吾(横浜国立大学)

- 岩崎 裕也(横浜国立大学)

現在、次世代ニュートリノ振動実験のための検出器として、位置分解能の高い3次元飛跡検出器である液体アルゴンTPC(Time projection chamber)を用いることが検討されている。ニュートリノの検出器には、スーパーカミオカンデ級の巨大スケールの検出器が必要であるため、液体アルゴンTPCを巨大化するための複数の要素の開発が必要不可欠になっている。その中でもニュートリノ事象の微小な信号の読み出しを可能にし、さらに検出器の製造コストを下げるために、読み出し回路は非常に重要な要素となっている。

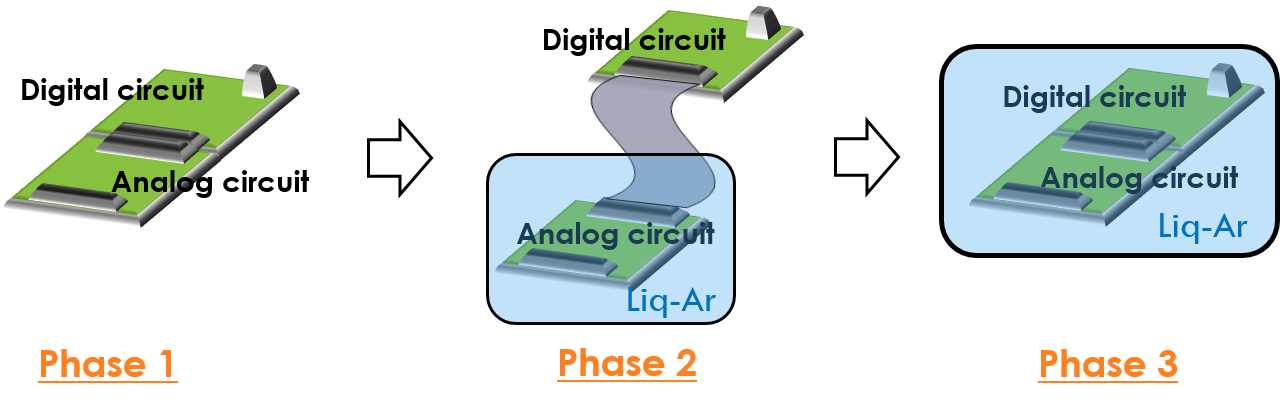

液体アルゴンTPCの読み出し回路に求められる仕様として、低ノイズかつ高ゲイン、さらに多チャンネル化等があり、これらの仕様を実現するための方法の一つとして、読み出し回路をチェンバー内に設置する方法が提案された。しかしチェンバーは液体アルゴンで満たすため、読み出し回路は液体アルゴン温度(−185℃@1atom)で動作する必要がある。そこで低温下で動作する事を目標として、読み出し回路が段階的なプロセスを踏んで開発されている。

本プロジェクトではその初段階、DAQシステムの確立と十分に高いSN比を達成する事を第一目標として、常温用の読み出し回路を開発した。加えてデータ取得用プログラム等の開発を行い、最後に全体のDAQシステム評価のための宇宙線データの取得試験を行った。

開発プロセス

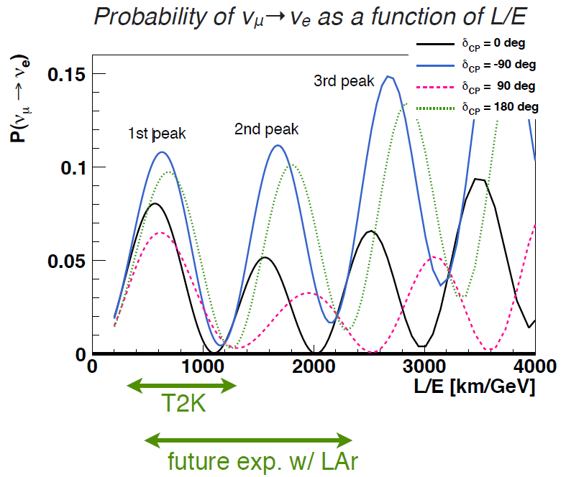

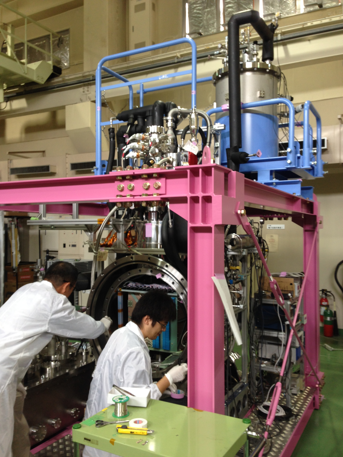

液体アルゴンTPCを用いてニュートリノビームを測定する長基線実験として、隠岐の島に液体アルゴンTPCを置く案が考えられている。この案では東海村J-PARCからのニュートリノビームを隠岐の島の液体アルゴン測定器で検出する。これは神岡へニュートリノを飛ばすT2K実験の次期計画であり、神岡~東海村間の295kmに比べて、ニュートリノを658kmという長距離間飛ばすことにより、ニュートリノの振動現象から、レプトンセクターでのCP対称性の破れの証明などの宇宙創世期の謎にも踏み込める可能性がある 。この長基線実験には100ktonクラスの大型の検出器が必要となるが、その実現には様々な技術開発が必要である。そのため、世界各国で将来の大型化に向けた開発研究が多角的に進められている。高エネルギー加速器研究機構(KEK)のニュートリノグループも液体アルゴン重量で0.4tonと15kgのプロトタイプ測定器2つを開発し、それらを利用して将来の大型化に向けた様々な研究開発を行っている。

次世代ニュートリノ振動実験

液体アルゴンTPC検出器はTPC(Time Projection Chamber)という原理で荷電粒子の飛跡を検出する、1相式(液相のみ)の検出器の概略図を図に示す。TPCは上面がアノード(2次元電極PADもしくはワイヤー読み出し)、下面がカソードとなっており、カソードに高電圧を印加し、TPC内に一様な電場を形成できるようになっている。TPCチェンバー内に荷電粒子が入射すると、液体アルゴンと反応し電離電子が生成される。発生した電離電子は電界によりドリフトして、やがてアノードへ達成する。この時の電離電子信号を読み出すことで、粒子飛跡の2次元情報を取得する。またチェンバー内に入射した荷電粒子は液体アルゴンを励起し128nmのシンチレーション光も発生させる。TPCにPMTを設置して、シンチレーション光を検出しトリガーとして利用すれば、電離電子のドリフト時間情報を取得することが出来、2次元飛跡情報と合わせることで、荷電粒子の3次元飛跡再構成が可能である。

液体アルゴンTPCの概念図

液体アルゴンTPCの特徴として高い位置分解能で3 次元的に飛跡を再構成できることと、その電気信号の大きさから通過した荷電粒子のエネルギー損失を測定できること等が挙げられる。それにより飛跡を再構成できることで多重事象と信号量の大きい事象とを識別することが可能になり、またカミオカンデなどの水チェレンコフでは判別が難しい背景事象π0(pi0) を伴うニュートリノ反応事象との識別が容易になる他、単位距離あたりの荷電粒子のエネルギー損失量dE/dx を知ることができるため粒子同定能力が高いという特徴がある。その他にもチェレンコフ光が出にくいK粒子や陽子などの重い粒子の飛跡検出も全く問題がなく行う事ができる。以下の図に日本の0.4ton液体アルゴンTPCチェンバーにテストビームを入射した際の、イベント図を載せる。図を見るとチェンバーを通り抜けるPion、電子シャワーを起こすPositron、散乱断面積が大きく、すぐに止まってしまうProtonのように、飛跡情報により粒子の区別が出来ることが分かる。

0.4ton液体アルゴンTPCとそのTextbook event

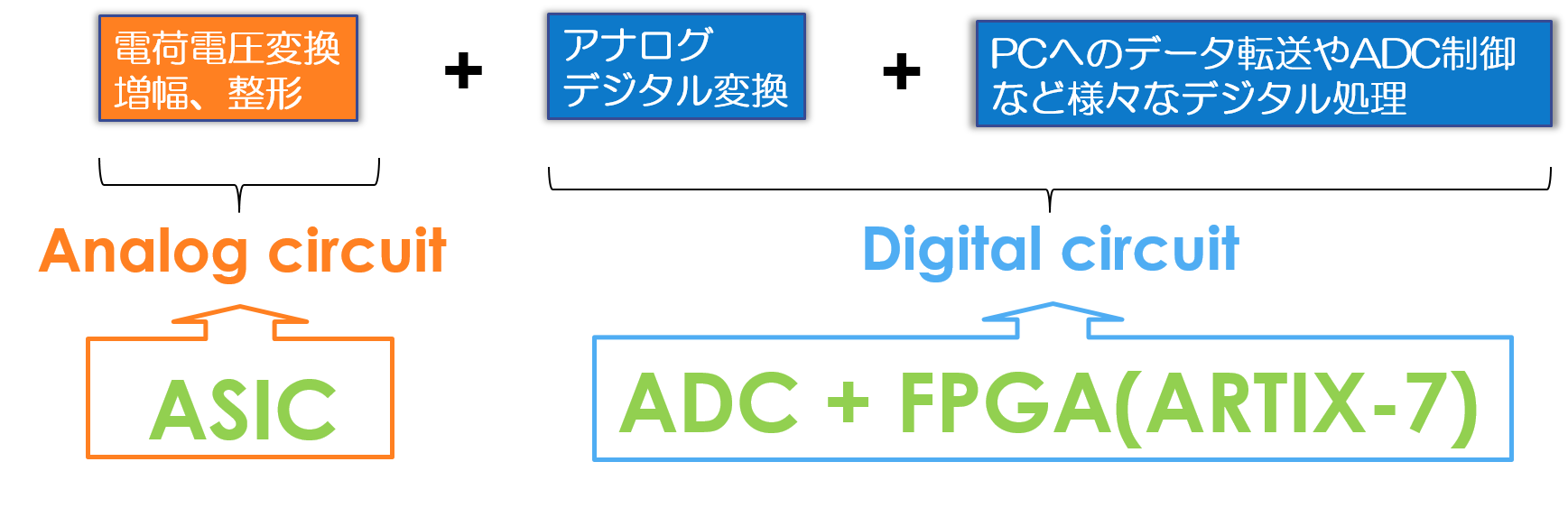

検出器からの数fCという微小電荷信号は、扱いやすい電圧信号に変換させるため、電荷有感型増幅器により電荷電圧変換する必要がある。その後増幅、波形整形という処理を行った後、ADCによってデジタル信号に変換する。そしてこのデータを最終的にPCに転送するが、この時PMTがシンチレーション光を検出した時のみ1イベント分のデータ転送を行いたいため、外部NIMトリガー信号を処理できるようにする必要がある。またPCとのデータ通信はTPC通信にて行う事もあり、TPC通信機能やイベント分のADCデータを保持するためのバッファ機能が必要となる。さらにシンチレーション光が発生したその瞬間からのデータが必要であるが、回路が外部トリガー受信してからのADCデータでは少し遅い。よって外部トリガーの受信より少し以前のADCデータを取得するために、データディレイ機能などを実装する必要がある。

第一に多チャンネルかつ微小な電気信号を処理する必要があるが、そのような高ゲイン低ノイズのアンプを汎用の部品で構成する事は難しい、そこで液体アルゴンTPC用にAnalog ASIC(LTARS)が開発され、今回はそのASICを採用した。第二にPCへのデータ転送のために、アナログ信号をADCによってデジタル変換するためのADCを実装した。第三にPCとのデータ通信やADCの制御、その他のデジタル処理を行うためには、デジタル回路を実装する必要がある。しかし多チャンネルの信号を扱うため、マイコンなどではピン数が少ないし、規模が小さい。また独自のデジタルICを開発するのは時間やコスト面で効率が悪い。そこで今回は、PCで自由にデジタル回路を書き込む事が出来、様々な規模、ピン数のラインナップがあるFPGAを採用した。最後に、読み出し回路全体の機能をアナログ部とデジタル部で分け、それぞれAnalog boardとDigital boardを開発するが、両基板は直接接続できるようなコネクタを実装する。開発の第二段階ではAnalog boardとDigital boardを離して設置するため、これを見越し、コネクタを変更することで両基板をケーブル接続できるような自由度を与えておいた。

構成概要

- 全32channel

- 最小信号は2fC、最大信号70fC程度を想定

- 最小信号に対してSN比が10以上

- 検出器容量は100pF程度を想定

- ADCは2.5MHz sampling、12bit resolution

- 外部トリガー入力

- 1イベントデータ数4000samples/ch

- 0 ~ 4000samplesのデータディレイ機能

- SiTCPを利用したデータ転送機能

- Analog board、Digital board間は差動信号で取り扱う。

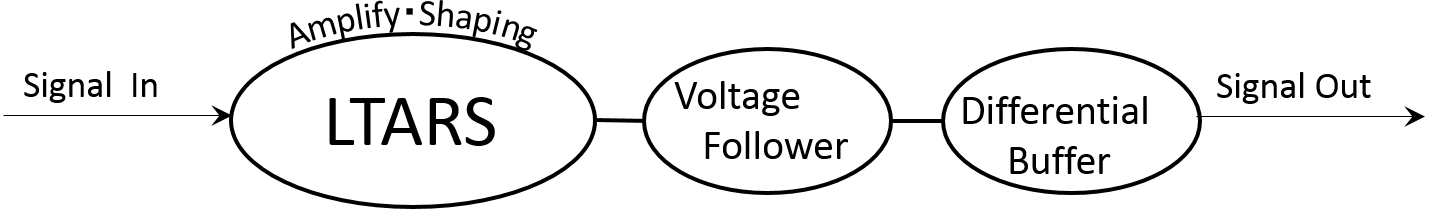

Analog boardは、電荷読み出しPADからの微小電荷信号を電荷電圧変換し、増幅整形する。さらにその信号を差動信号としてデジタルボードに転送する。よって全体の構成は以下の図のようになる。

Analog boardの構成

Analog boardは、電荷読み出しPAD全32channelの信号をそれぞれ処理するめASICは4個使用する。なおASICはLTARSを採用した。なおVoltage FollowerはLTARSがDifferential Bufferの入力抵抗をドライブ出来るほどの能力がないために使用している。

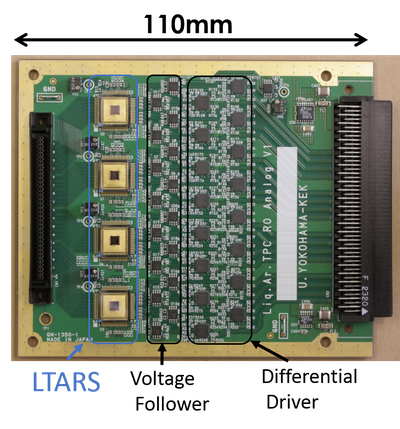

実際に開発したボードの写真を以下に示す。

- I/F INPUT: 8830E-068-170S-F

- Power ±3.3V

- Size 92mm × 110mm

寸法は横110mm、縦92mmであり、部品点数の多さから考えても集積度の高い基板となった。一番左側の計4個のICがLTARSである。その右隣の小さい計16個のICがボルテージフォロワのOPampであり、さらにその右隣の計16個のICが差動OPampである。電源は±2.5Vを使用するため、コネクタピンの一部から入力した±3.3Vを基板上に実装したレギュレータによりそれぞれ±2.5Vに落としている。最終段の差動信号は1ch分ペア配線の長さ、間隔等を揃えた。なおその他の配線も基本が集まっている箇所も基本的に間隔を揃えてある。またノイズ対策としてGNDスルーホールを基板の端に等間隔にあけてある。

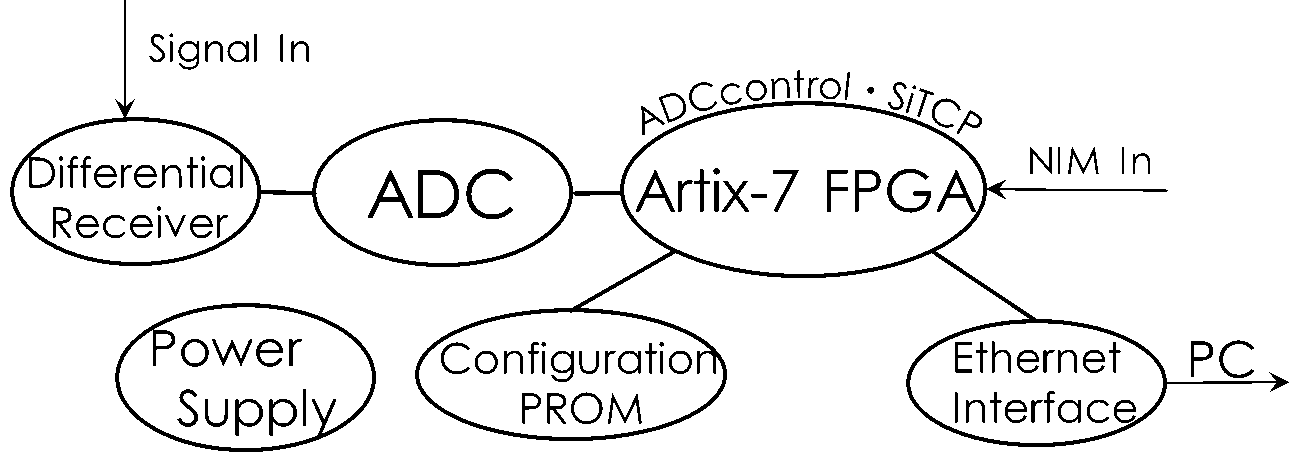

Digital boardはAnalog boardからの差動信号を受けて、アンチエイリアスフィルタを掛けたのち、ADCにて信号のアナログデジタル変換を行う。取得した信号のデジタルデータは、PMTからのトリガー(NIM信号)がONになると同時に、TCP通信によってPCに転送される。Digital boardの構成は以下の図のようにした。

Digital Board構成

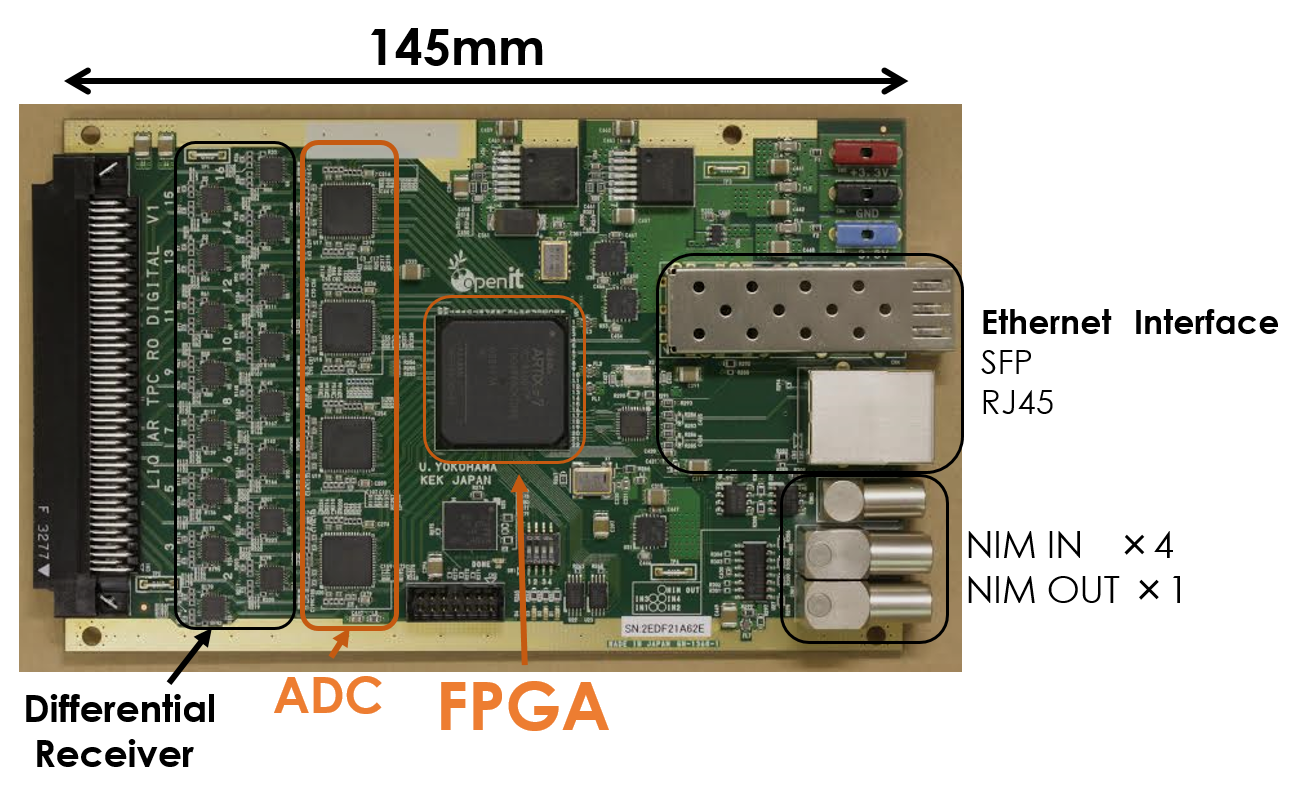

開発したDigital Boardの写真

- I/F INPUT: 8831E-100-170L-F ( 32ch Differential Signal , 2V p-p differential Input voltage range )

- ADC AD9637BCPZ-40: 12-Bit , 10 ~ 40MSPS , 0 ~ 2.0Vp-p Range

- FPGA Artix-7(xc7a100t-1fgg484c)

- Power ±3.3V

- Size 92mm × 145mm

- Other LED 4ch , DIP switch 4ch

寸法は横145mm、縦92mmであり、非常に小型で集積度の高い基板となった。一番左側の16個のICが差動OPampであり、その隣に4個のADCが実装されている。そして中心の一番大きなICがArtix-7(FPGA)である。電源は±3.3Vを右上のピンから入力し、基板上に実装したレギュレータにより様々な電圧に落としている。外部IFとしてSFPコネクタ、RJ-45コネクタ、LEMOコネクタ(IN:4口、OUT:1口)を右端に実装している。その他にFPGA書き込み用のJTAGコネクタ、汎用DIPスイッチ、汎用LEDなど実装されている。初段の差動信号やADCとFPGA間の差動LVDSは1ch分ペア配線の長さ、間隔等を揃えた。なおその他の配線も基本が集まっている箇所も基本的に間隔を揃えてある。またノイズ対策としてGNDスルーホールを基板の端に等間隔にあけてある。

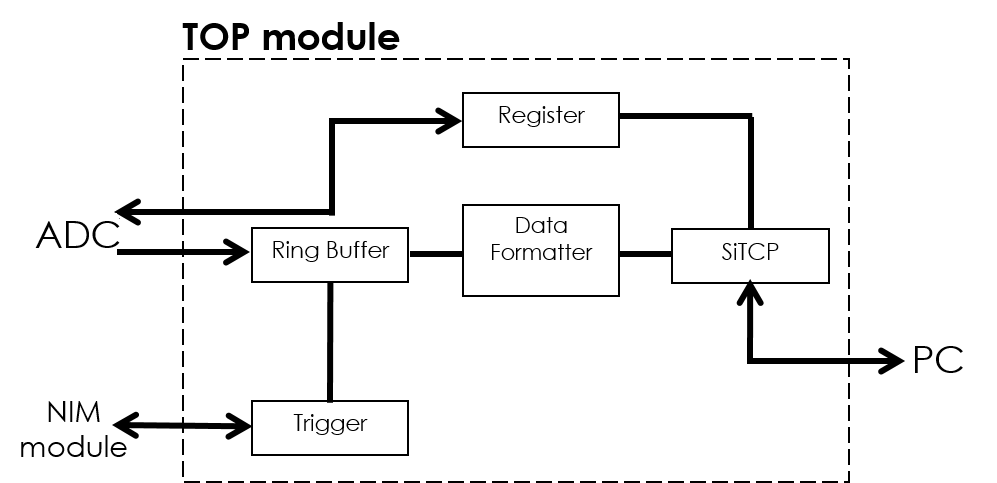

Digital boardではADCとのデータ通信(高速シリアル通信)や制御(SPI通信)、またデータのバッファやディレイ、そしてPCとのTPC通信や外部トリガーの信号処理など様々なデジタルの機能が必要となる。今回は基板にFPGAを実装し、FPGAで必要なデジタル回路を構成することにした。以下に今回開発したデジタル回路の仕様を示す。

- ADCからの高速シリアル通信

- 2.5MH sampling, 12bits resolution

- 1eventごとPCにデータを転送する

- 1eventごとに4000sample/chのデータ取得

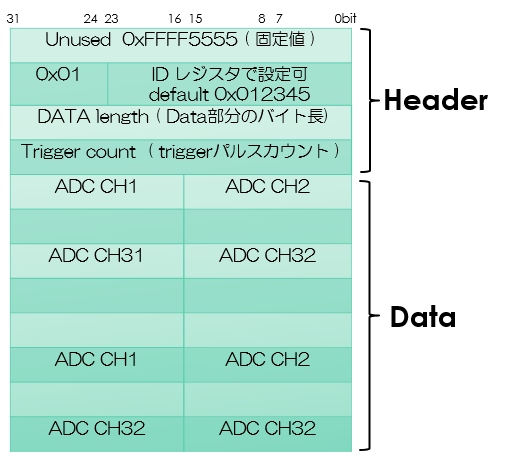

- 取得したADCデータを決められたフォーマットへ変換

- PCへのデータ転送にはTCP通信(SiTCP技術を利用)

- FPGA、ADCの制御にはUDP通信(SiTCP技術を利用)

- 外部トリガーの処理

- トリガーを受信した瞬間から設定したsample数だけ過去のデータを取得する

- Ethernetケーブル(ツイストペアケーブル)にてPCと接続

全体の動作の流れを説明する。ADCは常にアナログデジタル変換を行い、FPGAは高速シリアル通信によってADCデータを取得する。取得したADCデータはリングバッファに書き込まれるが、このリングバッファはchannelごと 4000 sample分のデータを保持でき、古いデータから上書きされていく。つまりリングバッファは4000 sample分過去のデータを保持し続ける。外部トリガーを受信したら、設定したsample数だけの過去のデータから1 event分のデータを決められたフォーマットに変換し、TCP通信によりPCに転送する。

REGISTER module

データ収集用ソフトウェアの開発には、DAQ-Middlewareというフレームワークを利用する。DAQ-Middlewareはネットワーク分散環境でデータ収集用ソフトウェアを容易に構築するためのソフトウェア・フレームワークである。

今回開発するDAQソフトウェアは10L小型液体アルゴンTPCでの宇宙線データ取得実験に向けたものであり、以下のような機能をもつ。

- Digital boardからTPC通信にて転送されてくるバイナリデータの読み出し

- 取得したデータのリアルタイムモニター

- 取得したデータにトリガー時間情報を付加する

- 取得したデータの保存(バイナリデータのまま)

以上のような仕様を実現するためにGatherer、Dispatcher、Monitor、Loggerの4つのDAQ-Componentを用意した。

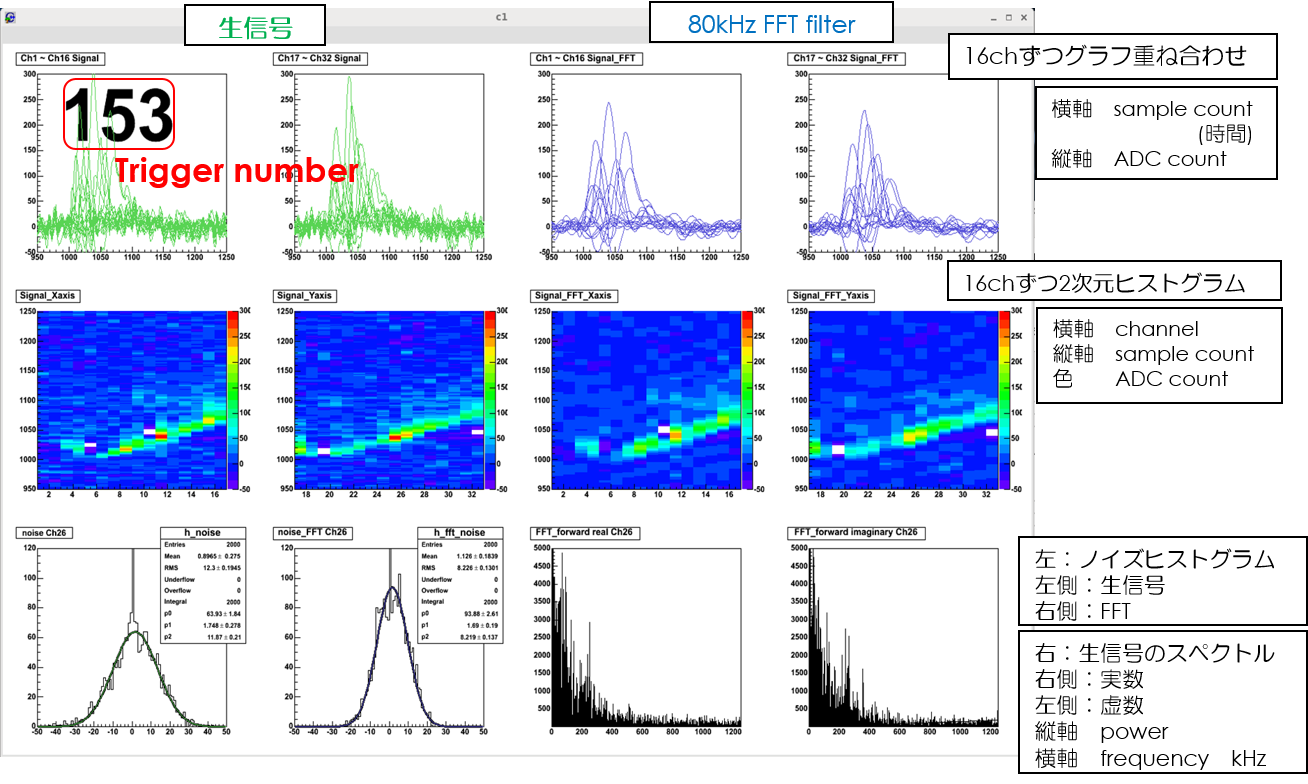

開発した読み出し回路、FPGAファームウェア、データ収集用ソフトウェアを使用し、10L液体アルゴンTPCにて宇宙線を取得した際のリアルタイムモニターの図を以下に載せる。

- プロジェクト関係者ページ(プロジェクトメンバーのみアクセス可)