PT7-汎用VMEマザーボード

メンバー

- 坂本宏(代表, ICEPP 東大)

- 大谷育生(ICEPP 東大)

- 加藤千曲(ICEPP 東大)

- 池野正弘(IPNS KEK)

- 佐々木修(IPNS KEK)

- 内田智久(IPNS KEK)

概要

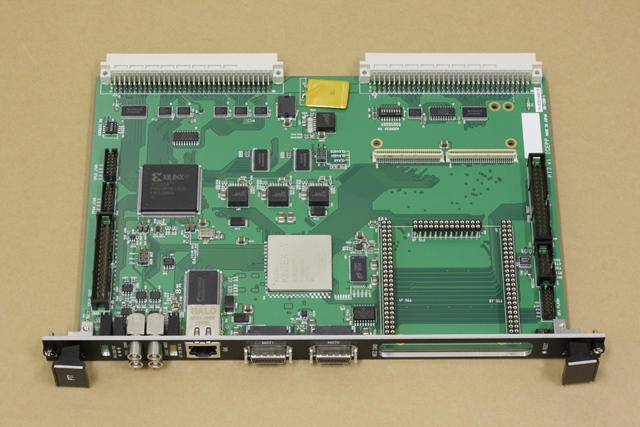

PT7 (ProtoType 7) ボードの開発。

ATLAS 検出器のデータ読み出し処理回路のアップグレード用プロトタイプ。

機能・特徴

- VME スレーヴモジュール (A32D32モード、6U サイズ)

- Kintex7 FPGA を搭載

- CPLD により VME 制御、FPGA のコンフィギュアが可能

- Mezzanine Card スロットを1つ搭載

- トリガー入力用に専用の Mezzanine Card スロットを1つ搭載

- DDR Infiniband 4x を2口搭載し、ギガビットトランシーバ GTX による高速通信が可能

- Gigabit Ethernet コネクタを搭載し、Ethernet による通信が可能

- RAMとしてDDR3-1333 (64M x 16bit = 1Gb) を搭載

公開予定リソース

- PT7 の仕様書

- PT7 ボードの回路図、基板レイアウト図

- CPLD の HDL デザイン

- FPGA の HDL デザイン

図・写真等

関連リンク

発表論文リスト