Hadron Universal Logic Module

概要

ハドロン実験では実験ごとにトリガー条件などの要求が異なり、汎用ロジックモジュールを用いた様々なトリガーが構築され使用されている。

現在そのためにはTULと呼ばれる過去に開発されたモジュールが使用されているが、現在様々な問題を抱えており新しいモジュールの開発が待たれている。そこで、Kintex7にSiTCPを搭載した新型汎用ロジックモジュールを開発する。

現在そのためにはTULと呼ばれる過去に開発されたモジュールが使用されているが、現在様々な問題を抱えており新しいモジュールの開発が待たれている。そこで、Kintex7にSiTCPを搭載した新型汎用ロジックモジュールを開発する。

メンバー

- 本多良太郎(代表:KEK 素核研、准教授)

- 三輪浩司(東北大、助教)

- 細見 健二(JAEA、博士研究員)

- 池野正弘(KEK 専任技師)

- 内田智久(KEK 准教授)

機能・特徴

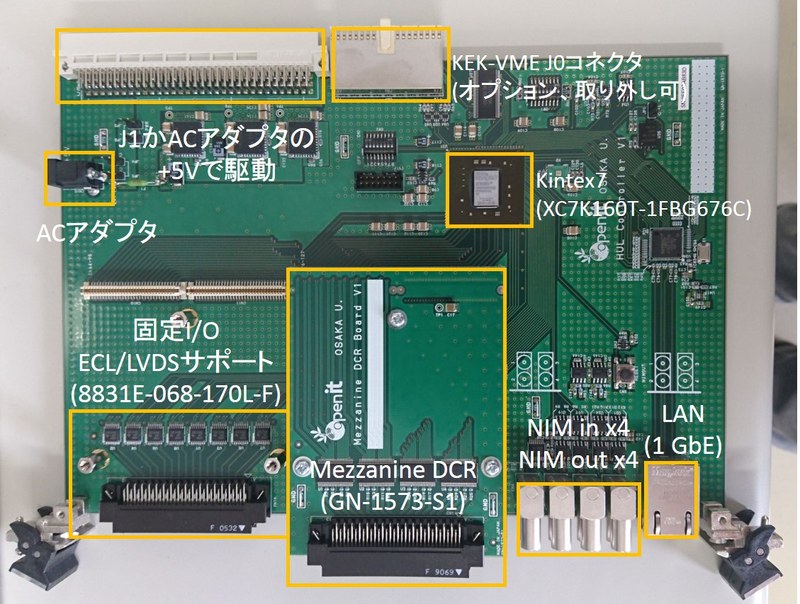

Kintex7を搭載し、RJ45を実装してGbE SiTCPをサポートする。

フロントパネルに64ch分の入力もち、更に拡張ボードを2枚さす事が可能で、最大128ch入力を受け付ける。

入力可能信号規格はLVDS/ECLを最低限サポートするものとする。

基盤はVME 6U規格とする。パワーはJ1から+5Vを給電し、ACアダプタでも動作するようにする。VMEバスによる会話はサポートしない。

FPGA回路の変更で様々な用途に使えるようにする。マトリックストリガーの構築やMHTDCやスケーラとしての動作を予定している。

フロントパネルに64ch分の入力もち、更に拡張ボードを2枚さす事が可能で、最大128ch入力を受け付ける。

入力可能信号規格はLVDS/ECLを最低限サポートするものとする。

基盤はVME 6U規格とする。パワーはJ1から+5Vを給電し、ACアダプタでも動作するようにする。VMEバスによる会話はサポートしない。

FPGA回路の変更で様々な用途に使えるようにする。マトリックストリガーの構築やMHTDCやスケーラとしての動作を予定している。

公開リソース

リリースパッケージ

FPGAファームウェアやソフトウェア、ユーザーガイドが含まれたパッケージです。

このパッケージに含まれるものが常に最新版になります。

このパッケージに含まれるものが常に最新版になります。

これまで公開していなかったファームウェアのソースコードと各回路の回路図はHULのユーザー限定でGitlab上で公開することにしました。

Gitlabリポジトリへのアクセス権が欲しい方は本多に連絡をお願いします。

- Zipfile (2023.08.19 PDF版UGを更新)

- HULユーザーガイド, PDF版 (2023.08.19更新)

- HUL User Guide (English) , PDF (Updated 2023.08.19)

ハードウェア

Open-Itメンバーのみ公開のアイテムについては、属性がmemberになっています。

本プロジェクトの開発メンバー以外で入手したい場合は本多までご連絡ください。

Hadron Universal Logic (HUL) controller (親基板) (GN-1573-1)

HUL Mezzanine cards (子基板)のリスト

1. Drift Chamber Reciever (DCR) v1 (GN-1573-S1)

1. Drift Chamber Reciever (DCR) v1 (GN-1573-S1)

LVDS (もしくは相当のcommon mode電圧の差動信号)を受け付ける子基板。

基本的にK1.8で使われているASD (gna200)を受けることを想定している。

- 仕様書 (ユーザーガイドを参照してください。)

- 回路図 (Opent-Itメンバーのみ公開とします。)

2. Drift Chamber Reciever (DCR) v2 (GN-1626-1)

DCRはLVDSしか受けれないため、ECLも受けれるように拡張したメザニン。

一度LVCMOSへ変換するためDCR v1よりも多少割高。

- 仕様書 (ユーザーガイドを参照してください。)

- 回路図 (本多へ連絡をください。Open-Itメンバーのみ公開とします。)

3. Receiver Module (RM) (GN-1627-1)

K1.8で使われているMTM-RMシステムのトリガー配布システムの、レシーバーモジュール。

- 仕様書 (ユーザーガイドを参照してください。)

- 回路図 (本多へ連絡をください。Open-Itメンバーのみ公開とします。)

4. Differential signal transmitter LVDS (GN-1724-1)

HULのFPGAから信号をLVDS形式で出力するためのメザニンカードです。

- 仕様書 (ユーザーガイドを参照してください。)

- 回路図 (本多へ連絡をください。Open-Itメンバーのみ公開とします。)

5. HR-TDC (GN-1644-1)

20 psの時間分解能を達成するHigh-resolution Multi-hit TDCです。

- 仕様書 (ユーザーガイドを参照してください。)

- 回路図 (本多へ連絡をください。Open-Itメンバーのみ公開とします。)

6. Extended NIM I/O (Ex-NIM) (coming soon)

LEMOコネクタが16 ch分搭載された基板であり、ジャンパで入力か出力かをチャンネル毎に決めることが出来る。

ソフトウェア (FPGA firmware + コンピューターソフト)

三次元マトリックストリガー

J-PARC E07実験で使われたTOFxFBHxSCHの3次元コインシデンストリガー。DCR v1が2枚必要。

Receiver module (HUL_RM)

Mezzanine Receiver Moduleをマウントして、MTMからのトリガー情報を受け取りKEK-VME J0へその情報を流すためのファームウェア。

また、RMが受け取った情報をネットワークで転送するDAQモジュールとしても利用することができる。

- ファームウェアおよびソフトウェア (リリースパッケージに同梱)

Scaler (HUL_Scaler)

300 MHzサンプリングのスケーラモジュール。DCRv1かv2をマウントすることで最大128chのスケーラデータを取得可能。

スケーラデータはネットワーク転送される。

- ファームウェアおよびソフトウェア (リリースパッケージに同梱)

Multi-Hit TDC (HUL_MHTDC)

1bit = 0.83 ns精度のMulti-Hit TDC。14 us分のヒット情報をレコードできる。Leading/Trailing両エッジ対応。時間分解能はおよそ300ps。

DCRv1かv2をマウントすることで最大128ch分のヒット情報を記録できる。TDC情報はネットワーク転送される。

- ファームウェアおよびソフトウェア (リリースパッケージに同梱)

High-resolution Multi-Hit TDC (MZN_MHTDC)

Mezzanine HR-TDC上のFPGAで20 ps 高時間分解能を達成するFPGA HR-TDCを制御及び読み出すためのソフトウェア。

Mezzanine HR-TDC上のFPGAで20 ps 高時間分解能を達成するFPGA HR-TDCを制御及び読み出すためのソフトウェア。

Mezzanine HR-TDC1台で32chの時間測定を行い、leading/trailing両エッジに対応。HUL一台で64ch分のHR-TDCを提供する。

- ファームウェアおよびソフトウェア (リリースパッケージに同梱)

図・写真等

Mezzanineを1つ取り付けた上体のHUL controller

関連リンク

発表論文リスト

- JPS 2016年秋季大会 (21pSK-11) 本多良太郎 J-PARCハドロン実験のための汎用ロジック回路、Hadron Universal Logic moduleの開発